- Up to 532 user I/Os

- LVDS interfaces up to 840 Mbps transmitter (Tx), 875 Mbps Rx

- Support for DDR2 SDRAM interfaces up to 200 MHz

- Support for QDRII SRAM and DDR SDRAM up to 167 MHz

- Up to eight phase-locked loops (PLLs) per device

- Offered in commercial and industrial temperature grades

# **Device Resources**

Table 1–1 lists Cyclone IV E device resources.

Table 1-1. Resources for the Cyclone IV E Device Family

| Resources                       | EP4CE6 | EP4CE10 | EP4CE15 | EP4CE22 | EP4CE30 | EP4CE40 | EP4CE55 | EP4CE75 | EP4CE115 |

|---------------------------------|--------|---------|---------|---------|---------|---------|---------|---------|----------|

| Logic elements (LEs)            | 6,272  | 10,320  | 15,408  | 22,320  | 28,848  | 39,600  | 55,856  | 75,408  | 114,480  |

| Embedded memory (Kbits)         | 270    | 414     | 504     | 594     | 594     | 1,134   | 2,340   | 2,745   | 3,888    |

| Embedded 18 × 18<br>multipliers | 15     | 23      | 56      | 66      | 66      | 116     | 154     | 200     | 266      |

| General-purpose PLLs            | 2      | 2       | 4       | 4       | 4       | 4       | 4       | 4       | 4        |

| Global Clock Networks           | 10     | 10      | 20      | 20      | 20      | 20      | 20      | 20      | 20       |

| User I/O Banks                  | 8      | 8       | 8       | 8       | 8       | 8       | 8       | 8       | 8        |

| Maximum user I/O (1)            | 179    | 179     | 343     | 153     | 532     | 532     | 374     | 426     | 528      |

#### Note to Table 1-1:

<sup>(1)</sup> The user I/Os count from pin-out files includes all general purpose I/O, dedicated clock pins, and dual purpose configuration pins. Transceiver pins and dedicated configuration pins are not included in the pin count.

# **Package Matrix**

Table 1–3 lists Cyclone IV E device package offerings.

Table 1–3. Package Offerings for the Cyclone IV E Device Family (1), (2)

| Package    | E1-         | 44        | M1       | 164      | M2       | 256      | U2           | 56       | F2           | 56             | F3          | 24       | U4           | 84        | F4       | 84       | F7           | 780      |

|------------|-------------|-----------|----------|----------|----------|----------|--------------|----------|--------------|----------------|-------------|----------|--------------|-----------|----------|----------|--------------|----------|

| Size (mm)  | 22 >        | <b>22</b> | 8 :      | × 8      | 9 :      | k 9      | 14 >         | × 14     | 17 :         | <b>&lt; 17</b> | 19 2        | x 19     | 19 :         | · 19      | 23 :     | × 23     | 29 :         | × 29     |

| Pitch (mm) | 0.          | .5        | 0        | .5       | 0.       | .5       | 0.           | .8       | 1.           | .0             | 1.          | .0       | 0            | .8        | 1.       | .0       | 1            | .0       |

| Device     | User I/O    | (S) KINDS | User I/O | (s) SQAT | User I/O | (E) SQAT | User I/O     | (s) SOAT | User I/0     | (E) SQAT       | User I/O    | (s) SQAT | User I/O     | (S) KINDS | User I/O | (s) SOAT | User I/O     | LVDS (3) |

| EP4CE6     | <b>▲</b> 91 | 21        | _        | _        | _        | _        | <b>▲</b> 179 | 66       | <b>▲</b> 179 | 66             | _           | _        | _            | _         | _        | _        | _            | _        |

| EP4CE10    | 91          | 21        | _        | _        | _        | _        | 179          | 66       | 179          | 66             | _           | _        |              | _         | _        | _        | _            | _        |

| EP4CE15    | 81          | 18        | 89       | 21       | 165      | 53       | 165          | 53       | 165          | 53             | _           | _        | _            | — .       | ▲ 343    | 137      | _            | —        |

| EP4CE22    | <b>√</b> 79 | 17        | _        | _        | _        | _        | <b>▼</b> 153 | 52       | <b>▼</b> 153 | 52             | _           | _        | _            | _         | _        | _        | _            | _        |

| EP4CE30    | _           | _         | _        | _        | _        | _        | _            | _        | _            | _              | <b>1</b> 93 | 68       | _            | _         | 328      | 124      | <b>↑</b> 532 | 224      |

| EP4CE40    | _           |           | _        | _        | _        | _        | _            | _        | _            | _              | <b>1</b> 93 | 68       | <b>▲</b> 328 | 124       | 328      | 124      | 532          | 224      |

| EP4CE55    | _           | _         | _        | _        | _        | _        | _            | _        | _            | _              | _           | _        | 324          | 132       | 324      | 132      | 374          | 160      |

| EP4CE75    | _           | _         | _        | _        | _        | _        | _            | _        | _            | _              | _           | _        | 292          | 110       | 292      | 110      | 426          | 178      |

| EP4CE115   | _           |           | _        | _        | _        |          | _            | _        | _            |                | _           | _        |              |           | 280      | 103      | <b>√</b> 528 | 230      |

#### Notes to Table 1-3:

- (1) The E144 package has an exposed pad at the bottom of the package. This exposed pad is a ground pad that must be connected to the ground plane of your PCB. Use this exposed pad for electrical connectivity and not for thermal purposes.

- (2) Use the Pin Migration View window in Pin Planner of the Quartus II software to verify the pin migration compatibility when you perform device migration. For more information, refer to the I/O Management chapter in volume 2 of the Quartus II Handbook.

- (3) This includes both dedicated and emulated LVDS pairs. For more information, refer to the I/O Features in Cyclone IV Devices chapter.

# **Cyclone IV Device Family Speed Grades**

Table 1–5 lists the Cyclone IV GX devices speed grades.

Table 1-5. Speed Grades for the Cyclone IV GX Device Family

| Device    | F169           | F324           | F484           | F672           | F896       |

|-----------|----------------|----------------|----------------|----------------|------------|

| EP4CGX15  | C6, C7, C8, I7 | _              | _              | _              | _          |

| EP4CGX22  | C6, C7, C8, I7 | C6, C7, C8, I7 | _              | _              | _          |

| EP4CGX30  | C6, C7, C8, I7 | C6, C7, C8, I7 | C6, C7, C8, I7 | _              | _          |

| EP4CGX50  | _              | _              | C6, C7, C8, I7 | C6, C7, C8, I7 | _          |

| EP4CGX75  | _              | _              | C6, C7, C8, I7 | C6, C7, C8, I7 | _          |

| EP4CGX110 | _              | _              | C7, C8, I7     | C7, C8, I7     | C7, C8, I7 |

| EP4CGX150 | _              | _              | C7, C8, I7     | C7, C8, I7     | C7, C8, I7 |

Table 1–6 lists the Cyclone IV E devices speed grades.

Table 1–6. Speed Grades for the Cyclone IV E Device Family (1), (2)

| Device   | E144                                   | M164 | M256     | U256 | F256                                   | F324 | U484 | F484                                   | F780                            |

|----------|----------------------------------------|------|----------|------|----------------------------------------|------|------|----------------------------------------|---------------------------------|

| EP4CE6   | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _    | _                                      | _                               |

| EP4CE10  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _    | _                                      | _                               |

| EP4CE15  | C8L, C9L, I8L<br>C6, C7, C8, I7        | I7N  | C7N, I7N | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _    | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 |                                 |

| EP4CE22  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 |      | l        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    |      | 1                                      | 1                               |

| EP4CE30  |                                        |      | _        | _    | _                                      | A7N  | _    | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE40  |                                        |      | _        | _    | _                                      | A7N  | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE55  | _                                      |      | _        | _    | _                                      | _    | 17N  | C8L, C9L, I8L<br>C6, C7, C8, I7        | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE75  | _                                      | _    | _        | _    | _                                      | _    | 17N  | C8L, C9L, I8L<br>C6, C7, C8, I7        | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE115 | _                                      | _    | _        | _    | _                                      | _    | _    | C8L, C9L, I8L<br>C7, C8, I7            | C8L, C9L, I8L<br>C7, C8, I7     |

## Notes to Table 1-6:

<sup>(1)</sup> C8L, C9L, and I8L speed grades are applicable for the 1.0-V core voltage.

<sup>(2)</sup> C6, C7, C8, I7, and A7 speed grades are applicable for the 1.2-V core voltage.

Table 4–1 lists the number of embedded multipliers and the multiplier modes that can be implemented in each Cyclone IV device.

Table 4-1. Number of Embedded Multipliers in Cyclone IV Devices

| Device Family | Device    | Embedded<br>Multipliers | 9 × 9<br>Multipliers <sup>(1)</sup> | 18 × 18<br>Multipliers <sup>(1)</sup> |

|---------------|-----------|-------------------------|-------------------------------------|---------------------------------------|

|               | EP4CGX15  | 0                       | 0                                   | 0                                     |

|               | EP4CGX22  | 40                      | 80                                  | 40                                    |

|               | EP4CGX30  | 80                      | 160                                 | 80                                    |

| Cyclone IV GX | EP4CGX50  | 140                     | 280                                 | 140                                   |

|               | EP4CGX75  | 198                     | 396                                 | 198                                   |

|               | EP4CGX110 | 280                     | 560                                 | 280                                   |

|               | EP4CGX150 | 360                     | 720                                 | 360                                   |

|               | EP4CE6    | 15                      | 30                                  | 15                                    |

|               | EP4CE10   | 23                      | 46                                  | 23                                    |

|               | EP4CE15   | 56                      | 112                                 | 56                                    |

|               | EP4CE22   | 66                      | 132                                 | 66                                    |

| Cyclone IV E  | EP4CE30   | 66                      | 132                                 | 66                                    |

|               | EP4CE40   | 116                     | 232                                 | 116                                   |

|               | EP4CE55   | 154                     | 308                                 | 154                                   |

|               | EP4CE75   | 200                     | 400                                 | 200                                   |

|               | EP4CE115  | 266                     | 532                                 | 266                                   |

#### Note to Table 4-1:

In addition to the embedded multipliers in Cyclone IV devices, you can implement soft multipliers by using the M9K memory blocks as look-up tables (LUTs). The LUTs contain partial results from the multiplication of input data with coefficients that implement variable depth and width high-performance soft multipliers for low-cost, high-volume DSP applications. The availability of soft multipliers increases the number of available multipliers in the device.

- For more information about M9K memory blocks, refer to the Memory Blocks in Cyclone IV Devices chapter.

- For more information about soft multipliers, refer to AN 306: Implementing Multipliers in FPGA Devices.

# **Architecture**

Each embedded multiplier consists of the following elements:

- Multiplier stage

- Input and output registers

- Input and output interfaces

<sup>(1)</sup> These columns show the number of  $9 \times 9$  or  $18 \times 18$  multipliers for each device.

# 5. Clock Networks and PLLs in Cyclone IV Devices

CYIV-51005-2.4

This chapter describes the hierarchical clock networks and phase-locked loops (PLLs) with advanced features in the Cyclone<sup>®</sup> IV device family. It includes details about the ability to reconfigure the PLL counter clock frequency and phase shift in real time, allowing you to sweep PLL output frequencies and dynamically adjust the output clock phase shift.

The Quartus<sup>®</sup> II software enables the PLLs and their features without external devices.

This chapter contains the following sections:

- "Clock Networks" on page 5–1

- "PLLs in Cyclone IV Devices" on page 5–18

- "Cyclone IV PLL Hardware Overview" on page 5–20

- "Clock Feedback Modes" on page 5–23

- "Hardware Features" on page 5–26

- "Programmable Bandwidth" on page 5–32

- "Phase Shift Implementation" on page 5–32

- "PLL Cascading" on page 5–33

- "PLL Reconfiguration" on page 5–34

- "Spread-Spectrum Clocking" on page 5–41

- "PLL Specifications" on page 5–41

# **Clock Networks**

The Cyclone IV GX device provides up to 12 dedicated clock pins (CLK[15..4]) that can drive the global clocks (GCLKs). Cyclone IV GX devices support four dedicated clock pins on each side of the device except the left side. These clock pins can drive up to 30 GCLKs.

The Cyclone IV E device provides up to 15 dedicated clock pins (CLK[15..1]) that can drive up to 20 GCLKs. Cyclone IV E devices support three dedicated clock pins on the left side and four dedicated clock pins on the top, right, and bottom sides of the device except EP4CE6 and EP4CE10 devices. EP4CE6 and EP4CE10 devices only support three dedicated clock pins on the left side and four dedicated clock pins on the right side of the device.

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Table 5–3. GCLK Network Connections for Cyclone IV E Devices (1) (Part 3 of 3)

| GCLK Network Clock                      |   |   |   |          |          |   |          |   | GC | LK N | etwo     | rks      |          |          |          |          |          |          |          |          |

|-----------------------------------------|---|---|---|----------|----------|---|----------|---|----|------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Sources                                 | 0 | 1 | 2 | 3        | 4        | 5 | 6        | 7 | 8  | 9    | 10       | 11       | 12       | 13       | 14       | 15       | 16       | 17       | 18       | 19       |

| DPCLK2 (4)                              |   |   |   |          |          |   |          |   |    |      |          |          |          |          |          |          |          |          |          |          |

| CDPCLK1, Or<br>CDPCLK2 (2), (5)         | _ | _ | _ | <b>✓</b> | <b>✓</b> | _ | _        | _ | _  | _    | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        |

| DPCLK5 (4) DPCLK7 (2)                   | _ | _ | _ | _        | _        | ~ | _        | _ | _  | _    | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        |

| DPCLK4 (4) DPCLK6 (2)                   | _ | _ | _ | _        | _        | _ | <b>✓</b> | _ | _  | _    | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        |

| DPCLK6 (4) CDPCLK5, Or CDPCLK6 (2), (5) | _ | _ | _ | _        | _        | _ | _        | ✓ | _  | _    | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        |

| DPCLK3 (4) CDPCLK4, Or CDPCLK3 (2). (5) | _ | _ | _ | _        | _        | _ | _        | _ | ✓  | ✓    | _        | _        | _        | _        | _        | _        | _        | _        | _        |          |

| DPCLK8                                  | _ | _ | _ | _        | _        | _ | _        | _ | _  | _    | <b>✓</b> | _        | _        | _        | _        | _        | _        | _        | —        | _        |

| DPCLK11                                 | _ | _ | _ | _        | _        | _ | _        | _ | _  | _    | _        | <b>✓</b> | _        | _        | _        | _        | _        | _        | _        | _        |

| DPCLK9                                  | _ | _ | _ | _        | _        | _ | _        | _ | _  | _    | _        | _        | <b>✓</b> | _        | _        | _        | _        | _        | _        | _        |

| DPCLK10                                 | _ | _ | _ | _        | _        | _ | _        | _ | _  | _    | _        | _        | _        | <b>✓</b> | <b>✓</b> | _        | _        | _        | _        | _        |

| DPCLK5                                  | _ | _ | _ | _        | _        |   | _        |   | _  | _    | _        | _        | _        | _        | _        | <b>✓</b> |          |          | _        | _        |

| DPCLK2                                  |   |   | _ | _        | _        |   | _        |   | _  | _    | _        | _        | _        |          | _        | _        | <b>✓</b> |          | _        |          |

| DPCLK4                                  | _ | _ |   |          |          |   | _        |   |    | _    |          |          |          |          |          | _        |          | <b>✓</b> | _        |          |

| DPCLK3                                  |   | _ | _ | _        | _        |   | _        |   | _  | _    | _        | _        | _        |          | _        | _        | _        |          | <b>✓</b> | <b>✓</b> |

#### Notes to Table 5-3:

- (1) EP4CE6 and EP4CE10 devices only have GCLK networks 0 to 9.

- (2) These pins apply to all Cyclone IV E devices except EP4CE6 and EP4CE10 devices.

- (3) EP4CE6 and EP4CE10 devices only have PLL\_1 and PLL\_2.

- (4) This pin applies only to EP4CE6 and EP4CE10 devices.

- (5) Only one of the two CDPCLK pins can feed the clock control block. You can use the other pin as a regular I/O pin.

Chapter 5: Clock Networks and PLLs in Cyclone IV Devices Clock Networks

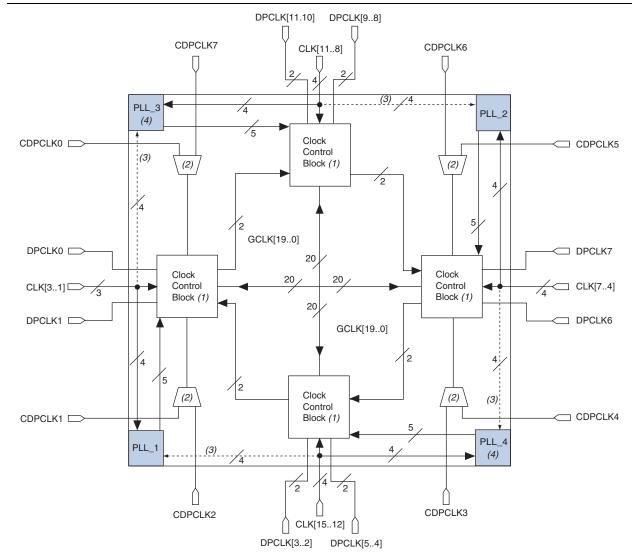

Figure 5-4. Clock Networks and Clock Control Block Locations in Cyclone IV E Devices

## Notes to Figure 5-4:

- (1) There are five clock control blocks on each side.

- (2) Only one of the corner CDPCLK pins in each corner can feed the clock control block at a time. You can use the other CDPCLK pins as general-purpose I/O (GPIO) pins.

- (3) Dedicated clock pins can feed into this PLL. However, these paths are not fully compensated.

- (4) PLL\_3 and PLL\_4 are not available in EP4CE6 and EP4CE10 devices.

The inputs to the clock control blocks on each side of the Cyclone IV GX device must be chosen from among the following clock sources:

- Four clock input pins

- Ten PLL counter outputs (five from each adjacent PLLs)

- Two, four, or six DPCLK pins from the top, bottom, and right sides of the device

- Five signals from internal logic

Each Cyclone IV I/O bank has a VREF bus to accommodate voltage-referenced I/O standards. Each VREF pin is the reference source for its  $V_{REF}$  group. If you use a  $V_{REF}$  group for voltage-referenced I/O standards, connect the VREF pin for that group to the appropriate voltage level. If you do not use all the V<sub>REF</sub> groups in the I/O bank for voltage-referenced I/O standards, you can use the VREF pin in the unused voltage-referenced groups as regular I/O pins. For example, if you have SSTL-2 Class I input pins in I/O bank 1 and they are all placed in the VREFB1N[0] group, VREFB1N[0] must be powered with 1.25 V, and the remaining VREFB1N [1..3] pins (if available) are used as I/O pins. If multiple  $V_{REF}$  groups are used in the same I/O bank, the VREF pins must all be powered by the same voltage level because the VREF pins are shorted together within the same I/O bank.

- When VREF pins are used as regular I/Os, they have higher pin capacitance than regular user I/O pins. This has an impact on the timing if the pins are used as inputs and outputs.

- For more information about VREF pin capacitance, refer to the pin capacitance section in the Cyclone IV Device Datasheet chapter.

- For information about how to identify  $V_{RFF}$  groups, refer to the Cyclone IV **Device Pin-Out** files or the **Quartus II Pin Planner** tool.

Table 6–4 and Table 6–5 summarize the number of VREF pins in each I/O bank for the Cyclone IV device family.

Table 6–4. Number of VREF Pins Per I/O Bank for Cyclone IV E Devices (Part 1 of 2)

| Device             |          | EP4CE6   |          |          | EP4CE10  |          |          |          | ED40     | 1        |          |          |          | EP4CE22  |          |          | EP4CE30  |          |          | 27       | EP4CE40  |          |          | EP4CE55  |          |          | EP4CE75  |          | AP E44   | EF46E115 |

|--------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| I/O<br>Bank<br>(1) | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 164-MBGA | 256-MBGA | 256-UBGA | 256-FBGA | 484-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 324-FBGA | 484-FBGA | 780-FBGA | 324-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-FBGA | 780-FBGA |

| 1                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 2                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 3                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 4                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 5                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 6                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 7                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

Chapter 6: I/O Features in Cyclone IV Devices 1/0 Banks

Table 6-4. Number of VREF Pins Per I/O Bank for Cyclone IV E Devices (Part 2 of 2)

| Device             |          | EP4CE6   |          |          | EP4CE10  |          |          |          | EDAFE1E  | 101      |          |          |          | EP4CE22  |          |          | EP4CE30  |          |          | EDACEAD  | 740.04   |          |          | EP4CE55  |          |          | EP4CE75  |          | DAFE     | Er46E113 |

|--------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| I/O<br>Bank<br>(1) | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 164-MBGA | 256-MBGA | 256-UBGA | 256-FBGA | 484-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 324-FBGA | 484-FBGA | 780-FBGA | 324-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-FBGA | 780-FBGA |

| 8                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

#### Note to Table 6-4:

(1) User I/O pins are used as inputs or outputs; clock input pins are used as inputs only; clock output pins are used as output only.

Table 6-5. Number of VREF Pins Per I/O Bank for Cyclone IV GX Devices

| Device   | 4CGX15   | 4CG      | X22      |          | 4CGX30   |          | 4CG      | X50      | 4CG      | X75      |          | 4CGX110  |          |          | 4CGX150  |          |

|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| I/O Bank | 169-FBGA | 169-FBGA | 324-FBGA | 169-FBGA | 324-FBGA | 484-FBGA | 484-FBGA | 672-FBGA | 484-FBGA | 672-FBGA | 484-FBGA | 672-FBGA | 896-FBGA | 484-FBGA | 672-FBGA | 896-FBGA |

| 3        | 1        | 1        | 1        |          | 1        | 3        | ;        | 3        | 3        | 3        |          | 3        |          |          | 3        |          |

| 4        | 1        | 1        | 1        |          | 1        | 3        | ;        | 3        | 3        | 3        |          | 3        |          |          | 3        |          |

| 5        | 1        | 1        | 1        |          | 1        | 3        | ;        | 3        | 3        | 3        |          | 3        |          |          | 3        |          |

| 6        | 1        | 1        | 1        |          | 1        | 3        | ;        | 3        | 3        | 3        |          | 3        |          |          | 3        |          |

| 7        | 1        | 1        | 1        |          | 1        | 3        | ;        | 3        | 3        | 3        |          | 3        |          |          | 3        |          |

| 8 (2)    | 1        | 1        |          |          | 1        | 3        | ;        | 3        | 3        | 3        |          | 3        |          |          | 3        |          |

#### Notes to Table 6-5:

- (1) User I/O pins are used as inputs or outputs; clock input pins are used as inputs only; clock output pins are used as output only.

- (2) Bank 9 does not have VREF pin. If input pins with VREF I/O standards are used in bank 9 during user mode, it shares the VREF pin in bank 8.

Each Cyclone IV I/O bank has its own VCCIO pins. Each I/O bank can support only one  $V_{CCIO}$  setting from among 1.2, 1.5, 1.8, 2.5, 3.0, or 3.3 V. Any number of supported single-ended or differential standards can be simultaneously supported in a single I/O bank, as long as they use the same  $V_{CCIO}$  levels for input and output pins.

Table 6–8 and Table 6–9 summarize the total number of supported row and column differential channels in the Cyclone IV device family.

Table 6-8. Cyclone IV E I/O and Differential Channel Count

| Device                                       |          | EP4CE6   |          |          | EP4CE10  |          |          |          | FDACE1E  | 6146613  |          |          |          | EP4CE22  |          |          | EP4CE30  |          |          | 07.07.0  | E146640  |          |          | EP4CE55  |          |          | EP4CE75  |          | 27730763 | Er40EII3 |

|----------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Numbers of Differential<br>Channels (1), (2) | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 164-MBGA | 256-MBGA | 256-UBGA | 256-FBGA | 484-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 324-FBGA | 484-FBGA | 780-FBGA | 324-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-FBGA | 780-FBGA |

| User<br>I/O <sup>(3)</sup>                   | 91       | 179      | 179      | 91       | 179      | 179      | 81       | 89       | 165      | 165      | 165      | 343      | 79       | 153      | 153      | 193      | 328      | 532      | 193      | 328      | 328      | 532      | 324      | 324      | 374      | 292      | 292      | 426      | 280      | 528      |

| User I/O<br>Banks                            | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        |

| LVDS (4), (<br>6)                            | 8        | 23       | 23       | 8        | 23       | 23       | 6        | 8        | 21       | 21       | 21       | 67       | 7        | 20       | 20       | 30       | 60       | 112      | 30       | 60       | 60       | 112      | 62       | 62       | 70       | 54       | 54       | 79       | 50       | 103      |

| Emulated<br>LVDS (5), (<br>6)                | 13       | 43       | 43       | 13       | 43       | 43       | 12       | 13       | 32       | 32       | 32       | 70       | 10       | 32       | 32       | 38       | 64       | 112      | 38       | 64       | 64       | 112      | 70       | 70       | 90       | 56       | 56       | 99       | 53       | 127      |

#### Notes to Table 6-8:

- (1) User I/O pins are used as inputs or outputs; clock input pins are used as inputs only; clock output pins are used as output only.

- (2) For differential pad placement guidelines, refer to "Pad Placement" on page 6-23.

- (3) The I/O pin count includes all GPIOs, dedicated clock pins, and dual-purpose configuration pins. Dedicated configuration pins are not included in the pin count.

- (4) The true LVDS count includes all LVDS I/O pairs, differential clock input and clock output pins in row I/O banks 1, 2, 5, and 6.

- (5) The emulated LVDS count includes all LVDS I/O pairs, differential clock input and clock output pins in column I/O banks 3, 4, 7, and 8.

- (6) LVDS input and output buffers are sharing the same p and n pins. One LVDS I/O channel can only be either transmitter or receiver at a time.

Chapter 6: I/O Features in Cyclone IV Devices High-Speed I/O Interface

Table 7–2 lists the number of DQS or DQ groups supported on each side of the Cyclone IV E device.

Table 7-2. Cyclone IV E Device DQS and DQ Bus Mode Support for Each Side of the Device (Part 1 of 3)

| Device   | Package        | Side            | Number<br>×8<br>Groups | Number<br>×9<br>Groups | Number<br>×16<br>Groups | Number<br>×18<br>Groups | Number<br>×32<br>Groups | Number<br>×36<br>Groups |

|----------|----------------|-----------------|------------------------|------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

|          |                | Left            | 0                      | 0                      | 0                       | 0                       | _                       | _                       |

|          | 144-pin EQFP   | Right           | 0                      | 0                      | 0                       | 0                       | _                       | _                       |

|          | 144-pili EQFF  | Bottom (1), (3) | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|          |                | Top (1), (4)    | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|          |                | Left (1)        | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

| EP4CE6   | 256-pin UBGA   | Right (2)       | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

| EP4CE10  | 230-pill obak  | Bottom          | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                | Тор             | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                | Left (1)        | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

|          | 256-pin FBGA   | Right (2)       | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

|          | 250-piii i buA | Bottom          | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                | Тор             | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                | Left            | 0                      | 0                      | 0                       | 0                       |                         | _                       |

|          | 144-pin EQFP   | Right           | 0                      | 0                      | 0                       | 0                       | _                       | _                       |

|          | 144-piii EQI1  | Bottom (1), (3) | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|          |                | Top (1), (4)    | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|          |                | Left            | 0                      | 0                      | 0                       | 0                       | _                       | _                       |

|          | 164-pin MBGA   | Right           | 0                      | 0                      | 0                       | 0                       | _                       | _                       |

|          | 104 piii MBart | Bottom (1), (3) | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|          |                | Top (1), (4)    | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|          |                | Left            | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

|          | 256-pin MBGA   | Right           | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

|          | 200 piii MBart | Bottom (1), (3) | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

| EP4CE15  |                | Top (1), (4)    | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

| LI TOLIO |                | Left (1)        | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

|          | 256-pin UBGA   | Right (2)       | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

|          | 200 pili obak  | Bottom          | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                | Тор             | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                | Left (1)        | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

|          | 256-pin FBGA   | Right (2)       | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

|          | 200 piii i buA | Bottom          | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                | Тор             | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                | Left            | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|          | 484-pin FBGA   | Right           | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|          | 704 PILLIDUM   | Bottom          | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|          |                | Тор             | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

## Power-On Reset (POR) Circuit

The POR circuit keeps the device in reset state until the power supply voltage levels have stabilized during device power up. After device power up, the device does not release nSTATUS until  $V_{CCINT}$ ,  $V_{CCA}$ , and  $V_{CCIO}$  (for I/O banks in which the configuration and JTAG pins reside) are above the POR trip point of the device. V<sub>CCINT</sub> and V<sub>CCA</sub> are monitored for brown-out conditions after device power up.

V<sub>CCA</sub> is the analog power to the phase-locked loop (PLL).

In some applications, it is necessary for a device to wake up very quickly to begin operation. Cyclone IV devices offer the fast POR time option to support fast wake-up time applications. The fast POR time option has stricter power-up requirements when compared with the standard POR time option. You can select either the fast option or the standard POR option with the MSEL pin settings.

- If your system exceeds the fast or standard POR time, you must hold nCONFIG low until all the power supplies are stable.

- For more information about the POR specifications, refer to the Cyclone IV Device Datasheet.

- For more information about the wake-up time and POR circuit, refer to the *Power* Requirements for Cyclone IV Devices chapter.

## **Configuration File Size**

Table 8–2 lists the approximate uncompressed configuration file sizes for Cyclone IV devices. To calculate the amount of storage space required for multiple device configurations, add the file size of each device together.

Table 8–2. Uncompressed Raw Binary File (.rbf) Sizes for Cyclone IV Devices (Part 1 of 2)

|              | Device   | Data Size (bits) |

|--------------|----------|------------------|

|              | EP4CE6   | 2,944,088        |

|              | EP4CE10  | 2,944,088        |

|              | EP4CE15  | 4,086,848        |

|              | EP4CE22  | 5,748,552        |

| Cyclone IV E | EP4CE30  | 9,534,304        |

|              | EP4CE40  | 9,534,304        |

|              | EP4CE55  | 14,889,560       |

|              | EP4CE75  | 19,965,752       |

|              | EP4CE115 | 28,571,696       |

You can use the Quartus II software with the APU and the appropriate configuration device programming adapter to program serial configuration devices. All serial configuration devices are offered in an 8- or 16-pin small outline integrated circuit (SOIC) package.

In production environments, serial configuration devices are programmed using multiple methods. Altera programming hardware or other third-party programming hardware is used to program blank serial configuration devices before they are mounted onto PCBs. Alternatively, you can use an on-board microprocessor to program the serial configuration device in-system by porting the reference C-based SRunner software driver provided by Altera.

A serial configuration device is programmed in-system by an external microprocessor with the SRunner software driver. The SRunner software driver is a software driver developed for embedded serial configuration device programming, which is easily customized to fit in different embedded systems. The SRunner software driver is able to read a Raw Programming Data (.rpd) file and write to serial configuration devices. The serial configuration device programming time, using the SRunner software driver, is comparable to the programming time with the Quartus II software.

For more information about the SRunner software driver, refer to *AN 418: SRunner: An Embedded Solution for Serial Configuration Device Programming* and the source code at the Altera website.

# **AP Configuration (Supported Flash Memories)**

The AP configuration scheme is only supported in Cyclone IV E devices. In the AP configuration scheme, Cyclone IV E devices are configured using commodity 16-bit parallel flash memory. These external non-volatile configuration devices are industry standard microprocessor flash memories. The flash memories provide a fast interface to access configuration data. The speed up in configuration time is mainly due to the 16-bit wide parallel data bus, which is used to retrieve data from the flash memory.

Some of the smaller Cyclone IV E devices or package options do not support the AP configuration scheme. Table 8–9 lists the supported AP configuration scheme for each Cyclone IV E devices.

Table 8-9. Supported AP Configuration Scheme for Cyclone IV E Devices

| Dovice   |      |      | Package Options |      |      |      |      |          |          |

|----------|------|------|-----------------|------|------|------|------|----------|----------|

| Device   | E144 | M164 | M256            | U256 | F256 | F324 | U484 | F484     | F780     |

| EP4CE6   | _    | _    | _               | _    | _    | _    | _    | _        | _        |

| EP4CE10  | _    | _    | _               | _    | _    | _    | _    | _        | _        |

| EP4CE15  | _    | _    | _               | _    | _    | _    | _    | ✓        | _        |

| EP4CE22  | _    | _    | _               | _    | _    | _    | _    | _        | _        |

| EP4CE30  | _    | _    | _               | _    | _    | ✓    | _    | <b>✓</b> | ✓        |

| EP4CE40  | _    | _    | _               | _    | _    | ✓    | ✓    | <b>✓</b> | ✓        |

| EP4CE55  | _    | _    | _               | _    | _    | _    | ✓    | ✓        | ✓        |

| EP4CE75  | _    | _    | _               | _    | _    | _    | ✓    | ✓        | <b>✓</b> |

| EP4CE115 | _    | _    | _               | _    | _    | _    | _    | <b>✓</b> | ✓        |

Table 9–6 lists the estimated time for each CRC calculation with minimum and maximum clock frequencies for Cyclone IV devices.

Table 9-6. CRC Calculation Time

| Device        |              | Minimum Time (ms) <sup>(1)</sup> | Maximum Time (s) (2) |

|---------------|--------------|----------------------------------|----------------------|

|               | EP4CE6 (3)   | 5                                | 2.29                 |

|               | EP4CE10 (3)  | 5                                | 2.29                 |

|               | EP4CE15 (3)  | 7                                | 3.17                 |

|               | EP4CE22 (3)  | 9                                | 4.51                 |

| Cyclone IV E  | EP4CE30 (3)  | 15                               | 7.48                 |

|               | EP4CE40 (3)  | 15                               | 7.48                 |

|               | EP4CE55 (3)  | 23                               | 11.77                |

|               | EP4CE75 (3)  | 31                               | 15.81                |

|               | EP4CE115 (3) | 45                               | 22.67                |

|               | EP4CGX15     | 6                                | 2.93                 |

|               | EP4CGX22     | 12                               | 5.95                 |

|               | FD4CCV20     | 12                               | 5.95                 |

| Cyclene IV CV | EP4CGX30     | 34 (4)                           | 17.34 <sup>(4)</sup> |

| Cyclone IV GX | EP4CGX50     | 34                               | 17.34                |

|               | EP4CGX75     | 34                               | 17.34                |

|               | EP4CGX110    | 62                               | 31.27                |

|               | EP4CGX150    | 62                               | 31.27                |

#### Notes to Table 9-6:

- (1) The minimum time corresponds to the maximum error detection clock frequency and may vary with different processes, voltages, and temperatures (PVT).

- (2) The maximum time corresponds to the minimum error detection clock frequency and may vary with different PVT.

- (3) Only applicable for device with 1.2-V core voltage

- (4) Only applicable for the F484 device package.

# **Software Support**

Enabling the CRC error detection feature in the Quartus II software generates the CRC\_ERROR output to the optional dual purpose CRC\_ERROR pin.

To enable the error detection feature using CRC, perform the following steps:

- 1. Open the Quartus II software and load a project using Cyclone IV devices.

- 2. On the Assignments menu, click **Settings**. The **Settings** dialog box appears.

- 3. In the Category list, select **Device**. The **Device** page appears.

- 4. Click **Device and Pin Options**. The **Device and Pin Options** dialog box appears as shown in Figure 9–2.

- 5. In the **Device and Pin Options** dialog box, click the **Error Detection CRC** tab.

- 6. Turn on Enable error detection CRC.

- 7. In the **Divide error check frequency by** box, enter a valid divisor as documented in Table 9–5 on page 9–5.

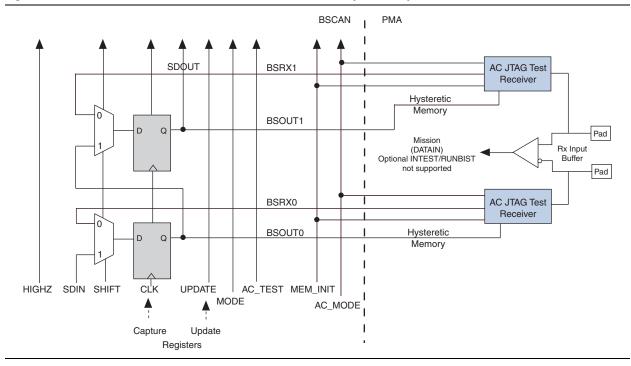

Figure 10–2 shows the Cyclone IV GX HSSI receiver BSC.

Figure 10–2. HSSI Receiver BSC with IEEE Std. 1149.6 BST Circuitry for the Cyclone IV GX Devices

For more information about Cyclone IV devices user I/O boundary-scan cells, refer to the *IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone III Devices* chapter.

# **BST Operation Control**

Table 10–1 lists the boundary-scan register length for Cyclone IV devices.

Table 10-1. Boundary-Scan Register Length for Cyclone IV Devices (Part 1 of 2)

| Device                  | Boundary-Scan Register Length |

|-------------------------|-------------------------------|

| EP4CE6                  | 603                           |

| EP4CE10                 | 603                           |

| EP4CE15                 | 1080                          |

| EP4CE22                 | 732                           |

| EP4CE30                 | 1632                          |

| EP4CE40                 | 1632                          |

| EP4CE55                 | 1164                          |

| EP4CE75                 | 1314                          |

| EP4CE115                | 1620                          |

| EP4CGX15                | 260                           |

| EP4CGX22                | 494                           |

| EP4CGX30 <sup>(1)</sup> | 494                           |

| EP4CGX50                | 1006                          |

| Table 10-1. Boundar | v-Scan Register Len | gth for Cyclone IV Devices | (Part 2 of 2) |

|---------------------|---------------------|----------------------------|---------------|

|                     |                     |                            |               |

| Device    | Boundary-Scan Register Length |

|-----------|-------------------------------|

| EP4CGX75  | 1006                          |

| EP4CGX110 | 1495                          |

| EP4CGX150 | 1495                          |

### Note to Table 10-1:

(1) For the F484 package of the EP4CGX30 device, the boundary-scan register length is 1006.

Table 10–2 lists the IDCODE information for Cyclone IV devices.

Table 10–2. IDCODE Information for 32-Bit Cyclone IV Devices

| ·            |                     | IDCODE (32 Bits) (1)     |                                    |                               |  |  |  |  |  |

|--------------|---------------------|--------------------------|------------------------------------|-------------------------------|--|--|--|--|--|

| Device       | Version<br>(4 Bits) | Part Number<br>(16 Bits) | Manufacturer Identity<br>(11 Bits) | LSB<br>(1 Bit) <sup>(2)</sup> |  |  |  |  |  |

| EP4CE6       | 0000                | 0010 0000 1111 0001      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CE10      | 0000                | 0010 0000 1111 0001      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CE15      | 0000                | 0010 0000 1111 0010      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CE22      | 0000                | 0010 0000 1111 0011      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CE30      | 0000                | 0010 0000 1111 0100      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CE40      | 0000                | 0010 0000 1111 0100      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CE55      | 0000                | 0010 0000 1111 0101      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CE75      | 0000                | 0010 0000 1111 0110      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CE115     | 0000                | 0010 0000 1111 0111      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CGX15     | 0000                | 0010 1000 0000 0001      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CGX22     | 0000                | 0010 1000 0001 0010      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CGX30 (3) | 0000                | 0010 1000 0000 0010      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CGX30 (4) | 0000                | 0010 1000 0010 0011      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CGX50     | 0000                | 0010 1000 0001 0011      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CGX75     | 0000                | 0010 1000 0000 0011      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CGX110    | 0000                | 0010 1000 0001 0100      | 000 0110 1110                      | 1                             |  |  |  |  |  |

| EP4CGX150    | 0000                | 0010 1000 0000 0100      | 000 0110 1110                      | 1                             |  |  |  |  |  |

#### Notes to Table 10-2:

- (1) The MSB is on the left.

- (2) The IDCODE LSB is always 1.

- (3) The IDCODE is applicable for all packages except for the F484 package.

- (4) The  ${\tt IDCODE}$  is applicable for the F484 package only.

IEEE Std.1149.6 mandates the addition of two new instructions: EXTEST\_PULSE and EXTEST\_TRAIN. These two instructions enable edge-detecting behavior on the signal path containing the AC pins.

Table 1–23 lists the Cyclone IV GX transceiver block AC specifications.

Table 1–23. Transceiver Block AC Specification for Cyclone IV GX Devices (1), (2)

| Symbol/                                                                 | Conditions                                     | C6     |             |        | C7, I7 |       |        | C8  |     |       | 11!4 |

|-------------------------------------------------------------------------|------------------------------------------------|--------|-------------|--------|--------|-------|--------|-----|-----|-------|------|

| Description                                                             | Conditions                                     | Min    | Min Typ Max |        | Min    | Тур   | Max    | Min | Тур | Max   | Unit |

| PCIe Transmit Jitter Gene                                               | PCIe Transmit Jitter Generation <sup>(3)</sup> |        |             |        |        |       |        |     |     |       |      |

| Total jitter at 2.5 Gbps<br>(Gen1)                                      | Compliance pattern                             | _      | _           | 0.25   | _      | _     | 0.25   | _   | _   | 0.25  | UI   |

| PCIe Receiver Jitter Tolei                                              | rance <sup>(3)</sup>                           |        |             |        |        |       |        |     |     |       |      |

| Total jitter at 2.5 Gbps<br>(Gen1)                                      | Compliance pattern                             | > 0.6  |             | > 0.6  |        | > 0.6 |        | UI  |     |       |      |

| GIGE Transmit Jitter Gene                                               | ration <sup>(4)</sup>                          |        |             |        |        |       |        |     |     |       |      |

| Deterministic jitter<br>(peak-to-peak)                                  | Pattern = CRPAT                                | _      | _           | 0.14   | _      | _     | 0.14   | _   | _   | 0.14  | UI   |

| Total jitter (peak-to-peak)                                             | Pattern = CRPAT                                | _      | _           | 0.279  | _      | _     | 0.279  | _   |     | 0.279 | UI   |

| GIGE Receiver Jitter Tole                                               | rance <sup>(4)</sup>                           |        |             |        |        |       |        |     |     |       |      |

| Deterministic jitter<br>tolerance (peak-to-peak)                        | Pattern = CJPAT                                | > 0.4  |             | > 0.4  |        | > 0.4 |        |     | UI  |       |      |

| Combined deterministic<br>and random jitter<br>tolerance (peak-to-peak) | Pattern = CJPAT                                | > 0.66 |             | > 0.66 |        |       | > 0.66 |     |     | UI    |      |

#### Notes to Table 1-23:

- (1) Dedicated refclk pins were used to drive the input reference clocks.

- (2) The jitter numbers specified are valid for the stated conditions only.

- (3) The jitter numbers for PIPE are compliant to the PCle Base Specification 2.0.

- (4) The jitter numbers for GIGE are compliant to the IEEE802.3-2002 Specification.

# **Core Performance Specifications**

The following sections describe the clock tree specifications, PLLs, embedded multiplier, memory block, and configuration specifications for Cyclone IV Devices.

# **Clock Tree Specifications**

Table 1–24 lists the clock tree specifications for Cyclone IV devices.

Table 1–24. Clock Tree Performance for Cyclone IV Devices (Part 1 of 2)

| Dovice  |       |       |     | Performance |         |       |                    |     |      |

|---------|-------|-------|-----|-------------|---------|-------|--------------------|-----|------|

| Device  | C6 C7 |       | C8  | C8L (1)     | C9L (1) | 17    | I8L <sup>(1)</sup> | A7  | Unit |

| EP4CE6  | 500   | 437.5 | 402 | 362         | 265     | 437.5 | 362                | 402 | MHz  |

| EP4CE10 | 500   | 437.5 | 402 | 362         | 265     | 437.5 | 362                | 402 | MHz  |

| EP4CE15 | 500   | 437.5 | 402 | 362         | 265     | 437.5 | 362                | 402 | MHz  |

| EP4CE22 | 500   | 437.5 | 402 | 362         | 265     | 437.5 | 362                | 402 | MHz  |

| EP4CE30 | 500   | 437.5 | 402 | 362         | 265     | 437.5 | 362                | 402 | MHz  |

| EP4CE40 | 500   | 437.5 | 402 | 362         | 265     | 437.5 | 362                | 402 | MHz  |

# **Embedded Multiplier Specifications**

Table 1–26 lists the embedded multiplier specifications for Cyclone IV devices.

Table 1–26. Embedded Multiplier Specifications for Cyclone IV Devices

| Mode                   | Resources Used        |     |                           | Unit |     |     |     |

|------------------------|-----------------------|-----|---------------------------|------|-----|-----|-----|

| Mode                   | Number of Multipliers | C6  | C6 C7, I7, A7 C8 C8L, I8L |      |     |     |     |

| 9 × 9-bit multiplier   | 1                     | 340 | 300                       | 260  | 240 | 175 | MHz |

| 18 × 18-bit multiplier | 1                     | 287 | 250                       | 200  | 185 | 135 | MHz |

## **Memory Block Specifications**

Table 1–27 lists the M9K memory block specifications for Cyclone IV devices.

Table 1-27. Memory Block Performance Specifications for Cyclone IV Devices

|           |                                    | Resou | rces Used     |     |            |     |          |     |      |  |

|-----------|------------------------------------|-------|---------------|-----|------------|-----|----------|-----|------|--|

| Memory    | Mode                               | LEs   | M9K<br>Memory | C6  | C7, I7, A7 | C8  | C8L, I8L | C9L | Unit |  |

|           | FIFO 256 × 36                      | 47    | 1             | 315 | 274        | 238 | 200      | 157 | MHz  |  |

| MOV Plook | Single-port 256 × 36               | 0     | 1             | 315 | 274        | 238 | 200      | 157 | MHz  |  |

| M9K Block | Simple dual-port 256 × 36 CLK      | 0     | 1             | 315 | 274        | 238 | 200      | 157 | MHz  |  |

|           | True dual port 512 × 18 single CLK | 0     | 1             | 315 | 274        | 238 | 200      | 157 | MHz  |  |

# **Configuration and JTAG Specifications**

Table 1–28 lists the configuration mode specifications for Cyclone IV devices.

Table 1–28. Passive Configuration Mode Specifications for Cyclone IV Devices (1)

| Programming Mode                | V <sub>CCINT</sub> Voltage Level (V) | DCLK f <sub>max</sub> | Unit |

|---------------------------------|--------------------------------------|-----------------------|------|

| Passive Serial (PS)             | 1.0 <sup>(3)</sup>                   | 66                    | MHz  |

|                                 | 1.2                                  | 133                   | MHz  |

| Fast Passive Parallel (FPP) (2) | 1.0 <sup>(3)</sup>                   | 66                    | MHz  |

| Tast Fassive Falallel (FFF) 1-7 | 1.2 (4)                              | 100                   | MHz  |

#### Notes to Table 1-28:

- (1) For more information about PS and FPP configuration timing parameters, refer to the *Configuration and Remote System Upgrades in Cyclone IV Devices* chapter.

- (2) FPP configuration mode supports all Cyclone IV E devices (except for E144 package devices) and EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 only.

- (3)  $V_{CCINT} = 1.0 \text{ V}$  is only supported for Cyclone IV E 1.0 V core voltage devices.

- (4) Cyclone IV E devices support 1.2 V V<sub>CCINT</sub>. Cyclone IV E 1.2 V core voltage devices support 133 MHz DCLK f<sub>MAX</sub> for EP4CE6, EP4CE10, EP4CE15, EP4CE22, EP4CE30, and EP4CE40 only.