# NTE74181 Integrated Circuit TTL – Arithmetic Logic Unit/Function Generator

#### **Description:**

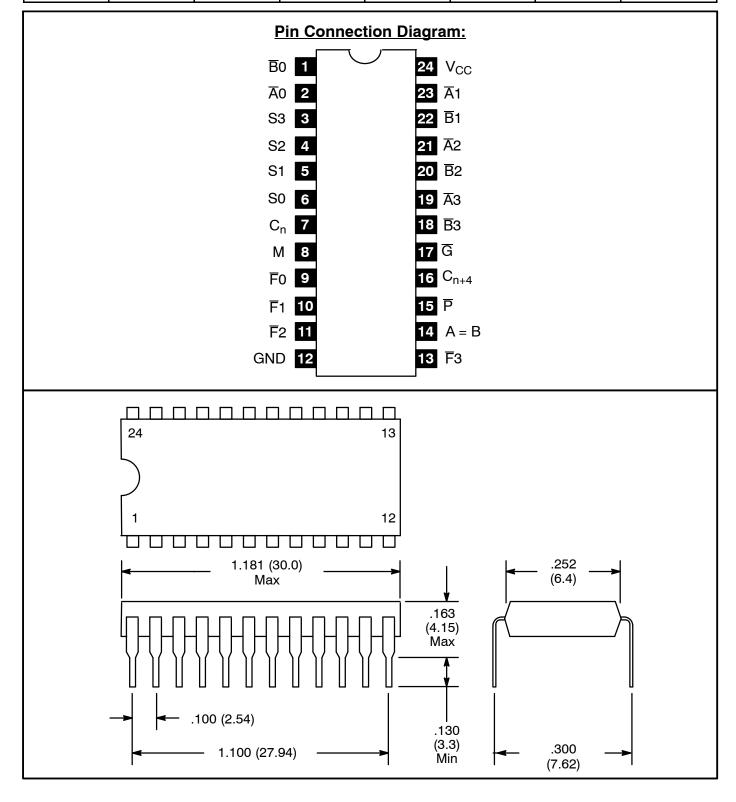

The NTE74181 is an arithmetic logic unit (ALU)/function generator in a 24–Lead DIP type package that has the complexity of 75 equivalent gates on a monolithic chip. This circuit performs 16 binary arithmetic operations on two 4–bit words as shown in Tables 1 and 2. These operations are selected by the four function–select lines (S0, S1, S2, S3) and include addition, subtraction, decrement, and, and straight transfer. When performing arithmetic manipulations, the internal carries must be enabled by applying a low–level voltage to the mode control input ((M). A full carry look–ahead scheme is made available in this device for fast, simultaneous carry generation by means of two cascade–out-puts (Pin15 and Pin17) for the four bits in the package. When used in conjunction with the NTE74182 or NTE74S182, full carry look–ahead circuits, high–speed arithmetic operations can be performed. The typical addition times shown in the Typical Additional Times table illustrate the little additional time required for addition of longer words when full carry look–ahead is employed.

If high speed is not of importance, a ripple–carry input ( $C_n$ ) and a ripple–carry output ( $C_{n+4}$ ) are available. However, the ripple–carry delay has also been minimized so that arithmetic manipulations for small word lengths can be performed without external circuitry.

#### Features:

- Full Look-Ahead for High Speed Operations on Long Words

- Input Clamping Diodes Minimize Transmission-Line Effects

- Darlington Outputs Reduce Turn-Off Time

- Arithmetic Operating Modes:

- Addition Subtraction Shift Operand A One Position Magnitude Comparison Plus Twelve Other Arithmetic Operations

- Logic Function Modes: Exclusive-OR

Comparator AND, NAND, OR, NOR Plus Ten Other Logic Operations

#### **Absolute Maximum Ratings:** ( $T_A = 0^\circ$ to +70°C unless otherwise specified)

| Supply Voltage (Note 1), V <sub>CC</sub>            | 7V             |

|-----------------------------------------------------|----------------|

| Input Voltage, V <sub>I</sub>                       |                |

| Interemitter Voltage (Note 2)                       | 5.5V           |

| Operating Ambient Temperature Range, T <sub>A</sub> | 0° to +70°C    |

| Storage Temperature Range, T <sub>stg</sub>         | –65° to +150°C |

Note 1. Voltage values, except interemitter voltage, are with respect to network ground terminal.

Note 2. This is the voltage between two emitters of a multiple–emitter transistor. For this circuit, this rating applies to each A input in conjunction with inputs S2 or S3, and to each B input in conjunction with inputs S0 or S3.

#### **Recommended Operation Conditions:**

| Parameter                                            | Symbol          | Min  | Тур | Max  | Unit |

|------------------------------------------------------|-----------------|------|-----|------|------|

| Supply Voltage                                       | V <sub>CC</sub> | 4.75 | 5.0 | 5.25 | V    |

| High-Level Output Current (All outputs except A = B) | I <sub>OH</sub> | _    | -   | -800 | μA   |

| Low-Level Output Current                             | I <sub>OL</sub> | _    | -   | 16   | mA   |

| Operating Ambient Temperature                        | T <sub>A</sub>  | 0    | -   | 70   | °C   |

# **<u>Electrical Characteristics</u>**: (T<sub>A</sub> = 0° to +70°C, Note 3, Note 4 unless otherwise specified)

| Parameter                                               | Symbol          | Test Conditions                                            |                           | Min | Тур | Max  | Unit |

|---------------------------------------------------------|-----------------|------------------------------------------------------------|---------------------------|-----|-----|------|------|

| High-Level Input Voltage                                | V <sub>IH</sub> |                                                            |                           | 2   | -   | -    | V    |

| Low-Level Input Voltage                                 | V <sub>IL</sub> |                                                            |                           | -   | -   | 0.8  | V    |

| Low-Level Clamp Voltage                                 | V <sub>IK</sub> | $V_{CC} = MIN, I_I = -12mA$                                |                           | -   | -   | -1.5 | V    |

| High-Level Output Voltage<br>Any Output Except A = B    | V <sub>OH</sub> | $V_{CC}$ = MIN, $V_{IH}$ = 2V, $V_{IL}$ = 0.8V, $I_{OH}$ = | –800μA                    | 2.4 | 3.4 | -    | V    |

| High–Level Output Current<br>A = B Output Only          | I <sub>ОН</sub> | $V_{CC} = MIN, V_{IH} = 2V, V_{IL} = 0.8V$                 | /, V <sub>OH</sub> = 5.5V | -   | -   | 250  | μΑ   |

| Low–Level Output Voltage<br>All Outputs                 | V <sub>OL</sub> | $V_{CC} = MIN, V_{IH} = 2V, V_{IL} = 0.8V$                 | /, I <sub>OL</sub> = 16mA | -   | 0.2 | 0.4  | V    |

| Input Current at Max Input Voltage                      | Ц               | $V_{CC} = MAX, V_I = 5.5V$                                 |                           | -   | -   | 1    | mA   |

| High-Level Input Current<br>Mode Input                  | IIH             | $V_{CC} = MAX, V_I = 2.4V$                                 |                           | -   | _   | 40   | μΑ   |

| Any A or B Input                                        |                 |                                                            |                           | -   | -   | 120  | μA   |

| Any S Input                                             |                 |                                                            |                           | -   | _   | 160  | μA   |

| Carry Input                                             |                 |                                                            |                           | -   | -   | 200  | μA   |

| Low-Level Input Current<br>Mode Input                   | Ι <sub>ΙL</sub> | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.4V               |                           | -   | _   | -1.6 | mA   |

| Any $\overline{A}$ or $\overline{B}$ Input              |                 |                                                            |                           | -   | -   | -4.8 | mA   |

| Any S Input                                             |                 |                                                            |                           | -   | -   | -6.4 | mA   |

| Carry Input                                             |                 |                                                            |                           | -   | -   | -8.0 | mA   |

| Short–Circuit Output Current<br>Any Output Except A = B | I <sub>OS</sub> | V <sub>CC</sub> = MAX, Note 5                              |                           | -18 | -   | -57  | mA   |

| Supply Current                                          | I <sub>CC</sub> | V <sub>CC</sub> = MAX, Note 5                              | Condition A               | _   | 88  | 140  | mA   |

|                                                         |                 |                                                            | Condition B               | Ι   | 94  | 150  | mA   |

Note 3. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

Note 4. All typical values at  $V_{CC} = 5V$ ,  $T_A = +25^{\circ}C$ .

- Note 5. Not more than one output should be shorted at a time.

- Note 6. With outputs open,  $I_{CC}$  is measured for the following conditions: A. S0 through S3, M, and  $\overline{A}$  inputs are at 4.5V, all other inputs are grounded.

- B. S0 through S3 and M are at 4.5V, all other inputs are grounded.

# <u>Switching Characteristics</u>: (V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C, C<sub>L</sub> = 15pF, R<sub>L</sub> = 400 $\Omega$ unless otherwise specified)

| Parameter                                                                        | Symbol           | Test Conditions                     | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------------|------------------|-------------------------------------|-----|-----|-----|------|

| Propagation Delay Time                                                           | t <sub>PLH</sub> |                                     | -   | 12  | 18  | ns   |

| (From C <sub>n</sub> Input to C <sub>n+4</sub> Output)                           | t <sub>PHL</sub> |                                     | -   | 13  | 19  | ns   |

| Propagation Delay Time                                                           | t <sub>PLH</sub> | M = 0V, S0 = S3 = 4.5V,             | -   | 28  | 43  | ns   |

| (From Any $\overline{A}$ or $\overline{B}$ Input to $C_{n+4}$ Output)            | t <sub>PHL</sub> | S1 = S2 = 0V (SUM Mode)             | -   | 27  | 41  | ns   |

| Propagation Delay Time                                                           | t <sub>PLH</sub> | M = 0V, S0 = S3 = 0V,               | -   | 35  | 50  | ns   |

| (From Any $\overline{A}$ or $\overline{B}$ Input to $C_{n+4}$ Output)            | t <sub>PHL</sub> | S1 = S2 = 4.5V (DIFF Mode)          | -   | 33  | 50  | ns   |

| Propagation Delay Time                                                           | t <sub>PLH</sub> | M = 0V,                             | -   | 13  | 19  | ns   |

| (From C <sub>n</sub> Input to Any F Output)                                      | t <sub>PHL</sub> | (SUM or DIFF Mode)                  | _   | 12  | 18  | ns   |

| Propagation Delay Time                                                           | t <sub>PLH</sub> | M = 0V, S0 = S3 = 4.5V,             | -   | 13  | 19  | ns   |

| (From Any A or B Input to G Output)                                              | t <sub>PHL</sub> | S1 = S2 = 0V ( <del>SUM</del> Mode) | -   | 13  | 19  | ns   |

| Propagation Delay Time                                                           | t <sub>PLH</sub> | M = 0V, S0 = S3 = 0V,               | -   | 17  | 25  | ns   |

| (From Any $\overline{A}$ or $\overline{B}$ Input to $\overline{G}$ Output)       | t <sub>PHL</sub> | S1 = S2 = 4.5V (DIFF Mode)          | -   | 17  | 25  | ns   |

| Propagation Delay Time                                                           | t <sub>PLH</sub> | M = 0V, S0 = S3 = 4.5V,             | -   | 13  | 19  | ns   |

| (From Any $\overline{A}$ or $\overline{B}$ Input to $\overline{P}$ Output)       | t <sub>PHL</sub> | S1 = S2 = 0V (SUM Mode)             | -   | 17  | 25  | ns   |

| Propagation Delay Time                                                           | t <sub>PLH</sub> | M = 0V, S0 = S3 = 0V,               | _   | 17  | 25  | ns   |

| (From Any $\overline{A}$ or $\overline{B}$ Input to $\overline{P}$ Output)       | t <sub>PHL</sub> | S1 = S2 = 4.5V (DIFF Mode)          | -   | 17  | 25  | ns   |

| Propagation Delay Time                                                           | t <sub>PLH</sub> | M = 0V, S0 = S3 = 4.5V,             | -   | 28  | 42  | ns   |

| (From Any $\overline{A_i}$ or $\overline{B_i}$ Input to $\overline{F_i}$ Output) | t <sub>PHL</sub> | S1 = S2 = 0V (SUM Mode)             | -   | 21  | 32  | ns   |

| Propagation Delay Time                                                           | t <sub>PLH</sub> | M = 0V, S0 = S3 = 0V,               | -   | 32  | 48  | ns   |

| (From Any $\overline{A_i}$ or $\overline{B_i}$ Input to $\overline{F_i}$ Output) | t <sub>PHL</sub> | S1 = S2 = 4.5V (DIFF Mode)          | -   | 23  | 34  | ns   |

| Propagation Delay Time                                                           | t <sub>PLH</sub> | M = 4.5V                            | -   | 32  | 48  | ns   |

| (From Any $\overline{A_i}$ or $\overline{B_i}$ Input to $\overline{F_i}$ Output) | t <sub>PHL</sub> | (Logic Mode)                        | -   | 23  | 34  | ns   |

| Propagation Delay Time                                                           | t <sub>PLH</sub> | M = 0V, S0 = S3 = 0V,               | _   | 35  | 50  | ns   |

| (From Any $\overline{A}$ or $\overline{B}$ Input to $A = B$ Output)              | t <sub>PHL</sub> | S1 = S2 = 4.5V (DIFF Mode)          | -   | 32  | 48  | ns   |

## **Typical Addition Times:**

|                   | Additional Times       | <u>J</u>                   |                                |                               |

|-------------------|------------------------|----------------------------|--------------------------------|-------------------------------|

| Number<br>of Bits | Using '181<br>and '182 | Arithmetic/<br>Logic Units | Look–Ahead<br>Carry Generators | Carry Method<br>Between ALU's |

| 1 to 4            | 24ns                   | 1                          | -                              | None                          |

| 5 to 8            | 36ns                   | 2                          | -                              | Ripple                        |

| 9 to 16           | 36ns                   | 3 or 4                     | 1                              | Full Look-Ahead               |

| 17 to 64          | 60ns                   | 5 to 16                    | 2 to 5                         | Full Look-Ahead               |

## Description (Cont'd):

The NTE74181 will accommodate active-high or active-low data if the pin designations are interpreted as follows:

| Pin Number                 | 2                | 1              | 23             | 22             | 21               | 21             | 19             | 18             | 9                | 10               | 11               | 13             | 7  | 16        | 15 | 17 |

|----------------------------|------------------|----------------|----------------|----------------|------------------|----------------|----------------|----------------|------------------|------------------|------------------|----------------|----|-----------|----|----|

| Active-Low Data (Table 1)  | $\overline{A}_0$ | B <sub>0</sub> | Ā <sub>1</sub> | B <sub>1</sub> | $\overline{A}_2$ | B <sub>2</sub> | Ā <sub>3</sub> | B <sub>3</sub> | $\overline{F}_0$ | $\overline{F}_1$ | $\overline{F}_2$ | $F_3$          | Cn | $C_{n+4}$ | P  | G  |

| Active-High Data (Table 2) | A <sub>0</sub>   | B <sub>0</sub> | A <sub>1</sub> | B <sub>1</sub> | A <sub>2</sub>   | B <sub>2</sub> | A <sub>3</sub> | B <sub>3</sub> | F <sub>0</sub>   | F <sub>1</sub>   | F <sub>2</sub>   | F <sub>3</sub> | Cn | Cn+4      | Х  | Y  |

## Description (Cont'd):

Subtraction is accomplished by 1's complement addition where the 1's complement of the substrahend is generated internally. The resultant output is A–B–1, which requires an end–around or forced carry to provide A–B.

The NTE74181 can also be utilized as a comparator. The A = B output is internally decoded from the function outputs (F0, F1, F2, F3) so that when two words of equal magnitude are applied at the A and b inputs, it will assume a high level to indicate equality (A = B). The ALU must be in the subtract mode with  $C_n = H$  when performing this comparison. The A = B output is open-collector so that it can be wire-AND connected to give a comparison fo more than four bits. The carry output ( $C_{n+4}$ ) can also be used to supply relative magnitude information. Again, the ALU must be placed in the subtract mode by placing the function select inputs S3, S2, S1, S0 at L, H, H, L, respectively.

| Input C <sub>n</sub> | Output C <sub>n+4</sub> | Active-Low Data | Active-High Data |

|----------------------|-------------------------|-----------------|------------------|

| Н                    | Н                       | A ≥ B           | A ≤ B            |

| Н                    | L                       | A < B           | A > B            |

| L                    | Н                       | A > B           | A < B            |

| L                    | L                       | A ≤ B           | A ≥ B            |

This circuit has been designed to not only incorporate all of the designer's requirements for arithmetic operations, but also to provide 16 possible functions of two Boolean variables without the use of external circuitry. These logic functions are selected by use of the four function–select inputs (S0, S1, S2, S3) with the mode–control input (M) at a high level to disable th internal carry. The 16 logic functions are detailed in tables 1 and 2 and include exclusive–OR, NAND, AND, NOR, and OR functions.

#### Signal Designations:

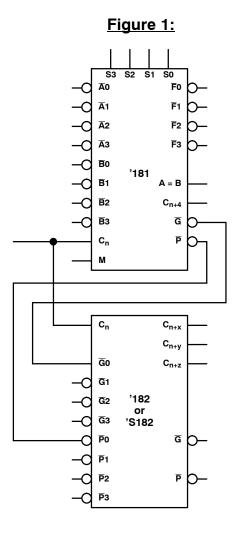

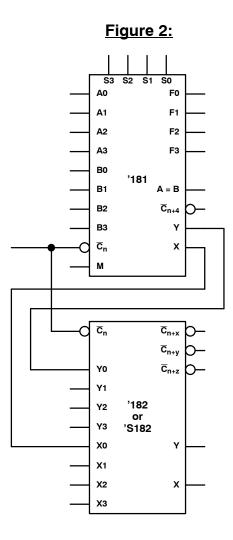

The NTE74181 together with the '182 and 'S182 can be used with the signal designations of either Figure 1 or Figure 2. The inversion indicators (O) and the bars over the terminal letter symbols (e.g.,  $\overline{C}$ ) each indicate that the associated input or output is active with respect to the selected function of the device when the input output is low. That is, a low  $\overline{C}$  means "do carry" while a high means "do not carry".

The logic functions and arithmetic operations obtained with signal designations of Figure 1 are given in Table 1; those obtained with signal designations of Figure 2 are given in Table 2.

<u> Table 1:</u>

|    | Sele  | otion |    |                             | Active-Low Data                  |                                         |

|----|-------|-------|----|-----------------------------|----------------------------------|-----------------------------------------|

|    | Selet | Suon  |    | M = H                       | M = L; Arithme                   | etic Operations                         |

| S3 | S2    | S1    | S0 | Logic Functions             | C <sub>n</sub> = L (no carry)    | C <sub>n</sub> = H (with carry)         |

| L  | L     | L     | L  | $F = \overline{A}$          | F = A MINUS 1                    | F = A                                   |

| L  | L     | L     | Н  | $F = \overline{AB}$         | F = AB MINUS 1                   | F = AB                                  |

| L  | L     | Н     | L  | $F = \overline{A} + B$      | $F = A\overline{B}$ MINUS 1      | $F = A\overline{B}$                     |

| L  | L     | Н     | Н  | F = 1                       | F = MINUS 1 (2's COMPL)          | F = ZERO                                |

| L  | Н     | L     | L  | $F = \overline{A + B}$      | $F = A PLUS (A + \overline{B})$  | $F = A PLUS (A + \overline{B}) PLUS 1$  |

| L  | Н     | L     | Н  | $F = \overline{B}$          | $F = AB PLUS (A + \overline{B})$ | $F = AB PLUS (A + \overline{B}) PLUS 1$ |

| L  | Н     | Н     | L  | $F = \overline{A \oplus B}$ | F = A MINUS B MINUS 1            | F = A MINUS B                           |

| L  | Н     | Н     | Н  | $F = A + \overline{B}$      | $F = A + \overline{B}$           | $F = (A + \overline{B}) PLUS 1$         |

| L  | L     | L     | L  | $F = \overline{A}B$         | F = A PLUS (A + B)               | F = A PLUS (A + B) PLUS 1               |

| н  | L     | L     | Н  | $F = A \oplus B$            | F = A PLUS B                     | F = A PLUS B PLUS 1                     |

| н  | L     | Н     | L  | F = B                       | $F = A\overline{B} PLUS (A + B)$ | $F = A\overline{B} PLUS (A + B) PLUS 1$ |

| н  | L     | Н     | Н  | F = A + B                   | F = (A + B)                      | F = (A + B) PLUS 1                      |

| н  | Н     | L     | L  | F = 0                       | F = A                            | F = A PLUS A PLUS 1                     |

| н  | Н     | L     | Н  | $F = A\overline{B}$         | F = AB PLUS A                    | F = AB PLUS A PLUS 1                    |

| н  | Н     | Н     | L  | F = AB                      | $F = A\overline{B} PLUS A$       | $F = A\overline{B} PLUS A PLUS 1$       |

| Н  | Н     | Н     | Н  | F = A                       | F = A                            | F = A PLUS 1                            |

<u> Table 2:</u>

|    | Seleo | otion |    |                             | Active-High Data                            |                                         |

|----|-------|-------|----|-----------------------------|---------------------------------------------|-----------------------------------------|

|    | Selet | Suon  |    | M = H                       | M = L; Arithme                              | etic Operations                         |

| S3 | S2    | S1    | S0 | Logic Functions             | <mark>C</mark> <sub>n</sub> = H (no carry)  | $\overline{C}_n = L$ (with carry)       |

| L  | L     | L     | L  | $F = \overline{A}$          | F = A                                       | F = A PLUS 1                            |

| L  | L     | L     | Н  | $F = \overline{A + B}$      | F = A + B                                   | F = (A + B) PLUS 1                      |

| L  | L     | Н     | L  | F = ĀB                      | $F = A + \overline{B}$                      | $F = (A + \overline{B}) PLUS 1$         |

| L  | L     | Н     | Н  | F = 0                       | F = MINUS 1 (2's COMPL)                     | F = ZERO                                |

| L  | Н     | L     | L  | $F = \overline{AB}$         | $F = A PLUS A\overline{B}$                  | $F = A PLUS A\overline{B} PLUS 1$       |

| L  | Н     | L     | Н  | $F = \overline{B}$          | $F = (A + \overline{B}) PLUS A\overline{B}$ | $F = (A + B) PLUS A\overline{B} PLUS 1$ |

| L  | Н     | Н     | L  | $F = A \oplus B$            | F = A MINUS B MINUS 1                       | F = A MINUS B                           |

| L  | Н     | Н     | Н  | $F = A\overline{B}$         | $F = A\overline{B} MINUS 1$                 | F = AB                                  |

| L  | L     | L     | L  | $F = \overline{A} + B$      | F = A PLUS AB                               | F = A PLUS AB PLUS 1                    |

| н  | L     | L     | Н  | $F = \overline{A \oplus B}$ | F = A PLUS B                                | F = A PLUS B PLUS 1                     |

| н  | L     | Н     | L  | F = B                       | $F = (A + \overline{B}) PLUS AB$            | $F = (A + \overline{B}) PLUS AB PLUS 1$ |

| н  | L     | Н     | Н  | F = AB                      | F = AB MINUS 1                              | F = AB                                  |

| н  | Н     | L     | L  | F = 1                       | F = A                                       | F = A PLUS A PLUS 1                     |

| н  | Н     | L     | Н  | $F = A + \overline{B}$      | F = (A + B) PLUS A                          | F = (A + B) PLUS A PLUS 1               |

| н  | Н     | Н     | L  | F = A + B                   | $F = (A + \overline{B}) PLUS A$             | $F = (A + \overline{B}) PLUS A PLUS 1$  |

| Н  | Н     | Н     | Н  | F = A                       | F = A MINUS 1                               | F = A                                   |

## Parameter Measurement Information:

| Parameter        | Input            | Other Inpu     | t Same Bit     | Other Da                          | ta Inputs                                 | Output              | Output       |

|------------------|------------------|----------------|----------------|-----------------------------------|-------------------------------------------|---------------------|--------------|

| Parameter        | Under Test       | Apply 4.5V     | Apply GND      | Apply 4.5V                        | Apply GND                                 | Under Test          | Waveform     |

| t <sub>PLH</sub> | Āi               | B <sub>i</sub> | None           | Remaining                         | C <sub>n</sub>                            | Fi                  | In-Phase     |

| t <sub>PHL</sub> |                  |                |                | $\overline{A}$ and $\overline{B}$ |                                           |                     |              |

| t <sub>PLH</sub> | B <sub>i</sub>   | Āi             | None           | Remaining                         | C <sub>n</sub>                            | Fi                  | In-Phase     |

| t <sub>PHL</sub> |                  |                |                | $\overline{A}$ and $\overline{B}$ |                                           |                     |              |

| t <sub>PLH</sub> | Āi               | B <sub>i</sub> | None           | None                              | Remaining                                 | P                   | In-Phase     |

| t <sub>PHL</sub> |                  |                |                |                                   | $\overline{A}$ and $\overline{B}$ , $C_n$ |                     |              |

| t <sub>PLH</sub> | B <sub>i</sub>   | Āi             | None           | None                              | Remaining                                 | P                   | In-Phase     |

| t <sub>PHL</sub> |                  |                |                |                                   | $\overline{A}$ and $\overline{B}$ , $C_n$ |                     |              |

| t <sub>PLH</sub> | A <sub>i</sub>   | None           | B <sub>i</sub> | Remaining                         | Remaining                                 | G                   | In-Phase     |

| t <sub>PHL</sub> |                  |                |                | B                                 | Ā, C <sub>n</sub>                         |                     |              |

| t <sub>PLH</sub> | B <sub>i</sub>   | None           | Ā              | Remaining                         | Remaining                                 | G                   | In-Phase     |

| t <sub>PHL</sub> |                  |                |                | B                                 | Ā, C <sub>n</sub>                         |                     |              |

| t <sub>PLH</sub> | C <sub>n</sub>   | None           | None           | All A                             | All B                                     | Any F               | In-Phase     |

| t <sub>PHL</sub> |                  |                |                |                                   |                                           | or C <sub>n+4</sub> |              |

| t <sub>PLH</sub> | Āi               | None           | B <sub>i</sub> | Remaining                         | Remaining                                 | C <sub>n+4</sub>    | Out-of-Phase |

| t <sub>PHL</sub> |                  |                |                | В                                 | A, C <sub>n</sub>                         |                     |              |

| t <sub>PLH</sub> | - B <sub>i</sub> | None           | Āi             | Remaining                         | Remaining                                 | C <sub>n+4</sub>    | Out-of-Phase |

| t <sub>PHL</sub> | 1                |                |                | В                                 | Ā, C <sub>n</sub>                         |                     |              |

#### **SUM Mode Test Table** Function Inputs: S0 = S3 = 4.5V, S1 = S2 = M = 0V

## **DIFF** Mode Test Table

Function Inputs: S1 = S2 = 4.5V, S0 = S3 = M = 0V

| Parameter        | Input          | Other Inpu     | t Same Bit     | Other Da                              | ta Inputs                                 | Output           | Output       |

|------------------|----------------|----------------|----------------|---------------------------------------|-------------------------------------------|------------------|--------------|

| Farameter        | Under Test     | Apply 4.5V     | Apply GND      | Apply 4.5V                            | Apply GND                                 | Under Test       | Waveform     |

| t <sub>PLH</sub> | A <sub>i</sub> | None           | B <sub>i</sub> | Remaining                             | Remaining                                 | Fi               | In-Phase     |

| t <sub>PHL</sub> |                |                |                | Ā                                     | B, C <sub>n</sub>                         |                  |              |

| t <sub>PLH</sub> | B <sub>i</sub> | Āi             | None           | Remaining                             | Remaining                                 | Fi               | Out-of-Phase |

| t <sub>PHL</sub> |                |                |                | Ā                                     | B, C <sub>n</sub>                         |                  |              |

| t <sub>PLH</sub> | Āi             | None           | B <sub>i</sub> | None                                  | Remaining                                 | P                | In-Phase     |

| t <sub>PHL</sub> |                |                |                |                                       | $\overline{A}$ and $\overline{B}$ , $C_n$ |                  |              |

| t <sub>PLH</sub> | B <sub>i</sub> | Āi             | None           | None                                  | Remaining                                 | P                | Out-of-Phase |

| t <sub>PHL</sub> |                |                |                |                                       | $\overline{A}$ and $\overline{B}$ , $C_n$ |                  |              |

| t <sub>PLH</sub> | A <sub>i</sub> | B <sub>i</sub> | None           | None                                  | Remaining                                 | G                | In-Phase     |

| t <sub>PHL</sub> |                |                |                |                                       | $\overline{A}$ and $\overline{B}$ , $C_n$ |                  |              |

| t <sub>PLH</sub> | B <sub>i</sub> | None           | Āi             | None                                  | Remaining                                 | G                | Out-of-Phase |

| t <sub>PHL</sub> | 1              |                |                |                                       | $\overline{A}$ and $\overline{B}$ , $C_n$ |                  |              |

| t <sub>PLH</sub> | Āi             | None           | B <sub>i</sub> | Remaining                             | Remaining                                 | A = B            | In-Phase     |

| t <sub>PHL</sub> |                |                |                | Ā                                     | B, C <sub>n</sub>                         |                  |              |

| t <sub>PLH</sub> | B <sub>i</sub> | Āi             | None           | Remaining                             | Remaining                                 | A = B            | Out-of-Phase |

| t <sub>PHL</sub> |                |                |                | Ā                                     | B, C <sub>n</sub>                         |                  |              |

| t <sub>PLH</sub> | C <sub>n</sub> | None           | None           | All $\overline{A}$ and $\overline{B}$ | None                                      | C <sub>n+4</sub> | In-Phase     |

| t <sub>PHL</sub> |                |                |                |                                       |                                           | or Any F         |              |

| t <sub>PLH</sub> | A <sub>i</sub> | B <sub>i</sub> | None           | None                                  | Remaining                                 | C <sub>n+4</sub> | Out-of-Phase |

| t <sub>PHL</sub> | ]              |                |                |                                       | Ā, Ħ, C <sub>n</sub>                      |                  |              |

| t <sub>PLH</sub> | B <sub>i</sub> | None           | A <sub>i</sub> | None                                  | Remaining                                 | C <sub>n+4</sub> | In-Phase     |

| t <sub>PHL</sub> | 1              |                |                |                                       | Ā, Ħ, C <sub>n</sub>                      |                  |              |

### Parameter Measurement Information (Cont'd):

#### Logic Mode Test Table

Function Inputs: S1 = S2 = M = 4.5V, S0 = S3 = 0V

| Parameter        | Input          | Other Inpu | it Same Bit | Other Da   | ta Inputs                                 | Output     | Output       |  |

|------------------|----------------|------------|-------------|------------|-------------------------------------------|------------|--------------|--|

| Falameter        | Under Test     | Apply 4.5V | Apply GND   | Apply 4.5V | Apply GND                                 | Under Test | Waveform     |  |

| t <sub>PLH</sub> | Āi             | Bi         | None        | None       | Remaining                                 | Fi         | Out-of-Phase |  |

| t <sub>PHL</sub> | 1              |            |             |            | $\overline{A}$ and $\overline{B}$ , $C_n$ |            |              |  |

| t <sub>PLH</sub> | B <sub>i</sub> | Ā          | None        | None       | Remaining                                 | Fi         | Out-of-Phase |  |

| t <sub>PHL</sub> |                |            |             |            | $\overline{A}$ and $\overline{B}$ , $C_n$ |            |              |  |