# User Manual DA14706 PRO Development kit

**UM-B-148**

### **Abstract**

Hardware description of the DA14706 PRO development kit, including DA14706 or DA14708 PRO daughterboards, PRO motherboard and the accompanying boards which mounted on the motherboard, namely the LCD module and the power measurement module.

# **Table of Contents**

| Abst            | tract                                                                      | 1  |

|-----------------|----------------------------------------------------------------------------|----|

| Figu            | res                                                                        | 3  |

| Tabl            | es                                                                         | 4  |

| 1               | Terms and Definitions                                                      | 5  |

| 2               | References                                                                 | 6  |

| •               | Later Leaffer BA44700 BBO Benefit and Life                                 | _  |

| 3               | Introduction DA14706 PRO Development kit                                   |    |

| 3.1             | Introduction                                                               |    |

| 3.2             | Features                                                                   |    |

| 3.3             | PRO Development kit Hardware block diagram                                 | 8  |

| 4               | PRO-Motherboard main features                                              | 9  |

| 4.1             | USB HUB                                                                    | 12 |

| 4.2             | USB to UART                                                                | 12 |

| 4.3             | USB to Serial Wire Debug port (SWD)                                        | 14 |

| 4.4             | Audio Codec section                                                        | 15 |

| 4.5             | Expansion SPI Connector                                                    |    |

| 4.6             | Voltage level translation (debugging) section                              | 17 |

| 4.7             | Push Buttons                                                               | 18 |

| 4.8             | GPIO assignment                                                            |    |

| 4.9             | QSPI-RAM                                                                   |    |

| 4.10            | QSPI FLASH                                                                 |    |

| 4.11            | Break-out connector (J6)                                                   |    |

| 4.12            | DA14706 PRO-Motherboard power configuration                                | 28 |

| 5               | Power measurement circuitry                                                | 31 |

| 5.1             | The Power measurement circuitry, the monitoring section on PRO-Motherboard |    |

| 5.2             | The power measurement module 2 (PMM2), da1470x-sb-pmm2, (500-29-x)         |    |

| 5.              | 2.1 Accuracy of current measurement for DA1470x system (VLDO)              | 37 |

| 5.              | 2.2 Settings of power configuration header J9                              |    |

| 6               | LCD interface and add-on board                                             | 40 |

| 6.1             | LCD interface on PRO-Motherboard                                           |    |

| 6.2             | LCD Amoled board, da1470x-sb-E120A390QSR (500-31-X)                        |    |

| 7               | DBO Daughtorhoard                                                          | 42 |

| <i>1</i><br>7.1 | PRO Daughterboard                                                          |    |

| 7.1<br>7.2      | Main Components Description                                                |    |

| 7.3             | Debugging section                                                          |    |

| 7.3<br>7.4      | Audio Section                                                              |    |

| 7.5             | RF Section                                                                 |    |

| 7.6             | Power section                                                              |    |

| 7.7             | QSPI FLASH                                                                 |    |

|                 | CO                                                                         |    |

| 8      | Quick Setup                                                                            |    |

|--------|----------------------------------------------------------------------------------------|----|

| 8.1    | Hardware setup                                                                         |    |

| 8.2    | Debug interfaces – SWD / JTAG                                                          |    |

| 8.3    | Debug interfaces UART                                                                  | 57 |

|        |                                                                                        |    |

|        |                                                                                        |    |

|        |                                                                                        |    |

|        |                                                                                        |    |

| Figu   | ires                                                                                   |    |

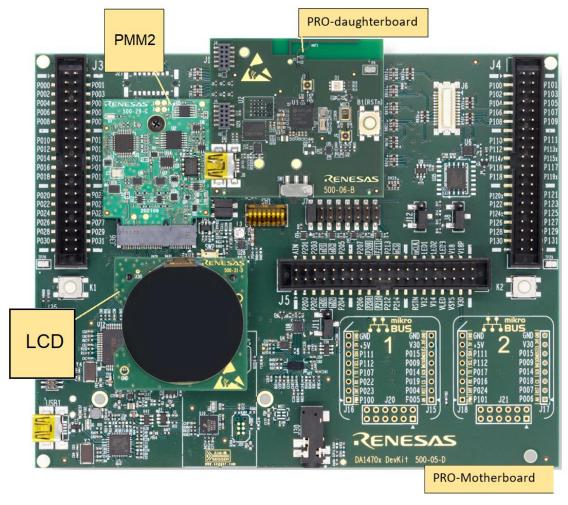

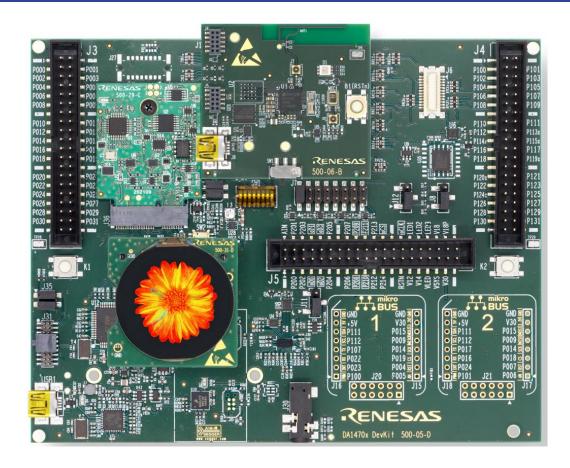

| Figure | e 1: DA14706 PRO Development kit                                                       | 7  |

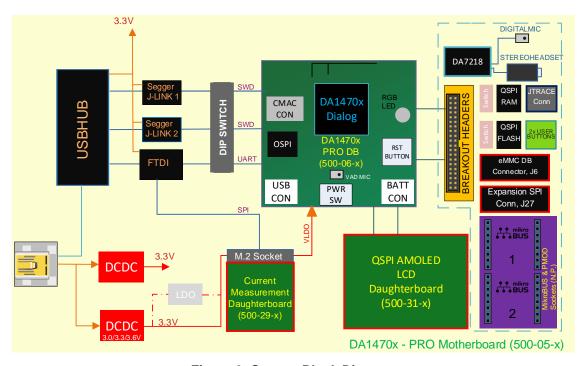

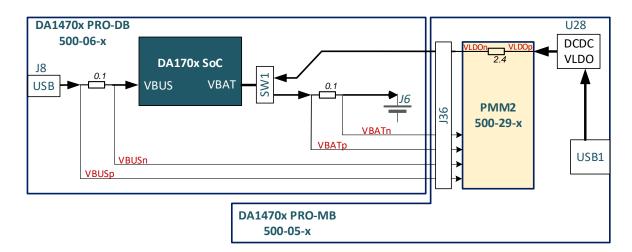

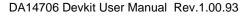

| Figure | e 2: System Block Diagram                                                              | 8  |

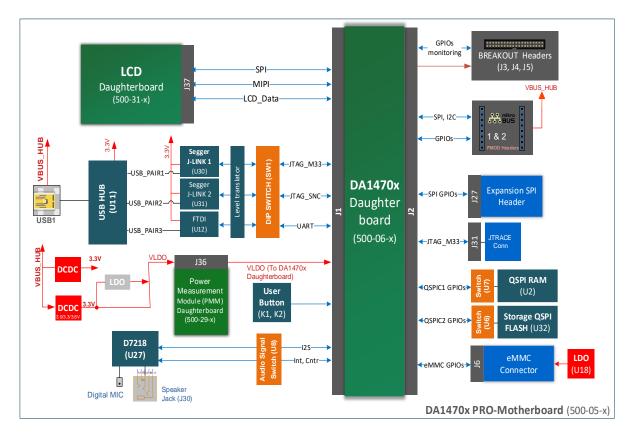

| Figure | e 3: Engineering level, voltage & interface, PRO-Motherboard block diagram             | 9  |

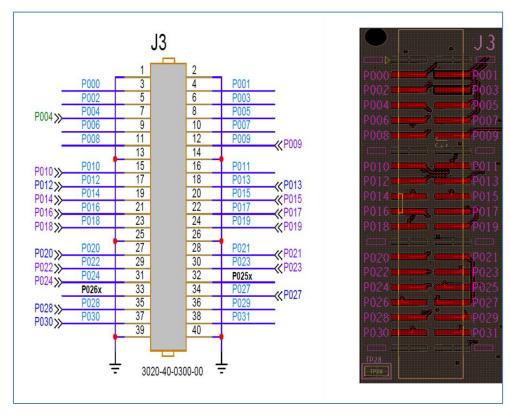

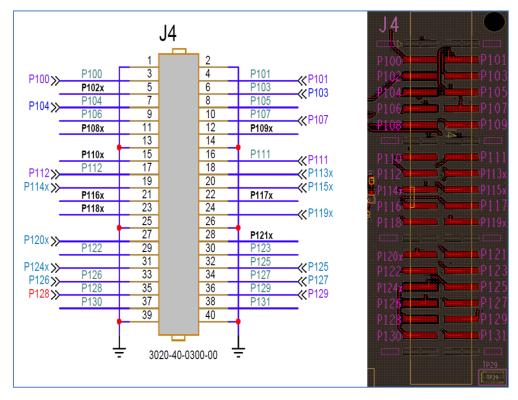

| Figure | e 4: Monitoring Header J3: Schematic (left) & PCB (right)                              | 10 |

| Figure | e 5: Monitoring Header J4: Schematic (left) & PCB (right)                              | 10 |

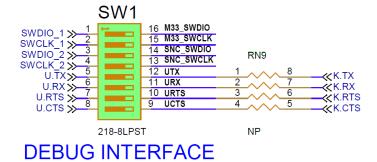

| Figure | e 6: Debug interface including DIP switch SW1                                          | 11 |

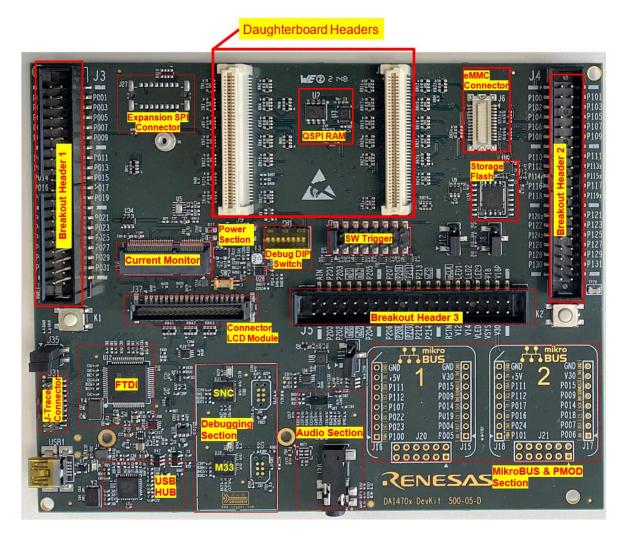

| Figure | e 7: PCB top of the DA1470x PRO Development Kit Top                                    | 11 |

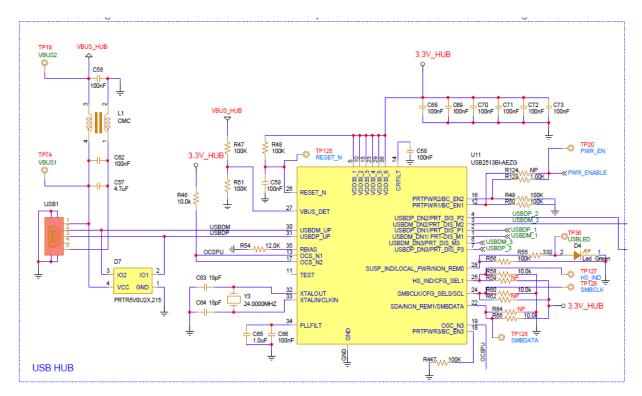

| Figure | e 8: USB HUB Circuitry of DA14706 PRO-Motherboard                                      | 12 |

| Figure | 9: USB to UART (FTDI module)                                                           | 13 |

| Figure | e 10: UART & SWD signals                                                               | 13 |

| Figure | e 11: MK22 debugger schematic (for M33)                                                | 14 |

| Figure | e 12: J-Trace connector for M33                                                        | 15 |

| Figure | e 13: Audio section schematic                                                          | 15 |

| Figure | e 14: Analog Switch (U8) used to isolate the Digital Audio interface                   | 16 |

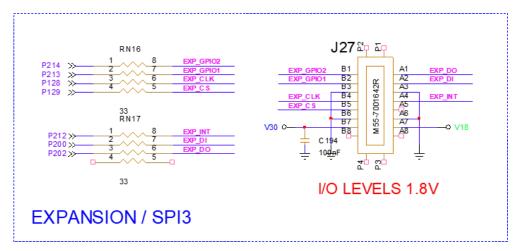

| Figure | e 15: Expansion SPI connector (J27)                                                    | 16 |

| Figure | e 16: Voltage Level Translation Circuit                                                | 17 |

| Figure | e 17: Push Buttons used in the DA1470x PRO-Motherboard                                 | 18 |

| Figure | e 18: QSPI RAM schematic                                                               | 23 |

| Figure | e 19: QSPI RAM Analog Switch                                                           | 23 |

| _      | e 20: QSPI RAM power switch                                                            |    |

| •      | e 21: Default QSPI flash AT25SL128A-MHE-T                                              |    |

| -      | e 22: Two QSPI Flash PCB footprint options (not populated)                             |    |

| •      | e 23: Analog switch (U6) used for the QSPI flash signals                               |    |

|        | e 24: QSPI Flash power switch                                                          |    |

| Figure | e 25: eMMC connector schematic                                                         | 27 |

| Figure | e 26: Power configuration applied on PRO-Motherboard                                   | 28 |

| -      | e 27: VLDOp voltage generation                                                         |    |

| Figure | e 28: 3.3V LDO for PRO-Motherboard peripherals                                         | 29 |

| Figure | e 29: Power Measurement Module (PMM2) block diagram                                    | 31 |

|        | e 30: Current Measurement socket (M2)                                                  |    |

|        | e 31: the hardware setup for current measurements                                      |    |

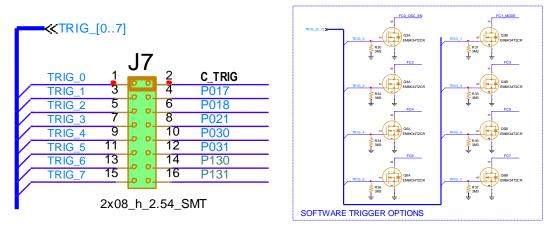

|        | e 32: C_TRIG selection jumper block (J7) & buffer MOSFETS for I/O levels compatibility |    |

| _      | e 33: PMM2 current Measurement Circuit PMM2                                            |    |

| _      | e 34: PMM2 on board peripherals (Power supply, Memory etc.)                            |    |

| -      | e 35: Current measurement unit PCBA (TOP)                                              |    |

| -      | e 36: Normal mode (1µA to 500mA at 3.3V) data after offset calibration                 |    |

|        | e 37: Hibernation mode (100nA to 60uA at 3.3V) data after offset calibration           |    |

| -      | e 38: Power connections                                                                |    |

| -      | e 39: Header schematic for LCD daughterboard (Interface board)                         |    |

|        | e 40: LCD add-on daughterboard                                                         |    |

| Figure | e 41: QSPI AMOLED LCD daughterboard position on PRO-Development kit                    | 42 |

| Figure 42: LCD TFT daughterboard top (left) and PCBA bottom side (right)            | 42 |

|-------------------------------------------------------------------------------------|----|

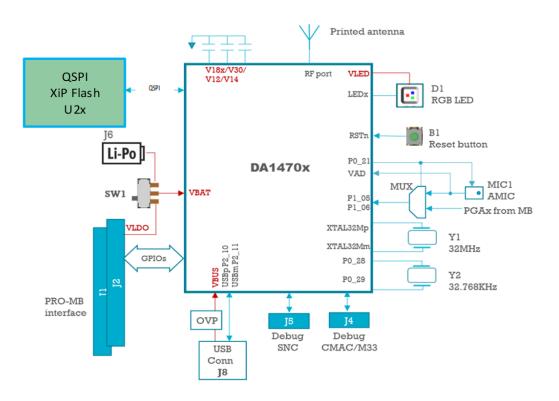

| Figure 43: System Block Diagram of DA1470x PRO-Daughterboard                        |    |

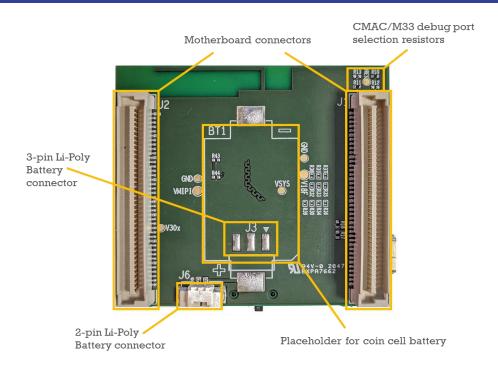

| Figure 44: PCB top of the DA14706 PRO- Daughterboard                                |    |

| Figure 45: PCB bottom of the DA1470x PRO- Daughterboard                             |    |

| Figure 46: PRO- Daughterboard. interface connectors to PRO-Motherboard              |    |

| Figure 47: CMAC/M33 & SNC debugging connectors schematic                            |    |

| Figure 48: VAD Analog MIC                                                           |    |

| Figure 49: Programmable gain amplifier signal routing                               |    |

| Figure 50: RF Section of PRO-Daughterboard.                                         |    |

| Figure 51: PRO-Daughterboard Power options                                          |    |

| Figure 52: USB OVP protection (U3) & Rsence (R18)                                   |    |

| Figure 53: MX25U6432FZNI02 QSPI FLASH schematic                                     |    |

| Figure 54: V18P & V18F are connected through R22                                    |    |

| Figure 55: Resistor network for the monitoring signals                              |    |

| Figure 56: PCB marking of GPIO signals not directly connected to monitoring headers | 53 |

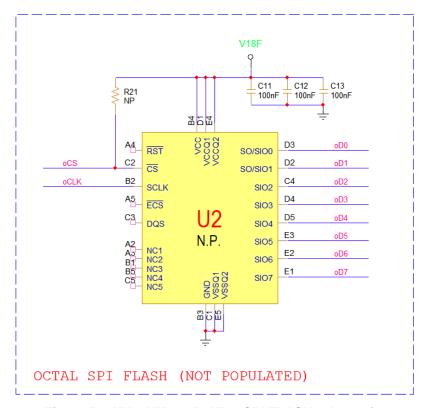

| Figure 57: MX66UM1G45GXD OSPI FLASH schematic                                       | 54 |

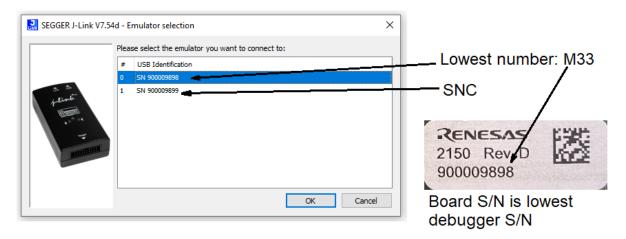

| Figure 58: SWD/JTAG ports to use                                                    | 56 |

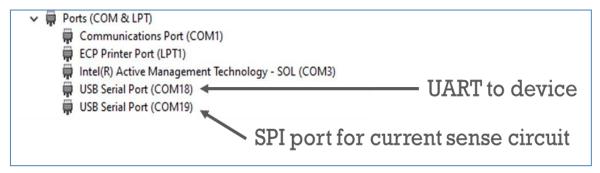

| Figure 59: Virtual COM port selection                                               | 57 |

| Tables                                                                              |    |

| Table 1: Signals with level translation                                             | 17 |

| Table 2: DA14706 PRO-Development kit GPIO pin assignment                            |    |

| Table 3: U6 truth table                                                             | 26 |

| Table 4: SW2 switch voltage settings                                                | 29 |

| Table 5: Monitored Power Sources                                                    | 33 |

| Table 6: Accuracy of the Current Measurement Circuit                                | 38 |

| Table 7Jumper setting of current measurement connector J9                           |    |

| Table 8: DA1470x Product Family Differentiation                                     | 46 |

| Table 9: DA1470x SoC Voltage domains                                                |    |

| Table 10: XTAL32M Recommended Operating Conditions                                  |    |

| Table 11: XTAL32K Recommended Operating Conditions                                  |    |

| Table 12: Flash memory signals to the monitoring headers at PRO-Motherboard         |    |

| Table 13: DA14706 PRO-Development kit, Quick setup                                  | 55 |

# 1 Terms and Definitions

AFE Analog Front End

BLE Bluetooth Low Energy

Dev Kit Development Kit

PRO-Devkit Professional Development Kit

PRO-DB PRO-Daughterboard

PRO-MB PRO-Motherboard

DB Daughterboard

MB Mainboard or motherboard

OPAMP Operational Amplifier

OVP Over Voltage Protection

PCB Printed Circuit Board

SDK SW Development Kit

HDK HW Development Kit

## 2 References

- 1. Device specification, DA1470x Datasheet

- 2. HW Design, PRO-Motherboard, da1470x-mb\_[500-05-x]

- 3. HW Design, PRO-daughterboard, da1470x-db-vfbga142\_[500-06-x]

- 4. HW Design, Current Sense, da1470x-sb-pmm2\_[500-29-x]

- 5. HW Design, LCD, da1470x-sb-ctspilcd\_[500-31-x]

# 3 Introduction DA14706 PRO Development kit

#### 3.1 Introduction

The DA14706 PRO Development kit consists of the PRO-Motherboard and PRO-daughterboard.

Special attention for the design of this kit has been given in providing a trouble-free user experience and keeping compatibility with the existing tools from the DA1458x/DA1468x/DA1469x product lines.

The PRO development kit when combined with the DA1470x SDK and SmartSnippets tools, provides an easy to use and complete platform for software/hardware development.

In this document we focus on the DA14706 PRO Development kit which consists of the following parts:

- PRO-Motherboard (PRO-MB)

- o da1470x-mb, PCBA reference number 500-05-x

- PRO-daughterboard (PRO-DB)

- o da1470x-db-vfbga142, PCBA reference number 500-06-x

- Power Measurement Module 2 (PMM2) add-on

- o da1470x-sb-pmm2, PCB reference number 500-29-x

- LCD add-on for TFT 390x390

- o da1470x-sb-ctspilcd, PCB reference number 500-31-x

Figure 1: DA14706 PRO Development kit

#### 3.2 Features

- DA1470x silicon easily replaceable on a daughterboard core module

- Dedicated daughterboard for current measurement (on a M2 socket)

- LCD daughterboard

- On-board basic peripherals for demo and development

- Look and feel like previous PRO-Development kits

- Flexible & robust power options

- JTAG debugger on Board and connectivity to PC for M33 and SNC.

- Voltage translation section for minimizing leakage

- DIP switches for breaking-up certain signal allowing power measurements & debugging

- Header for JTAG debugger for CMAC

- 64 Mbit, QSPI NOR Flash memory for eXecute in Place (XiP)

- 256 Mbit Storage QSPI NOR Flash

- 64 Mbit QSPI RAM

- Break-out header (J6) for connecting an add-on board with eMMC (DA14708) or other peripheral.

- Headers for I/O monitoring and expandability1

- Audio codec with jack speaker phone & digital mic capabilities

- Analog Microphone

- RGB LED

- Two general purpose Push Buttons

- Option to support two MikroBUS click boards & PMOD interface

- Generic SPI expansion header (J27)

- Provisions for automated test

### 3.3 PRO Development kit Hardware block diagram

Figure 2: System Block Diagram

## 4 PRO-Motherboard main features

- Single USB connector \*NOTE: USB host must support USB 2.0 high-speed for reliable power measurements

- USB hub with 3 downstream ports

- Port1: Segger JLink-OB SWD-JTAG debugger for ARM Cortex M33

- Port2: FT2232H multiprotocol serial interface providing a booting/debugging/HCI UART (2 or 4-pin) and SPI connected to the current measurement daughterboard A/D converter

- o Port3: Segger JLink-OB SWD-JTAG debugger for SNC

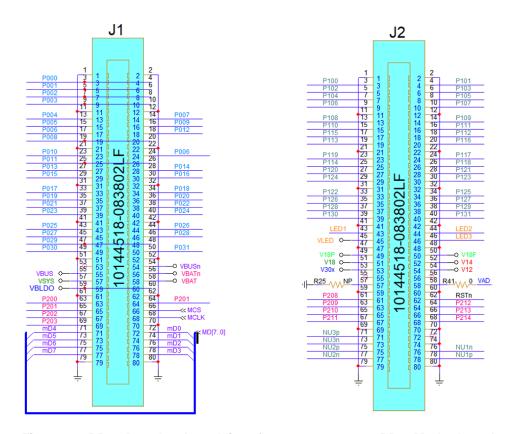

- 2 Connectors mating to the DA1470x daughterboard

- Breakout Headers (3 pcs 2x20pin) for monitoring GPIO and power signals, with markings of signal names on the PCB top silkscreen (Figure 3)

- Two user button, K1 & K2 connected to GPIOs through header J35

- DIP switch to isolate UART and JTAG signals (in case we need to secure the most accurate sleep current measurements)

- Test points on the bottom layer

- Ground points (TP28, TP29) for connecting crocodile clips

- QSPI-RAM with option to disconnect the related GPIOs from the long traces travelling to breakout headers & MikroBUS sockets

Figure 3: Engineering level, voltage & interface, PRO-Motherboard block diagram

Figure 4: Monitoring Header J3: Schematic (left) & PCB (right)

Figure 5: Monitoring Header J4: Schematic (left) & PCB (right)

- QSPI flash (with three footprint options)

- dedicated connector (J6) which can accept an eMMC flash daughterboard

- Optional 2x MikroBUS sockets (supporting 3.3V compatible click boards)

- PMOD interface (shares same signals with MIKROBUS sockets)

- GPIOs marked with an 'x' at the end (e.g.P113x) have dual usage described in 4.9 and in 4.11

Figure 6: Debug interface including DIP switch SW1

Figure 7: PCB top of the DA1470x PRO Development Kit Top

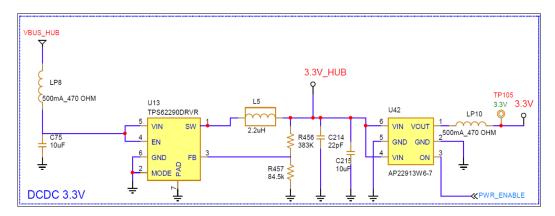

#### 4.1 USB HUB

Figure 8: USB HUB Circuitry of DA14706 PRO-Motherboard

The USB HUB of DA14706 PRO-Motherboard is implemented by U11, USB2513B. This chip is supplied with 3.3V from a voltage regulator, U13.

The signal PWR\_ENABLE is generated from U11 and it is an active high signal. It enables the power components (DCDC converter & power switches) for UART, JTAG. The system will power up only after the USB HUB has enumerated properly.

Its operation is indicated via the green LED D4 on the motherboard. A 24 MHz crystal (Y3) is required.

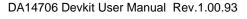

#### 4.2 USB to UART

The USB to UART function is implemented by U12, FT2232HL. This chip is supplied with 3.3 V from U13. A 12 MHz crystal (Y4) is required for the chip operation.

Functions served by U12 are the following:

- Connecting a PC to the UART port of DA1470x SoC

- Connecting a PC to the current sensing circuitry:

- Software cursor triggering (C\_TRIG)

Figure 9: USB to UART (FTDI module)

Figure 10: UART & SWD signals

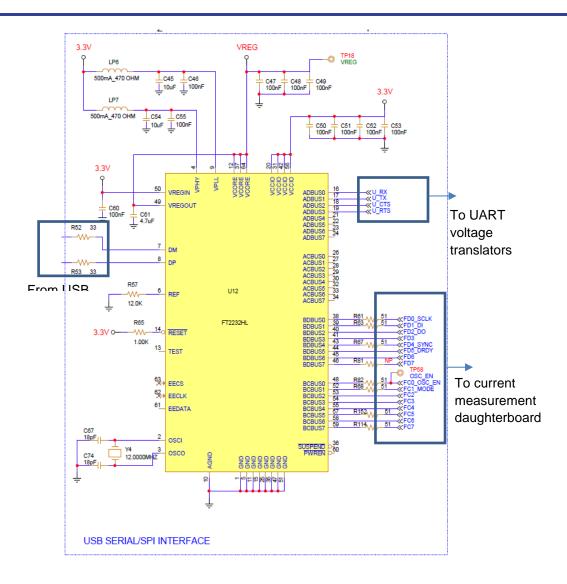

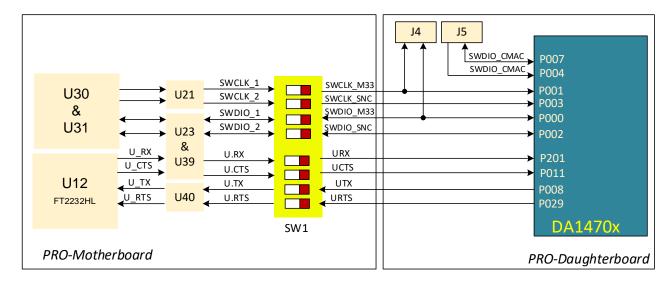

## 4.3 USB to Serial Wire Debug port (SWD)

DA1470x SoC contains three processors, the main processor M33, the SNC and the CMAC. Each of them can be accessed by a SWD port. M33 and SNC are accessed from the debuggers on board (U30 and U31 respectively) which are located on the PRO-Motherboard. CMAC can be accessed by a connector on PRO-Daughterboard.

Figure 11: MK22 debugger schematic (for M33)

The USB to SWD function is implemented by U30 and U31, MK22FN128VMP10. U30/31 are flashed with the J-Link OB firmware. Their operation is indicated via the green LEDs D11/D12. The chips are supplied with 3.3 V from U13.

Functions served by U30 and U31 include:

DA14706 Devkit User Manual Rev.1.00.93

- Connecting a PC to the SWD port of DA1470x SoC

- Reset capability of the DA1470x SoC through the nRST signal

- U30 is used for M33

- U31 is used for the SNC

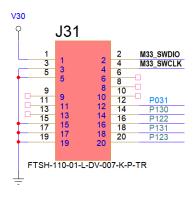

For the M33 processor only, the connector J31 is available to access the Embedded Trace Macrocell (ETM) module via a standard 20-pin high density connector. A J-Link Trace debug probe can be connected to J31 for this purpose.

Figure 12: J-Trace connector for M33

Please notice that TRACE\_DATA\_1 and TRACE\_DATA\_3 are used for buttons K1 and K2.

#### 4.4 Audio Codec section

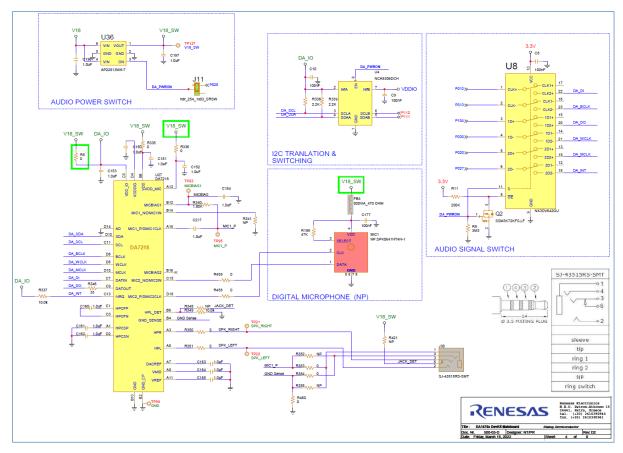

Figure 13: Audio section schematic

DA1470x is equipped with the DA7218 a powerful audio codec with a stereo DAC to headphone output and it contains two analog MIC input paths and two PDM channels.

In this development kit there a placeholder for a digital MIC1 that is **not populated** by default as shown in Figure 13. The power domain of the DA7218 is GPIO controlled via two power switches for optimum power consumption.

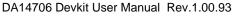

All digital signals between DA1470x and Audio Codec are controlled and can be disabled by an analog switch (U8), this switch is controlled by DA170x's GPIO P028 connected to DA\_PWRON signal alias as shown in Figure 14.

Figure 14: Analog Switch (U8) used to isolate the Digital Audio interface

**Notice:** On DA14706 PRO-Development kit, there is no capability to connect a PDM microphone directly to DA1470x. However, this can be realized by plugging an external PDM microphone break out on break out headers.

#### 4.5 Expansion SPI Connector

Figure 15: Expansion SPI connector (J27)

The SPI signals that can be utilized by the J27 connector are either SPI1/SPI2 (up to 24MHz, Master/Slave) or SPI3 controller (up to 48MHz, master only).

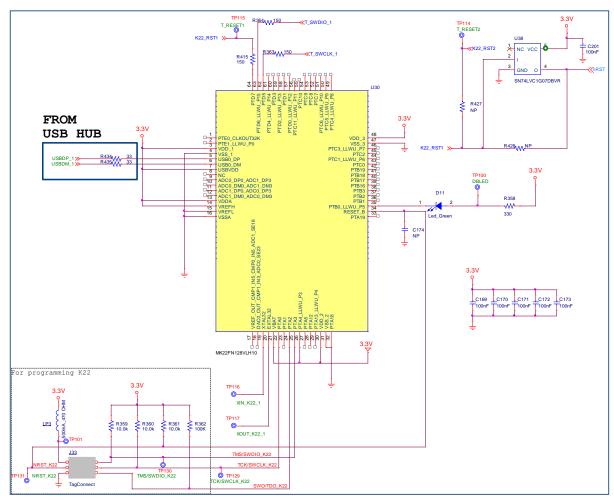

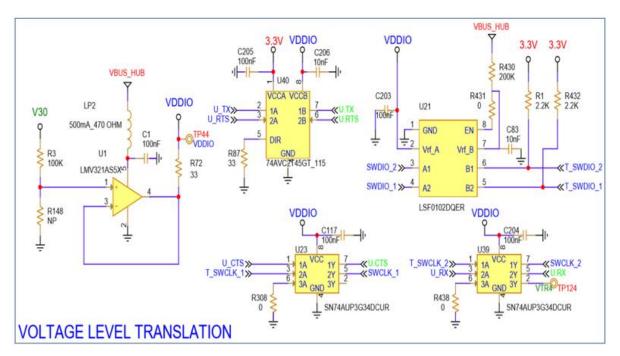

### 4.6 Voltage level translation (debugging) section

Voltage translation is required because the DA1470x I/O voltage will vary depending on the battery level and setting for the I/O LDO. So, if the other side (on board interfaces, JTAG / UART) is fixed at 3.3V, there will be leakage through the pins, e.g. if the DA1470x voltage I/Os are for example at 3.0V or less.

Table 1: Signals with level translation

| Pin name | Signal name  |

|----------|--------------|

| P00      | SWDIO1 (M33) |

| P01      | SWCLK1 (M33) |

| P02      | SWDIO2 (SNC) |

| P03      | SWCLK2 (SNC) |

| P08      | UTX          |

| P201     | URX          |

| P011     | URTS         |

| P029     | UCTS         |

Figure 16: Voltage Level Translation Circuit

- Voltage translation is applied to the UART and JTAG signals. The voltage translation is from 3.3 V to VDDIO and vice versa

- In the SWDIO signals the voltage conversion is made from 3.3V to VDDIO (=V30 by default) VDDIO can be trimmed to lower voltage by populating R148

- V<sub>DDIO</sub> is generated from U1, where V30 from PRO-daughterboard is used as a reference. Consequently, there is no additional power consumption on the power circuitry of DA14706 PRO-Motherboard due to voltage translation

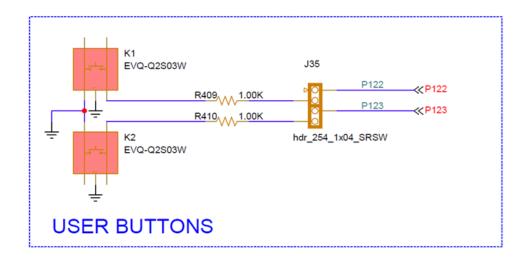

#### 4.7 Push Buttons

- There are two available push buttons, K1 and K2 on DA14706 PRO-Motherboard

- Push buttons are connected to the DA1470x PRO daughterboard for getting user actions by the Application Software K1 button is connected to GPIO signal P122 which is shared with J-trace connector signal TRACE\_DATA\_1

- K2 button is connected to GPIO signal P123 which is shared with J-trace connector signal TRACE\_DATA\_3

- Jumpers at connector J35 should be mounted

Figure 17: Push Buttons used in the DA1470x PRO-Motherboard

# 4.8 GPIO assignment

Table 2: DA14706 PRO-Development kit GPIO pin assignment

| DA1470x GPIO<br>Pin Name | GPIO assignment                                        | Comments                                 |  |

|--------------------------|--------------------------------------------------------|------------------------------------------|--|

| P0_00                    | M33_SWDIO                                              | Available on J4 of PRO-<br>Daughterboard |  |

| P0_01                    | 1 M33_SWDCLK Available on J4 of PRO Daughterboard      |                                          |  |

| P0_02                    | SNC_SWDIO                                              |                                          |  |

| P0_03                    | SNC_SWDCLK                                             |                                          |  |

| P0_04                    | MikroBUS-BRSTn(1)                                      | Multiplexed with CMAC_SWDIO, QSPIC_ON    |  |

| P0_05                    | MikroBUS-(1)                                           |                                          |  |

| P0_06                    | MikroBUS-A(2)/TRIG_0                                   | Multiplexed with TRIG_0                  |  |

| P0_07                    | MikroBUS-BRSTn(2)                                      | CMAC_SWDCLK                              |  |

| P0_08                    | UART Tx (Output)  Available on J4 of PRO-Daughterboard |                                          |  |

| P0_09                    | 09 SPI MISO MikroBU                                    |                                          |  |

| P0_10                    | )_10 LCD_TE LCD_TE signal                              |                                          |  |

| P0_11                    | UART CTSn (input) /NTC supply                          | Multiplexed GPIO                         |  |

| P0_12                    | DA_DI                                                  | DA7218 data                              |  |

| P0_13                    | DA_BCLK                                                | DA7218 BCLK                              |  |

| P0_14                    | SPI SCK                                                | MikroBUS SPI SCK                         |  |

| P0_15                    | SPI MOSI                                               | MikroBUS SPI MOSI                        |  |

| P0_16                    | MikroBUS-RX(2) / LCD_SPI_SD1                           | Multiplexed GPIO                         |  |

| P0_17                    | MikroBUS-TX(2) /LCD_SPI_SD3/TRIG_1                     | Multiplexed GPIO                         |  |

| P0_18                    | MikroBUS-CS(2) / LCD_CS / TRIG_2                       | Multiplexed GPIO                         |  |

| P0_19                    | MikroBUS CS(1) / EXTCOMIN                              | Multiplexed GPIO                         |  |

| P0_20                    | DA_MCLK                                                | MCLK of DA7218 codec                     |  |

| P0_21                    | MIC_PWR1 / TRIG_3                                      | TRIG_3/ Analog MIC supply                |  |

| P0_22                    | MikroBUS-RX(1) / LCD_SPI_SD2                           | Multiplexed GPIO                         |  |

| DA1470x GPIO<br>Pin Name | GPIO assignment                               | Comments                                                                  |  |

|--------------------------|-----------------------------------------------|---------------------------------------------------------------------------|--|

| P0_23                    | MikroBUS-INT(1) / LCD_RED1 Multiplexed GPIO   |                                                                           |  |

| P0_24                    | MikroBUS-INT(2) / LCD_GREEN0 Multiplexed GPIO |                                                                           |  |

| P0_25                    | eMMC_CLK / P025x                              | eMMC daughterboard, dual usage GPIO described in 4.11                     |  |

| P0_26                    | eMMC_CMD / P026x                              | eMMC daughterboard, dual usage GPIO described in 4.11                     |  |

| P0_27                    | DA_INT                                        | DA7218 interrupt signal                                                   |  |

| P0_28                    | DA_PWRON                                      | Controls the power switches of the DA7218 voltage domains                 |  |

| P0_29                    | RTSn (output) / NTC_Sence                     |                                                                           |  |

| P0_30                    | DA_WCLK/TRIG_4                                | DA7218 WCLK signal                                                        |  |

| P0_31                    | TRACE_CLK / TRIG_5                            | Multiplexed GPIO                                                          |  |

| P1_00                    | MikroBUS-PWM(1) / LCD_GREEN1/<br>QSPIC2_ON    | Multiplexed GPIO                                                          |  |

| P1_01                    | MikroBUS-PWM(2) / LCD_BLUE0 Multiplexed GPIO  |                                                                           |  |

| P1_02                    | eMMC_D0 / P102x                               | eMMC module, dual usage GPIO described in 4.11                            |  |

| P1_03                    | TP_INT                                        | Interrupt pin of the LCDs touch controller                                |  |

| P1_04                    | DA_DO                                         | DA7218 data out                                                           |  |

| P1_05                    | PGAp                                          | MIC+                                                                      |  |

| P1_06                    | PGAm                                          | MIC-                                                                      |  |

| P1_07                    | MikroBUS-TX(1) / LCD_FRP /<br>LCD_PWR_EN      | Multiplexed GPIO                                                          |  |

| P1_08                    | eMMC_D3 / P108x                               | eMMC module, dual usage<br>GPIO described in 4.11                         |  |

| P1_09                    | FL_D0 / eMMC_D2                               | SPI_FLASH multiplexed with eMMC module, dual usage GPIO described in 4.11 |  |

| P1_10                    | eMMC_D1                                       | eMMC module, dual usage<br>GPIO described in 4.11                         |  |

| P1_11                    | I3C SDA                                       | I3C data signal                                                           |  |

| DA1470x GPIO<br>Pin Name | GPIO assignment                                              | Comments                                                |  |

|--------------------------|--------------------------------------------------------------|---------------------------------------------------------|--|

| P1_12                    | I3C SCL                                                      | I3C clock signal                                        |  |

|                          |                                                              | QSPI RAM, dual usage GPIO described in 4.9              |  |

| P1_14                    | QSPIC2_D1/P114x                                              | QSPI RAM, dual usage GPIO described in 4.9              |  |

| P1_15                    | QSPIC2_D0, P115x                                             | QSPI RAM, dual usage GPIO described in 4.9              |  |

| P1_16                    | eMMC_D6/P116x                                                | eMMC module, dual usage<br>GPIO described in 4.11       |  |

| P1_17                    | FL_D3/eMMC_D5/P117x                                          | SPI FLASH/eMMC, multi-use<br>GPIO described in 4.11     |  |

| P1_18                    | FL_D2/eMMC_D4,P118x                                          | SPI FLASH/eMMC, multi-use<br>GPIO described in 4.11     |  |

| P1_19                    | P1_19 QSPIC2_CLK,P119x QSPI RAM, dual usage described in 4.9 |                                                         |  |

|                          |                                                              | QSPI RAM, dual usage GPIO described in 4.9              |  |

|                          |                                                              | eMMC module reset, dual usage<br>GPIO described in 4.11 |  |

| P1_22                    | TRACE_DATA[1] / Button 1                                     | on 1                                                    |  |

| P1_23                    | TRACE_DATA[3] / Button 2                                     |                                                         |  |

| P1_24                    | QSPIC2_CS / P124x                                            | QSPI RAM, dual usage GPIO described in 4.9              |  |

| P1_25                    | FL_CS                                                        | SPI FLASH                                               |  |

| P1_26                    | FL_CLK                                                       | SPI FLASH                                               |  |

| P1_27                    | FL_D1                                                        | SPI FLASH                                               |  |

| P1_28                    | EXP_CLK                                                      | CLK signal on the expansion connector J27               |  |

| P1_29                    | EXP_CS CS signal on the expansion connector J27              |                                                         |  |

| P1_30                    | TRACE_DATA[0] /TRIG_6                                        | Multiplexed GPIO                                        |  |

| P1_31                    | RACE_DATA[2] / TRIG_7                                        | Multiplexed GPIO                                        |  |

| DA1470x GPIO<br>Pin Name                             | GPIO assignment                                      | Comments                                          |

|------------------------------------------------------|------------------------------------------------------|---------------------------------------------------|

| P2_00                                                | P2_00 EXP_DI DI signal on the connector J27          |                                                   |

| P2_01                                                | UART RX (input)                                      | Available on J4 of PRO-<br>Daughterboard          |

| P2_02                                                | EXP_D0                                               | D0 signal on the expansion connector J27          |

| P2_03                                                | eMMC_D7/P203x                                        | eMMC module, dual usage<br>GPIO described in 4.11 |

| P2_04                                                | OQSPIF_D4                                            |                                                   |

| P2_05                                                | OQSPIF_D5                                            |                                                   |

| P2_06                                                | OQSPIF_D6                                            |                                                   |

| P2_07                                                | OQSPIF_D7                                            |                                                   |

| P2_08                                                | XTAL 32KHZ                                           |                                                   |

| P2_09                                                | XTAL 32KHZ                                           |                                                   |

| P2_10                                                | USBp                                                 |                                                   |

| P2_11                                                | USBn                                                 |                                                   |

| P2_12                                                | EXP_INT                                              | INT signal on the expansion connector J27         |

| P2_13                                                | P2_13 EXP_GPIO1 GPIO1 on the expansion connector J27 |                                                   |

| P2_14 EXP_GPIO2 GPIO2 on the expansion connector J27 |                                                      | GPIO2 on the expansion connector J27              |

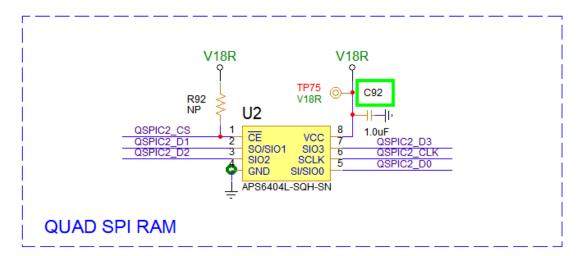

#### 4.9 QSPI-RAM

Figure 18: QSPI RAM schematic

QSPI-RAM may be used in applications where we need bulk data transfers with DMA. The most common case is as LCD frame buffer. On DA14706 PRO-Motherboard, the APS6404L-SQH-SN from APMEMORY is mounted. The memory characteristics are shown below:

- 64 Mbit QSPI RAM memory

- Half Sleep Mode with data retention for 30µA (max) Stand By current

- Operating voltage: 1.65 V to 3.6 V for read, erase and program operations

- SOP-8L (150mils), package

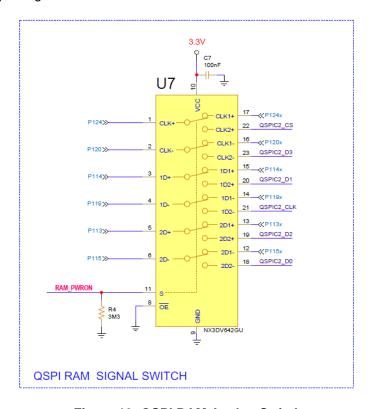

Figure 19: QSPI RAM Analog Switch

The QSPI RAM signals are controlled by an analog switch (see Figure 19), they either connected: to the main SoC DA1470x (when RAM\_PWRON is high) or to the monitoring headers (when RAM\_PWRON is low).

Default state of RAM\_PWRON signal is high.

P113x, P114x, P115x, P119x, P120x, P124x are connected to the monitoring header J4 and they are enabled when signal RAM\_PWRON is low.

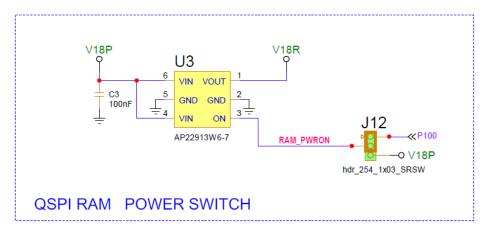

Figure 20: QSPI RAM power switch

In the QSPI-RAM both the power (via power switch U3) and the connectivity of the signals are controlled by jumper block J12 and signal RAM\_PWRON. This control signal can be driven by GPIO P1\_00 (jumper 1-2, Default option), set permanently enabled (jumper 2-3).

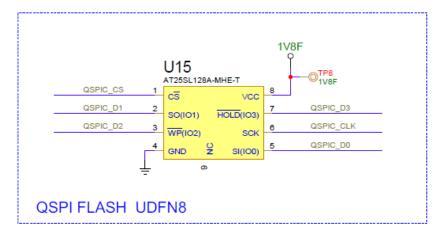

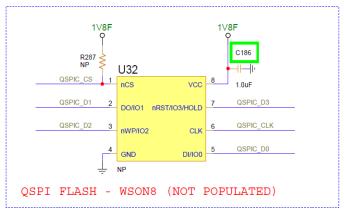

#### 4.10 QSPI FLASH

In this DA14706 PRO-Motherboard, three different footprints are available for the storage flash memory (WSON8, SOIC16 and UDFN8), in order to support a large selection of memories. The default option is the AT25SL128A-MHE-T at a UDFN8 package.

Figure 21: Default QSPI flash AT25SL128A-MHE-T

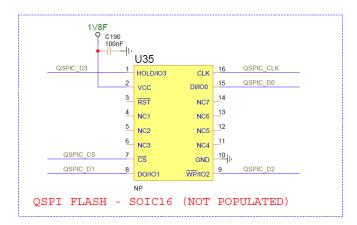

Figure 22: Two QSPI Flash PCB footprint options (not populated)

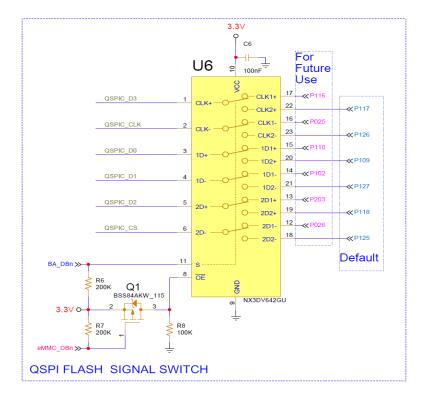

The QSPI flash signals are connected to the DA1470x using an analog switch, as shown in Figure 23. The switch serves two purposes: It selects which group of pins (default or marked as "for future use") will be connected to the QSPI storage flash. This function is controlled by signal BA\_DBn which is hardwired on the daughterboard – default is high. The second function of U6 is to interrupt the signals to the QSPI memory if the eMMC daughterboard is connected, since the eMMC and QSPI memory controllers on the DA1470x share some pins. Signal eMMC\_DBn is grounded on the eMMC daughterboard. When plugged in, the analog switch will disable the output to the QSPI memory via Q1 so only one of the interfaces (QSPI or eMMC) can be selected at a time.

Figure 23: Analog switch (U6) used for the QSPI flash signals

Table 3: U6 truth table

| BA_DBn | eMMC_DBn | QSPI Flash | DA1470x | Comments                           |

|--------|----------|------------|---------|------------------------------------|

| х      | L        | switch     | off     | Use with eMMC through connector J6 |

|        |          | QSPIC_D0   | P110    |                                    |

|        |          | QSPIC_D1   | P102    |                                    |

| L      | н        | QSPIC_D2   | P203    | Use with QSPI Flash,               |

| L      | L        | QSPIC_D3   | P116    | (U15)                              |

|        |          | QSPIC_CS   | P026    |                                    |

|        |          | QSPIC_CLK  | P025    |                                    |

|        |          | QSPIC_D0   | P109    |                                    |

|        |          | QSPIC_D1   | P127    |                                    |

| ш      | н        | QSPIC_D2   | P118    | Reserved for Future                |

| П      |          | QSPIC_D3   | P117    | use                                |

|        |          | QSPIC_CS   | P125    |                                    |

|        |          | QSPIC_CLK  | P126    |                                    |

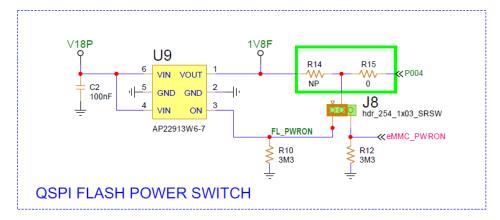

Figure 24: QSPI Flash power switch

The QSPI-Flash power switch U9 is controlled by jumper block J8 and signal FL\_PWRON. FL\_PWRON can be driven by GPIO P0\_04 (jumper 1-2, Default option). When jumper is placed on positions 2-3 of J8 then eMMC\_PWRON control signal is enabled (please see paragraph 4.11) whereas U9 is disabled. If neither the QSPI flash nor the eMMC daughterboard are needed then the jumper on J8 can be removed and both of them will not be powered.

#### J6 ≪eMMC\_DBn P025 O V30 5 6 O VSYS P102 9 10 ≪eMMC\_PWRON 10 12 9 12 11 P117 14 P108 14 16 18 20 13 P118 15 P109 16 18 15 17 17 19 20 P110 19 21 22 P116 21 23 23 24 1775013-2 P025 P025x RN35 P026 6 0 P026x P102 P102x P108 P108x P109 RN36 P109x P110 0 P110x P116 P116x P117 P117x RN37 P118 P118x P121 P121x P203x eMMC DB CONNECTOR

## 4.11 Break-out connector (J6)

Figure 25: eMMC connector schematic

For better flexibility, J6 break-out connector is added on the DA14706 PRO Motherboard. The connector used is the 1775013-2, a 24 positions,0.8 mm, PCB Mount vertical receptacle. User can design a module using the mate connector.

The GPIOs connected on J6 are multiplexed with eMMC bus, providing by this way the capability to test an eMMC memory as well other peripherals.

Also as a number of the signals are shared with QSPI Flash memory, the analog switch U6 should be turned off using the eMMC\_DBn signal as shown in Figure 23.

Please note that in the absence of the eMMC module GPIOs: P025x, P026x, P102x, P108x, P109x, P110x, P116x, P117x P118x, P121x, P203x can be used as generic GPIOs connected to the monitoring header J4.

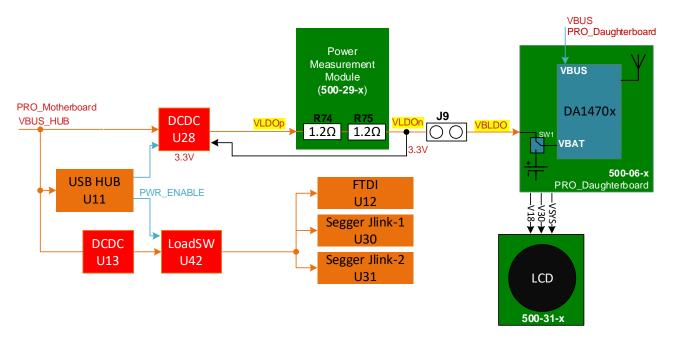

## 4.12 DA14706 PRO-Motherboard power configuration

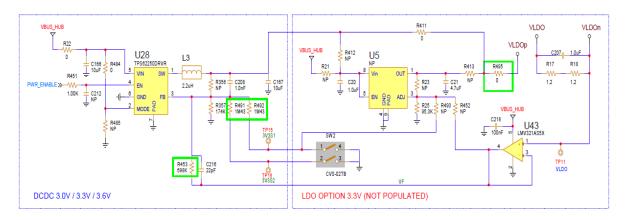

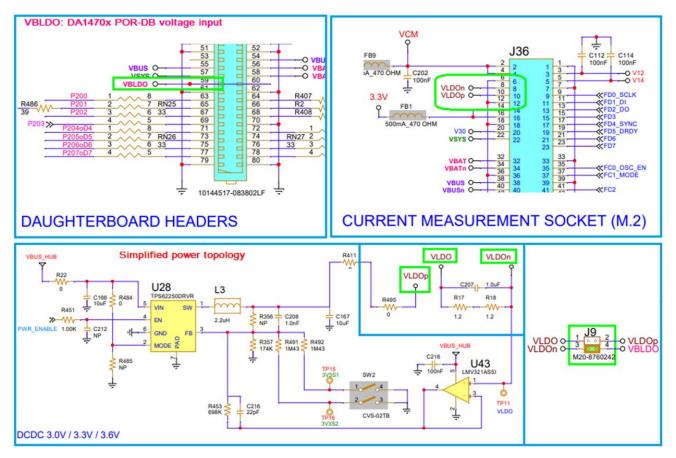

The power structure of the PRO-Motherboard (shown in Figure 26) contains two high efficient adjustable 1A DCDC step down converters the U28 (TPS62250DRVR) and the U13 (AP61100Z6-7) both fed from the USB connector 5V supply (VBUS\_HUB). There is one DCDC allocated per supply domain meaning that there is a dedicated DCDC converter (U28) accompanied with a LDO (U5) for VLDOp voltage generation that passes through the current measurement circuitry and then eventually becoming the VBLDO input supply on the daughterboard section. Please notice that on PRO-Daughterboard, the VBLDO is connected to the VBAT through switch SW1.

LDO is acting as a back up to suppresses any undesired rippling that may appear at the output of the U28 DCDC converter. U5 not populated by default.

Figure 26: Power configuration applied on PRO-Motherboard

The actual schematic of the aforementioned configuration is shown in Figure 27. The DIP switch SW2 used to adjust the DCDC's output voltage from 3.0V to 3.3V and 3.6V.

Figure 27: VLDOp voltage generation

Table 4: SW2 switch voltage settings

Header J9 is added for facilitating the current measurements. Jumper settings of header J9 are presented below on 5.2.2.

The remaining support circuits on the PRO-Motherboard are powered by a 2<sup>nd</sup> DCDC converter that generates the 3.3V supply. This 3.3V power rail is used on:

- USB to SWD (FTDI module)

- Onboard debuggers

- Voltage translation circuit

- Current measurement & LCD header

The signal (PWR\_ENABLE) that triggers the power switch U42 will go high after the hub has successfully enumerated with a USB host.

Figure 28: 3.3V LDO for PRO-Motherboard peripherals

### Important note on DA14706 PRO Devkit power setup

There are two USB ports, one on PRO-Daughterboard and another on the PRO-Motherboard.

As it is appeared on Figure 26, the USB of PRO-Motherboard supplies all supporting circuits as well as the DCDC converter (U28) which supplies PRO-Daughterboard.

In case that the USB port of PRO-Daughterboard is used, it is advised to plug the USB cable on USB port of PRO-Motherboard as well. By this way any possible leakage will be avoided.

# 5 Power measurement circuitry

On DA14706 Development kit, there is a capability of monitoring critical current and voltages of the system. This is implemented with a power measurement circuitry which consists of the power measurement module (PMM2) and the monitoring circuit which resides on the DA14706 PRO-Motherboard. This feature is intended to provide a good visualization of the system current draw and various voltages. It is relatively accurate but please note that for proper measurements an external calibrated instrument shall be used.

#### . PMM2 features are:

- DA1470x current measurement (1uA-500mA @128kHz)

- DA1470x system voltage measurement

- USB and battery charging current measurement

- 8x Digital signals (triggers)

On the host side, PMM2 is supported by the Power Profiler tool of Smart Snippets Toolbox. At the time of writing, the software support is limited to current measurement. The more advanced features of PMM2 will be rolled out gradually in subsequent versions of Smart Snippets Toolbox.

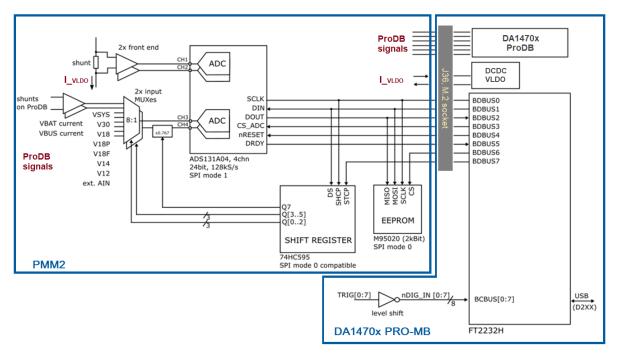

The block diagram of PMM2 is shown in Figure 29. The analog frontend and ADC converter are implemented on the M.2 module, whereas the SPI to USB bridge and digital signals reside on the motherboard.

Figure 29: Power Measurement Module (PMM2) block diagram

An EEPROM is also provided on the module to store production data and allow autodetection from the host software.

RENESAS

## 5.1 The Power measurement circuitry, the monitoring section on PRO-Motherboard

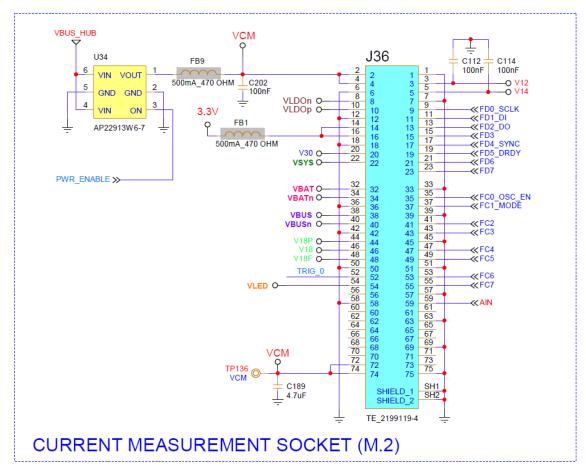

The power measurement module (PMM2) is connected to PRO-Motherboard via J36, M.2 socket. Power to PMM2 is provided from PRO-Motherboard through power switch U34.

Figure 30: Current Measurement socket (M2)

**Table 5: Monitored Power Sources**

| Monitored Magnitude   | Signal          | Comments                                                                                            |

|-----------------------|-----------------|-----------------------------------------------------------------------------------------------------|

| V30                   | V30             | Sourced from PRO-Daughterboard                                                                      |

| VSYS                  | VSYS            | Sourced from PRO-Daughterboard                                                                      |

|                       |                 | Main power rail of the Power management unit                                                        |

| 1.8V                  | V18,            | Sourced from PRO-Daughterboard                                                                      |

|                       | V18P,<br>V18F   | 1.8V rails powering peripherals (V18P), external memories (V18) and XiP flash (V18F) of the DA1470x |

| V14                   | V14             | Sourced from PRO-Daughterboard                                                                      |

|                       |                 | 1.4V rail powering the radio, ADC, PLL and oscillators                                              |

| V12                   |                 | Sourced from PRO- Daughterboard                                                                     |

|                       |                 | 1.2V rail powering the digital core                                                                 |

| VLED                  | VLED            | Sourced from PRO- Daughterboard.                                                                    |

|                       |                 | Boost converter output for supplying white LEDs.                                                    |

| USB charging current  | VBUSp,<br>VBUSn | Sourced from PRO- Daughterboard.                                                                    |

| VBAT charging current | VBATp,          | The current drawn from battery when it is charged. Battery                                          |

|                       | VBATn           | is connected on J6 header and SW1 must be set accordingly on of PRO- Daughterboard.                 |

| VBAT current VLDOp,   |                 | The current drawn from DA1470x system.                                                              |

|                       | VLDOn           | Sourced from PRO-Motherboard.                                                                       |

|                       |                 | Current enters PMM2 from VLDOp (pin 10) and exits from VLDOn                                        |

Figure 31: the hardware setup for current measurements

There are 8 TRIG options defined (TRIG\_0 to TRIG\_7).

As shown in Figure 32 suitable jumper block (J7) allows the user to select directly C\_TRIG (P0\_06) and some other preferred options. Any other GPIO can be used as a trigger source by connecting a TRIG pin on J7 with jumper wire to the desired position at breakout headers (J3..J5).

Figure 32: C\_TRIG selection jumper block (J7) & buffer MOSFETS for I/O levels compatibility

The dual Mosfets Q3..Q6 buffer the signals to provide compatibility with 1.2 to 3.3V I/O levels.

#### 5.2 The power measurement module 2 (PMM2), da1470x-sb-pmm2, (500-29-x)

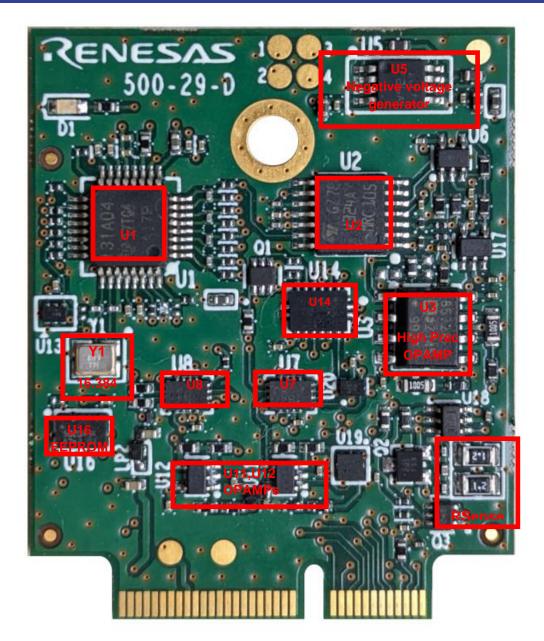

In this DA14706 Development Kit the power measurement module (PMM2) is an external add on board that is interfacing (connected) on the PRO-Motherboard via connector J36.

This is the da1470x-sb-pmm2, 500-29-D or later

Current measurement unit exhibits the following features:

- Full scale range 500mA @ 3.3V

- Measure accurately down to 1uA

- Dedicated hibernation mode to measure down to 100nA

- Current sense resistors

- 2.4 ohm in series to VLDO (located on DA1470x-sb-pmm2, see Figure 26)

- 0.1 ohm in series with VBAT (located on PRO-Daughterboard.)

- 0.1 ohm in series with VBUS (located on PRO-Daughterboard.)

- Analog processing blocks

- Fast quad channel 24-bit ADC with SPI interface

- FTDI chip for transferring data to the PC

- Software trigger circuit

- System voltage measurement

- External analog input 0-5V

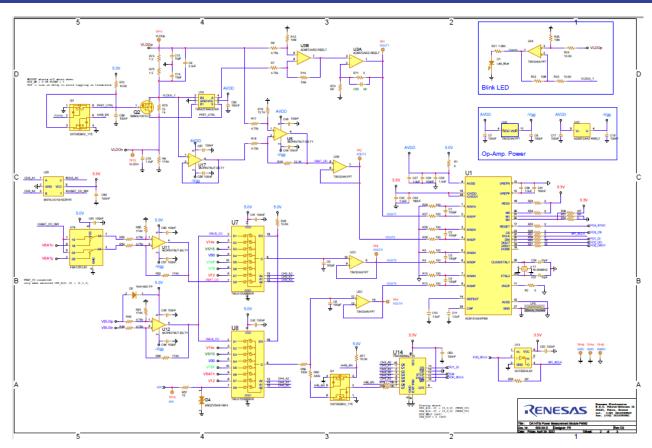

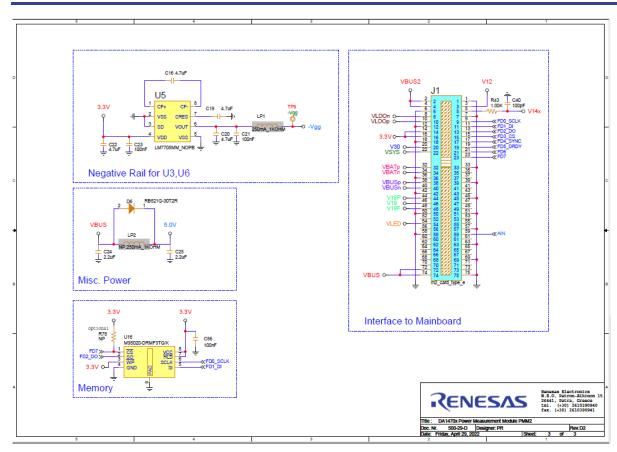

Figure 33: PMM2 current Measurement Circuit PMM2

The input to the circuit is the voltage across the sense resistors R74 and R75. The voltage across the sense resistors is sampled simultaneously by 2 differential amplifier stages and is converted by the ADC to a digital value. The low range has a conversion gain of 5053V/A and covers from 1uA up to about 790uA. The high scale has a conversion gain of 6.114V/A and covers up to about 500mA depending on the VBAT voltage. Both channels are sampled simultaneously, and the host software selects the correct channel using a threshold of 750uA. R9 provides a constant offset which helps avoid the nonlinear region of the low scale. A blue LED serves as a visual indicator of the range. It switches on close to 750uA and allows the user to have a quick indication of the state of the system (on when active, off when sleeping)

Multiplexers U7 and U8 select among the available system voltages and feed channels 3 and 4 of the ADC. A divider formed by R59 and R60 can be selected to allow for 5V input signal range on VSYS and AIN (the full-scale voltage of the ADC is 4V). Two analog front ends around U11 and U12 are provided for measuring the VBUS current and the battery charge current. The switch in front of U11 prevents the leakage current of the differential amplifier stage from VBATp/n to be measured as system current.

A shift register and associated logic control the multiplexers and the rest of the functions of the module. An EEPROM memory is used to store production data and allows the host software to autodetect the module. Charge pump u6 generates a slightly negative voltage (-230mV) to allow the output of the frontend OPAMPs to reach true zero.

Figure 34: PMM2 on board peripherals (Power supply, Memory etc.)

The circuit can be set in a low current measurement mode from the host (hibernation mode), useful in measuring the current of the DA1470x in hibernation (shipping) mode, which is in the order of some 100s of nA. The measurement range of the circuit in this mode is from 100nA to 60uA. This is achieved with a significantly larger sense resistor (R76) which is shorted by Q2 in normal operation. In hibernation mode, Q2 switches off and R76 is placed in series with R74 and R75 forming a 24.4 $\Omega$  sense resistor. The lower sampling point of the low range is moved to the terminals of this series combination with the help of analog switch U18. The high range connections remain unchanged, and it monitors the current through R74 and R75 only. In order to avoid excessive voltage, drop due to the large sense resistor in case the system wakes up draws large currents, the LED indicator output will also override the control of Q2 when the measured current exceeds ~600-700uA. This ensures that the system can wake up normally and its operation is not affected by the hibernation mode.

The offset of the circuit can be calibrated in the Smart Snippets Toolbax software. The procedure necessitates disconnecting the daughterboard either physically or by sliding the daughterboard power selection switch to the right.

Figure 35: Current measurement unit PCBA (TOP)

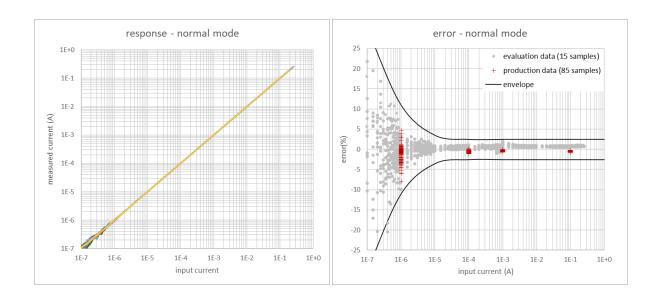

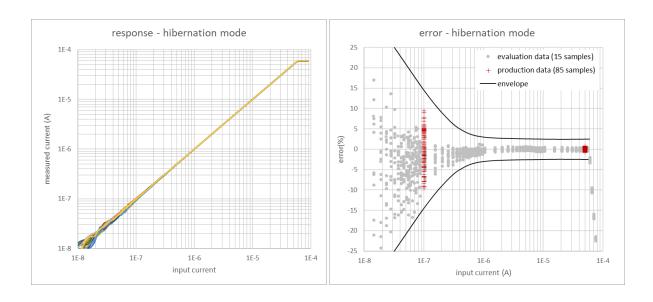

## 5.2.1 Accuracy of current measurement for DA1470x system (VLDO)

The total measuring range of the current measurement circuit of the power measurement module 2 is 100nA to 500mA for VBLDO= 3.3V, implemented into two scales. The current measurement range is covered by two operating modes the default (1 $\mu$ A to 500mA) and the hibernation mode (100nA to 60 $\mu$ A). Switching from default to hibernation mode is done manually over Smart Snippets Toolbox (a version supporting this mode must be used)

The circuit accuracy is measured by applying a constant current, monitoring the same current with an external instrument and the ADC of the PMM2 module and comparing the two. In general, the inaccuracy presented in the current measurement circuit is less than 5% (practically less than 2%) in most of the current range, (Table 6). Note that the values presented in the figures below are averages of multiple points.

**Table 6: Accuracy of the Current Measurement Circuit**

| Current Range  | Current Range Mode Error (%) |       |

|----------------|------------------------------|-------|

| 100 nA to 1 μA | Hibernation mode             | <±10% |

| 1μA το 60uA    | Hibernation mode             | <±5%  |

| 1 μA to 10 μA  | Default mode                 | <±10% |

| 10 μA to 500mA | Default mode                 | <±2%  |

Figure 36: Normal mode (1µA to 500mA at 3.3V) data after offset calibration.

Figure 37: Hibernation mode (100nA to 60uA at 3.3V) data after offset calibration.

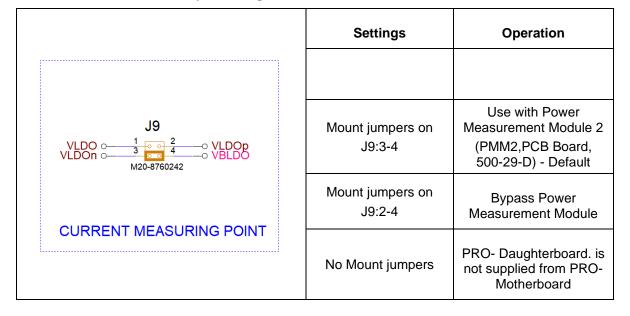

#### 5.2.2 Settings of power configuration header J9

Figure 38: Power connections

Jumper block J9 allows for different configurations as described in **Error! Reference source not found.**. Alternatively, an external current measurement instrument can be connected on these jumpers.

Table 7Jumper setting of current measurement connector J9

## 6 LCD interface and add-on board

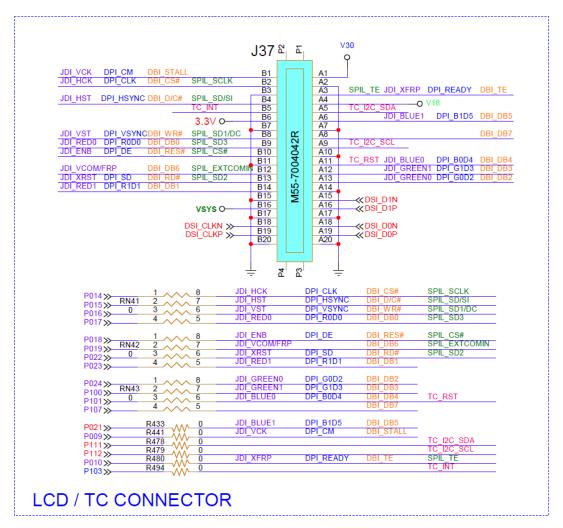

#### 6.1 LCD interface on PRO-Motherboard

Figure 39: Header schematic for LCD daughterboard (Interface board)

The DA14706 PRO Development kit provides LCD support via a dedicated daughterboard (add-on) mounted on the J37 connector on the PRO-Motherboard side. LCD type:

AMOLED display: QSPI, High resolution 390x390 display with touch panel

## 6.2 LCD Amoled board, da1470x-sb-E120A390QSR (500-31-X)

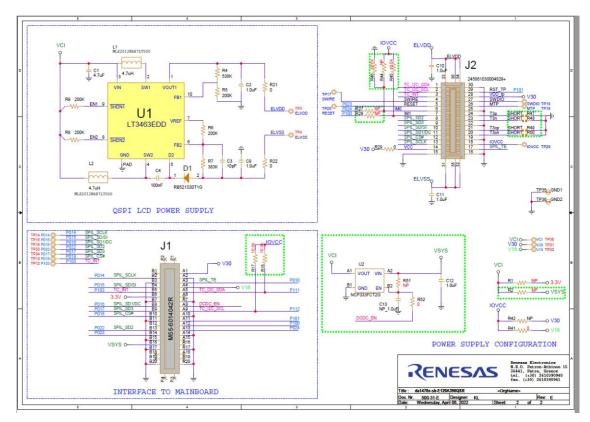

The E120A390QSR, 390x390 AMOLED with capacitive touch has been selected and applied on the LCD add-on, da1470x-sb-E120A390QSR (500-31-D).

Figure 40: LCD add-on daughterboard

U1 is the adjustable DCDC converter LT3463EDDPBF from Analog Devices able to generate positive and negative supplies. Connector J2 provides connectivity with the TFT LCD module while J1 connects this LCD interface (add-on) board with the PRO-Motherboard.

The add-on board is configured for being supplied from VSYS.

E120A390QSR is provided from Panox Displays (https://www.panoxdisplay.com/amoled/1-2-inch-round-oled-390-spi-60hz.html)

Figure 41: QSPI AMOLED LCD daughterboard position on PRO-Development kit

Figure 42: LCD TFT daughterboard top (left) and PCBA bottom side (right)

## 7 PRO Daughterboard

#### 7.1 Main features

The system on DA1470x PRO- Daughterboard. consists of the DA1470x SoC, crystals, power and radio sections. The system block diagram and the actual components location are presented in Figure 43.

The SoC variants that are going to be supported with the DA1470x PRO- Daughterboard. are:

- DA14706 (commercial code: DA14706-00000HZ2), package VFBGA142

- DA14708 (commercial code: DA14708-00000HZ2), package VFBGA142

Block diagram blocks description is given below:

- PRO-Motherboard interface, connectors 2x80pins (J1, J2)

- SWD connector for CMAC/SYS (J4)

- SWD connector for SNC (J5)

- USB mini-B connector

- NOR XiP Flash:

- Quad-SPI Flash (U2X, default)

- Octal-SPI Flash (U2, place holder not populated)

- RGB LED (D1), part number: VLMRGB6112-00-GS08

- Reset push button (B1)

- 3-wire LiPo battery connector (J3, not mounted), part number:147323

- Coin cell holder (BT1 not mounted)

- Power switch (SW1)

- Analog microphone (MIC1)

- RF coaxial switch (J7)

- External analog MIC coaxial switch (J9)

- Printed antenna

Figure 43: System Block Diagram of DA1470x PRO-Daughterboard

Figure 44: PCB top of the DA14706 PRO- Daughterboard.

Figure 45: PCB bottom of the DA1470x PRO- Daughterboard.

Figure 46: PRO- Daughterboard. interface connectors to PRO-Motherboard

## 7.2 Main Components Description

**BLE SoC (U1)**: DA1470x is a BLE SoC family integrating: the latest Arm Cortex M33<sup>TM</sup> application processor, advanced power management functionality allowing the multi power options approach (LiPo, Coincell battery), a Graphic Processing Unit (GPU) for advanced graphics processing, a cryptographic security engine, analog and digital peripherals, a dedicated sensor node controller, and a software configurable protocol engine with a radio that is compliant to the Bluetooth® 5.2 low energy standard.

On Table 8 the DA1470x SoC family is presented. DA14706 and DA14708 are supported on DA14706 Devkit

**Table 8: DA1470x Product Family Differentiation**

| Features                          | DA14701 | DA14705 | DA14706 | DA14708 |  |

|-----------------------------------|---------|---------|---------|---------|--|

| External PSRAM with Data<br>Cache | 1       | ×       | 1       | 1       |  |

| JEITA Charger                     | ×       | 1       | 1       | 1       |  |

| Boost DCDC converter              | ×       | 1       | 1       | 1       |  |

| eMMC                              | 1       | ×       | ×       | 1       |  |

| Rest of features                  | 1       | 1       | 1       | 1       |  |

On the Table 9 below there is a list of the voltage domains either generated (output) by the DA1470x or inserted as inputs.

Table 9: DA1470x SoC Voltage domains

| Voltage rail                                                  | Description                              | Voltage    | Max current capability |

|---------------------------------------------------------------|------------------------------------------|------------|------------------------|

| V <sub>BAT</sub>                                              | Input: Battery supply rail               | 4.75 (Max) |                        |

| V <sub>LED</sub>                                              | Output: LED supply voltage               | 5V (Max)   | 150mA                  |

| V <sub>SYS</sub>                                              | Output: Variable output voltage rail     | 4.8V (Typ) | 1A (Max)               |

| V <sub>30</sub>                                               | Output: 3.0V power rail                  | 3V         | 150mA (Max)            |

| V <sub>12</sub>                                               | Output: 1.2V power rail                  |            | 150mA (Max)            |

| V <sub>14</sub>                                               | Output: 1.4V power rail                  |            | 20mA (Max)             |

| V <sub>14RF</sub> INPUT: Radio supply voltage. Connect to V14 |                                          | 1.4V       |                        |

| V <sub>18</sub>                                               | Output: 1.8V power rail                  |            | 100mA (Max)            |

| V <sub>18F</sub>                                              | V <sub>18F</sub> Output: 1.8V power rail |            | 30mA (Max)             |

| V <sub>18P</sub>                                              | Output: 1.8V power rail                  | 1.8V       | 100mA (Max)            |

| V <sub>BUS</sub>                                              | Input: USB voltage                       | 5V (Typ)   |                        |

32 MHz XTAL (Y1): The main clock of the system is generated from a 32 MHz XTAL which is connected to the internal clock oscillator. The selected crystal for this reference is the XRCGB32M000F1H00R0 of Murata.

**Table 10: XTAL32M Recommended Operating Conditions**

| Parameter                | Description                  | Conditions                          | Min | Тур | Max | Unit         |

|--------------------------|------------------------------|-------------------------------------|-----|-----|-----|--------------|

| F <sub>XTAL</sub> (32M)  | crystal oscillator frequency |                                     |     | 32  |     | MHz          |

| ESR(32M)                 | equivalent series resistance |                                     |     |     | 60  | Ω            |

| C <sub>L</sub> (32M)     | load capacitance             | No external capacitors are required | 5   | 6   | 7   | pF           |

| Frequency<br>Aging       |                              |                                     |     |     | 2   | ppm/Ye<br>ar |

| Δf <sub>XTAL</sub> (32M) | crystal frequency tolerance  |                                     | -10 |     | +10 | ppm          |

| Drive Level              | Maximum Allowable Power      |                                     |     | 150 | 300 | μW           |

| F <sub>XTAL</sub> (32M)  | crystal oscillator frequency |                                     |     | 32  |     | MHz          |

32.768 kHz XTAL (Y2): A crystal of 32.768 kHz is placed on the pins P2\_08 and P2\_09 of DA1470x.

The selected crystal for this reference is the X CM7V-T1A-32.768kHz-7pF-20PPM-TB-QA from Micro Crystal.

**Table 11: XTAL32K Recommended Operating Conditions**

| Parameter                 | Description                  | Conditions | Min | Тур    | Max | Unit |

|---------------------------|------------------------------|------------|-----|--------|-----|------|

| f <sub>CLK_32K</sub>      | clock frequency              |            |     | 32     |     | kHz  |

| fxtal_32K                 | crystal oscillator frequency |            |     | 32.768 |     | kHz  |

| ESR32K                    | equivalent series resistance |            |     | 50     | 70  | kΩ   |

| C <sub>L_32K</sub>        | load capacitance             |            |     | 7      |     | pF   |

| C <sub>0_32K</sub>        | shunt capacitance            |            |     | 1.2    |     | pF   |

| Δf <sub>XTAL_32K</sub>    | crystal frequency tolerance  |            | -20 |        | +20 | ppm  |

| P <sub>DRV_MAX_32</sub> K | Maximum driver power         |            |     |        | 1   | μW   |

#### 7.3 **Debugging** section

The DA1470x provides three SWD ports (M33, SNC and CMAC) and a UART port.

On DA14706 PRO-Devkit, by default, SWD ports for M33 and SNC as well as UART port are accessed through the USB connector of PRO-Motherboard. On Daughterboard two debugging connectors are applied (10 Pos, 1.27mm pitch) one for the CMC/M33 debugging (J4) and one for the SNC debugging (J5). These connectors can provide external access to the corresponded processors.

Figure 47: CMAC/M33 & SNC debugging connectors schematic

#### 7.4 Audio Section

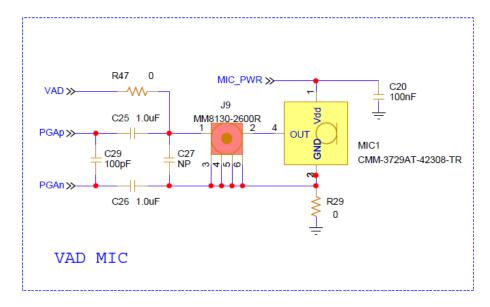

DA1470x SoC has provides a Voice Activity Detection (VAD) engine. VAD engine allows DA1470x SoC to stay in sleep mode until enough audible energy has been sensed to trigger an interrupt assertion and consequently wake up the rest of the SoC. On PRO-Daughterboard, an analog microphone (Mic1) is connected to specific pins of DA1470x. SoC through an analog switch (U5).

VAD mic (MIC1): Analog microphone connected on the VAD pin (analog input of the voice activity Detection Engine), MIC1 part number CMM-3729AT-42308-TR of CUI Devices.

An external microphone can be connected on connector/switch J9 if needed. J9 is the MM8130-2600R of Murata. It is an electromechanical connector used for radio signals.

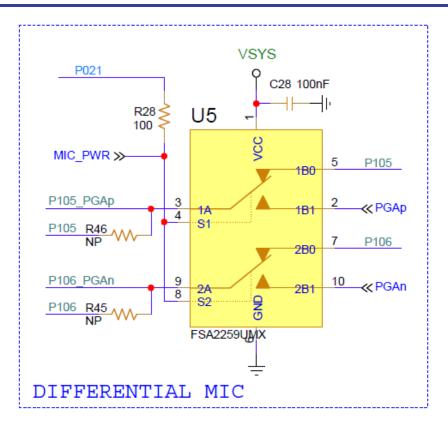

Figure 48: VAD Analog MIC

Differential MIC (U5): Voice Activity Detection (VAD) mic outputs (PGAp, PGAn) as well as outputs from the digital MIC (P105, P106) placed at the PRO-Motherboard are connected in this differential MIC

Figure 49: Programmable gain amplifier signal routing

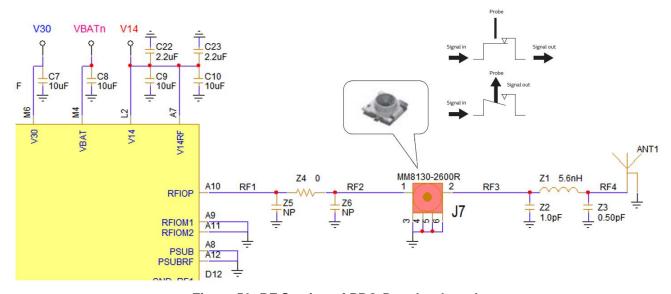

#### 7.5 RF Section

A printed F-antenna (ANT1) is used as the radiating element for the DA1470 PRO-DB.

The DA1470x RFIO pin is connected to the printed antenna through a RF strip line and a matching circuit as shown below:

Figure 50: RF Section of PRO-Daughterboard.

On PRO-Daughterboard, the printed IFA antenna (ANT1) is enabled.

For conducted measurements J7, MM8130-2600R, microwave coaxial connector with a switch, must be used.

The MXHS83QE3000 of Murata (Cable Assembly Coaxial 0.303m SMA to L Type Probe F-M) must be plugged on J7. The antenna is isolated and the RF signals from/to DA1470x is driven over the coaxial cable.

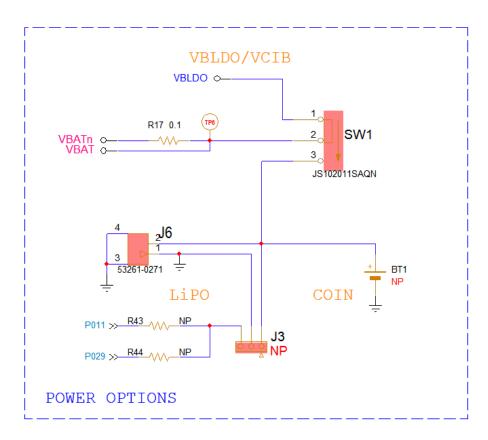

#### 7.6 Power section

Figure 51: PRO-Daughterboard Power options

- Battery/Power connectors (shown in Figure 51):

- o 2-pin connector for Li-Ion/LiPo (J6, default), part number: 53261-0271 (mates with 51021-0200

- Optional Coin cell holder (unpopulated, CR2032 type)

- o Power selector switch (can be used as on-off switch), (SW1)

- o GPIOs P011 and P029 used for NTC supply and NTC sense respectively

The R17 is acting as a current sense for the current measurement unit in case the PRO daughterboard is battery powered.

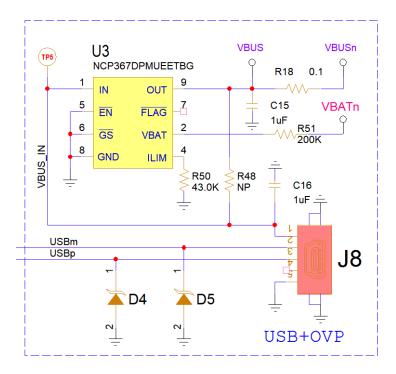

Figure 52: USB OVP protection (U3) & Rsence (R18)

In Figure 52 the OVP protection of the USB is being taken care of the NCP367DPMUEETBG, this device it also offers an overvoltage protection related to the LiPo battery via the VBAT pin.

R18 is acting as sensing resistor when the PRO-MB is powered from the USB connector (VBUS).

#### 7.7 QSPI FLASH

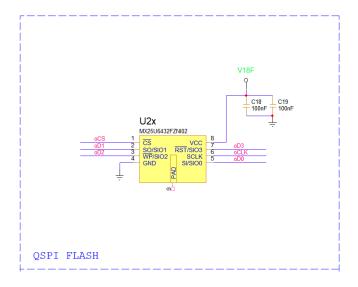

Figure 53: MX25U6432FZNI02 QSPI FLASH schematic

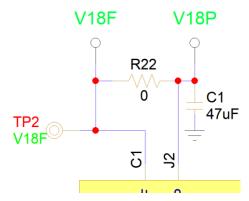

The 64Mbit QSPI flash memory used for storage in the PRO- Daughterboard is the MX25U6432FZNI02 from Macronix. During read the operating current may reach the 80mA level for beyond the V18F current capability of 30mA. In order to ensure that the QSPI flash is properly supplied with sufficient current when operating at 96MHz V18F and V18F are connected together on PRO-Daughterboard.

Figure 54: V18P & V18F are connected through R22

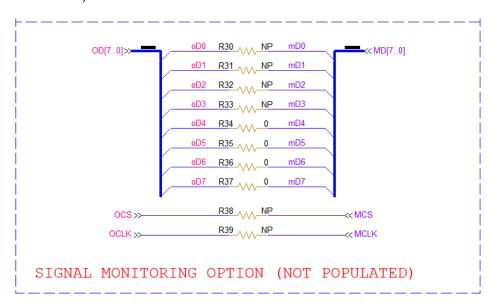

The resistor network consisting of resistors R30 to R37 that is showing below has a twofold purpose: to connect the memory signals on the monitoring headers at the PRO-Motherboard side (shown in section 4) or to have them disconnected (in order for these high speed signal not to travel long distances and cause reflections and interference).

Figure 55: Resistor network for the monitoring signals

Table 12: Flash memory signals to the monitoring headers at PRO-Motherboard

| Flash memory signal | Corresponded GPIO at PRO-MB | Monitoring header at PRO-MB | Direct Connectivity to Monitoring Headers                 |

|---------------------|-----------------------------|-----------------------------|-----------------------------------------------------------|

| oD0                 | oD0                         | J5 (7)                      | Resistor R30 should be mounted, PCB marking see Figure 55 |

|                     |                             |                             | Figure 56                                                 |

| oD1                 | oD1                         | J5 (8)                      | Resistor R31 should be mounted PCB marking see Figure 55  |

| oD2                 | oD2                         | J5 (9)                      | Resistor R32 should be mounted PCB marking see Figure 55  |

| oD3                 | oD3                         | J5 (10)                     | Resistor R33 should be mounted PCB marking see Figure 55  |

| oD4                 | P204oD4                     | J5 (11)                     | Yes                                                       |

| oD5                 | P205oD5                     | J5 (12)                     | Yes                                                       |

| oD6                 | P206oD6                     | J5 (15)                     | Yes                                                       |

| oD7                 | P207oD7                     | J5 (16)                     | Yes                                                       |

| oCS                 | oCS                         | J5 (24)                     | Resistor R38 should be mounted PCB marking see Figure 55  |

| oCLK                | oCLK                        | J5 (28)                     | Resistor R39 should be mounted PCB marking see Figure 55  |

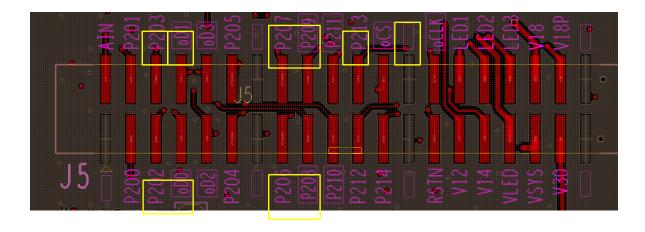

Please note that in the PCB layout the GPIO signals (J5 monitoring header) that need a resistor to be populated in order to connect to the monitoring headers are marked with a surrounding frame as shown below (yellow highlight):

Figure 56: PCB marking of GPIO signals not directly connected to monitoring headers

There is the option for the user to connect a 1Gbit OCTAL NOR flash memory the (MX66UM1G45GXD from Macronix) used for storage. This OCTA flash memory is however, not being populated, along with the correlated monitoring resistors (R30-R33) shown in Figure 57.

Figure 57: MX66UM1G45GXD OSPI FLASH schematic

# 8 Quick Setup

#### 8.1 Hardware setup

<u>Important note</u>: Supplying PRO- Daughterboard, only from USB connector, whereas it is plugged on the PRO-MB which is not powered-on should be avoided.

For proper operation, PRO-Motherboard must be always plugged to source (for e.g. PC, laptop etc.)) through USB. The reason is that a number of circuits (e.g. analog switches, PMM2 module etc) are supplied from the USB connector of the Pro-MB.

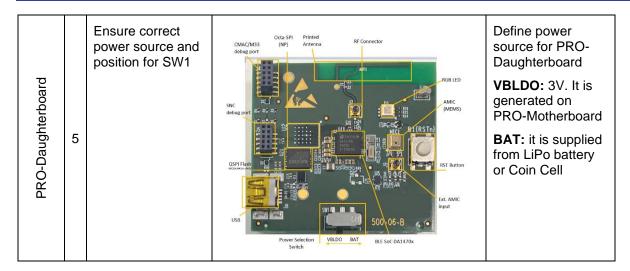

Table 13: DA14706 PRO-Development kit, Quick setup

|                 |   |                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Comments                            |

|-----------------|---|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|                 | 1 | Apply jumper on<br>J9.3 & J9.4                                     | J9 VLDON : 1 2 4 0 VELDO VLDON : 2 4 0 VELDO V | Provide power to<br>PRO Motherboard |