**DAC7611**

# 12-Bit Serial Input DIGITAL-TO-ANALOG CONVERTER

### **FEATURES**

- LOW POWER: 2.5mW

- FAST SETTLING: 7µs to 1 LSB

- 1mV LSB WITH 4.095V FULL-SCALE RANGE

- COMPLETE WITH REFERENCE

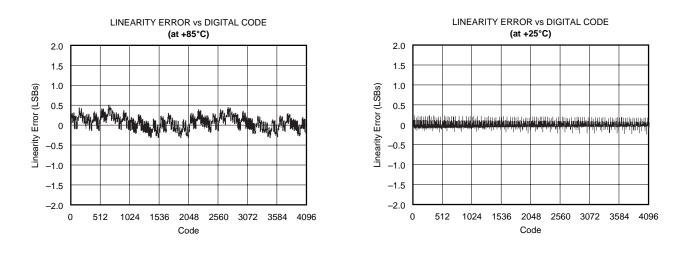

- 12-BIT LINEARITY AND MONOTONICITY OVER INDUSTRIAL TEMP RANGE

- ASYNCHRONOUS RESET TO 0V

- 3-WIRE INTERFACE: Up to 20MHz Clock

- ALTERNATE SOURCE TO DAC8512

### **APPLICATIONS**

- PROCESS CONTROL

- DATA ACQUISITION SYSTEMS

- CLOSED-LOOP SERVO-CONTROL

- PC PERIPHERALS

- PORTABLE INSTRUMENTATION

## DESCRIPTION

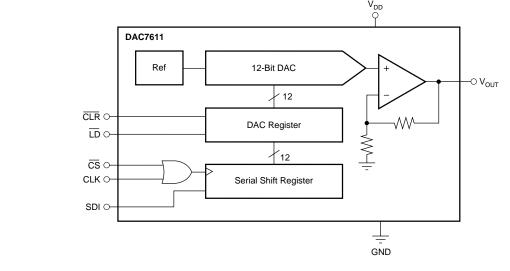

The DAC7611 is a 12-bit digital-to-analog converter (DAC) with guaranteed 12-bit monotonicity performance over the industrial temperature range. It requires a single +5V supply and contains an input shift register, latch, 2.435V reference, DAC, and high speed rail-to-rail output amplifier. For a full-scale step, the output will settle to 1 LSB within 7µs. The device consumes 2.5mW (0.5mA at 5V).

The synchronous serial interface is compatible with a wide variety of DSPs and microcontrollers. Clock (CLK), serial data in (SDI), and load strobe ( $\overline{\text{LD}}$ ) comprise the serial interface. In addition, two control pins provide a chip select ( $\overline{\text{CS}}$ ) function and an asynchronous clear ( $\overline{\text{CLR}}$ ) input. The  $\overline{\text{CLR}}$  input can be used to ensure that the DAC7611 output is 0V on power-up or as required by the application.

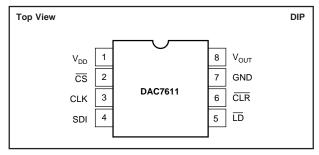

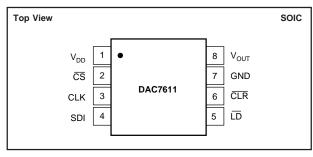

The DAC7611 is available in an 8-lead SOIC or 8-pin plastic DIP package and is fully specified over the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

© 1997 Burr-Brown Corporation

### **SPECIFICATIONS**

#### ELECTRICAL

At  $T_A$  = –40°C to +85°C, and  $V_{DD}$  = +5V, unless otherwise noted.

|                                                                                                                                                             |                                                                                                                                                                                                                      | DAC7611P, U          |                                     | DAC7611PB, UB            |                    |                   |               |                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------|--------------------------|--------------------|-------------------|---------------|---------------------------|

| PARAMETER                                                                                                                                                   | CONDITIONS                                                                                                                                                                                                           | MIN                  | ТҮР                                 | MAX                      | MIN                | TYP               | MAX           | UNITS                     |

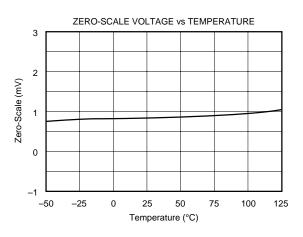

| ACCURACY<br>Resolution<br>Relative Accuracy <sup>(1)</sup><br>Differential Nonlinearity<br>Zero-Scale Error                                                 | Guaranteed Monotonic<br>Code 000 <sub>H</sub>                                                                                                                                                                        | 12<br>-2<br>-1<br>-1 | ±1/2<br>±1/2<br>+1                  | +2<br>+1<br>+3           | *<br>-1<br>-1<br>* | ±1/4<br>±1/4<br>* | +1<br>+1<br>* | Bits<br>LSB<br>LSB<br>LSB |

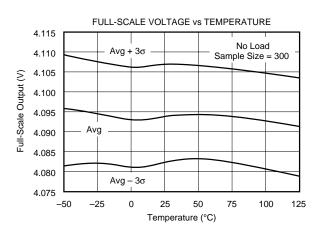

| Full Scale Voltage                                                                                                                                          | Code FFF <sub>H</sub>                                                                                                                                                                                                | 4.079                | 4.095                               | 4.111                    | 4.087              | 4.095             | 4.103         | V                         |

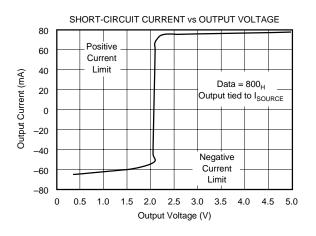

| ANALOG OUTPUT<br>Output Current<br>Load Regulation<br>Capacitive Load<br>Short Circuit Current<br>Short Circuit Duration                                    | $\label{eq:code} \begin{array}{c} \text{Code 800}_{\text{H}} \\ \text{R}_{\text{LOAD}} \geq 402 \Omega, \mbox{ Code 800}_{\text{H}} \\ \text{No Oscillation} \\ \\ \mbox{ GND or } \mbox{V}_{\text{DD}} \end{array}$ | ±5                   | ±7<br>1<br>500<br>±70<br>Indefinite | 3                        | *                  | * * * *           | *             | mA<br>LSB<br>pF<br>mA     |

| DIGITAL INPUT<br>Data Format<br>Data Coding<br>Logic Family                                                                                                 |                                                                                                                                                                                                                      | S                    | Serial<br>traight Bina<br>TTL       | ry                       |                    | * * *             |               |                           |

| Logic Levels<br>V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IH</sub><br>I <sub>IL</sub>                                                                    |                                                                                                                                                                                                                      | 2.4                  |                                     | 0.8<br>±10<br>±10        | *                  |                   | *<br>*<br>*   | V<br>V<br>μΑ<br>μΑ        |

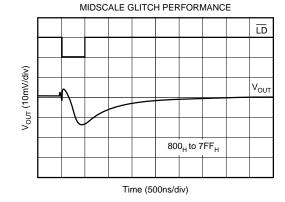

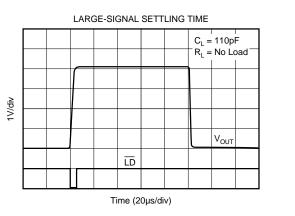

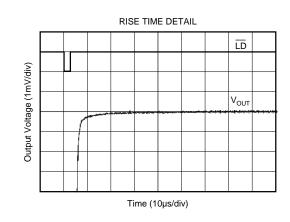

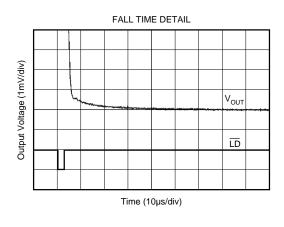

| $\begin{array}{l} \textbf{DYNAMIC PERFORMANCE}\\ \text{Settling Time}^{(2)}\left(t_{S}\right)\\ \text{DAC Glitch}\\ \text{Digital Feedthrough} \end{array}$ | To ±1 LSB of Final Value                                                                                                                                                                                             |                      | 7<br>15<br>2                        |                          |                    | * * *             |               | μs<br>nV-s<br>nV-s        |

| POWER SUPPLY<br>V <sub>DD</sub><br>I <sub>DD</sub><br>Power Dissipation<br>Power Supply Sensitivity                                                         | $\label{eq:VIII} \begin{split} V_{IH} = 5V, \ V_{IL} = 0V, \ \text{No Load, at Code } 000_{H} \\ V_{IH} = 5V, \ V_{IL} = 0V, \ \text{No Load} \\ \Delta V_{DD} = \pm 5\% \end{split}$                                | +4.75                | +5.0<br>0.5<br>2.5<br>0.001         | +5.25<br>1<br>5<br>0.004 | *                  | * * * *           | * * * *       | V<br>mA<br>mW<br>%/%      |

| TEMPERATURE RANGE<br>Specified Performance                                                                                                                  |                                                                                                                                                                                                                      | -40                  |                                     | +85                      | *                  |                   | *             | °C                        |

\* Same specification as for DAC7611P, U.

NOTES: (1) This term is sometimes referred to as Linearity Error or Integral Nonlinearity (INL). (2) Specification does not apply to negative-going transitions where the final output voltage will be within 3 LSBs of ground. In this region, settling time may be double the value indicated.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### **PIN CONFIGURATION**

#### **PIN CONFIGURATION**

#### ABSOLUTE MAXIMUM RATINGS(1)

| V <sub>DD</sub> to GND            | –0.3V to 6V                       |

|-----------------------------------|-----------------------------------|

| Digital Inputs to GND             | 0.3V to V <sub>DD</sub> + 0.3V    |

| V <sub>OUT</sub> to GND           | $-0.3V$ to V <sub>DD</sub> + 0.3V |

| Power Dissipation                 | 325mW                             |

| Thermal Resistance, $\theta_{JA}$ | 150°C/W                           |

| Maximum Junction Temperature      | +150°C                            |

| Operating Temperature Range       | 40°C to +85°C                     |

| Storage Temperature Range         | 65°C to +150°C                    |

| Lead Temperature (soldering, 10s) | +300°C                            |

NOTE: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### PACKAGE/ORDERING INFORMATION

#### PIN DESCRIPTION

| PIN | LABEL            | DESCRIPTION                                                                                                                                                                                                                                           |  |

|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | V <sub>DD</sub>  | Power Supply                                                                                                                                                                                                                                          |  |

| 2   | CS               | Chip Select (active LOW).                                                                                                                                                                                                                             |  |

| 3   | CLK              | Synchronous Clock for the Serial Data Input.                                                                                                                                                                                                          |  |

| 4   | SDI              | Serial Data Input. Data is clocked into the internal serial register on the rising edge of CLK.                                                                                                                                                       |  |

| 5   | ĪD               | Loads the Internal DAC Register. NOTE: The DAC register is a transparent latch and is transparent when $\overline{\text{LD}}$ is LOW (regardless of the state of $\overline{\text{CS}}$ or CLK).                                                      |  |

| 6   | CLR              | Asynchronous Input to Clear the DAC Register. When $\overline{\rm CLR}$ is strobbed LOW, the DAC register is set to $\rm 000_{H}$ and the output voltage to 0V.                                                                                       |  |

| 7   | GND              | Ground                                                                                                                                                                                                                                                |  |

| 8   | V <sub>OUT</sub> | Voltage Output. Fixed output voltage range of approximately 0V to 4.095V (1mV/LSB). The internal reference maintains this output range over time, temperature, and power supply variations (within the values defined in the specifications section). |  |

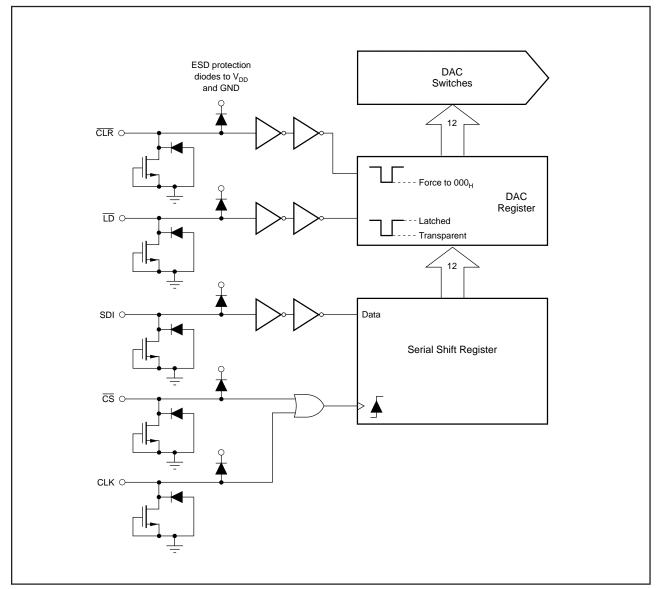

### ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT        | MINIMUM<br>RELATIVE<br>ACCURACY<br>(LSB) | DIFFERENTIAL<br>NONLINEARITY<br>(LSB) | SPECIFICATION<br>TEMPERATURE<br>RANGE | PACKAGE          | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> | ORDERING<br>NUMBER <sup>(2)</sup> | TRANSPORT<br>MEDIA     |

|----------------|------------------------------------------|---------------------------------------|---------------------------------------|------------------|---------------------------------------------|-----------------------------------|------------------------|

| DAC7611P       | ±2                                       | ±1                                    | –40°C to +85°C                        | 8-Pin DIP        | 006                                         | DAC7611P                          | Rails                  |

| DAC7611U       | ±2                                       | ±1                                    | -40°C to +85°C                        | 8-Lead SOIC      | 182                                         | DAC7611U                          | Rails                  |

| "              | "                                        | "                                     | "                                     | "                | "                                           | DAC7611U/2K5                      | Tape and Reel          |

| DAC7611PB      | ±1                                       | ±1                                    | -40°C to +85°C                        | 8-Pin DIP        | 006                                         | DAC7611PB                         | Rails                  |

| DAC7611UB<br>" | ±1<br>"                                  | ±1<br>"                               | –40°C to +85°C<br>"                   | 8-Lead SOIC<br>" | 182<br>"                                    | DAC7611UB<br>DAC7611UB/2K5        | Rails<br>Tape and Reel |

NOTES: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book. (2) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /2K5 indicates 2500 devices per reel). Ordering 2500 pieces of "DAC7611/2K5" will get a single 2500-piece Tape and Reel. For detailed Tape and Reel mechanical information, refer to Appendix B of Burr-Brown IC Data Book.

**DAC7611**

#### **EQUIVALENT INPUT LOGIC**

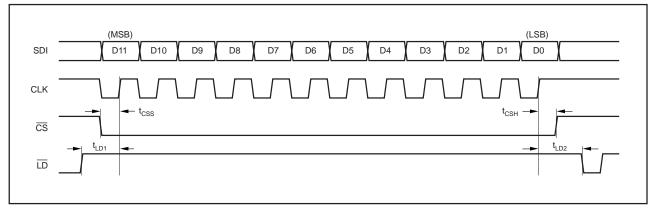

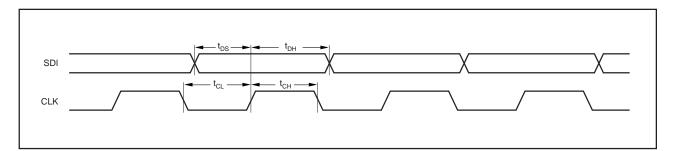

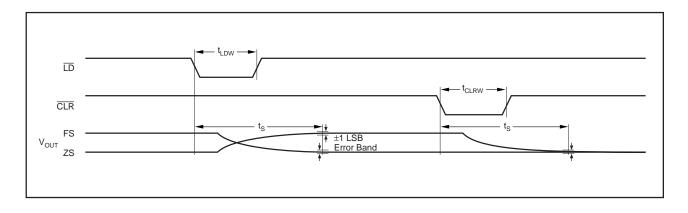

#### **TIMING DIAGRAMS**

#### LOGIC TRUTH TABLE

| CS <sup>(1)</sup> | CLK <sup>(1)</sup>                                                                   | CLR | LD           | SERIAL SHIFT<br>REGISTER | DAC REGISTER                                 |  |

|-------------------|--------------------------------------------------------------------------------------|-----|--------------|--------------------------|----------------------------------------------|--|

| н                 | Х                                                                                    | Н   | н            | No Change                | No Change                                    |  |

| L                 | L                                                                                    | н   | н            | No Change                | No Change                                    |  |

| L                 | н                                                                                    | н   | н            | No Change                | No Change                                    |  |

| L                 | ↑                                                                                    | н   | н            | Advanced One Bit         | No Change                                    |  |

| ↑                 | L                                                                                    | н   | н            | Advanced One Bit         | No Change                                    |  |

| H <sup>(2)</sup>  | Х                                                                                    | н   | $\downarrow$ | No Change                | Changes to Value of<br>Serial Shift Register |  |

| H <sup>(2)</sup>  | Х                                                                                    | н   | L(3)         | No Change                | Transparent                                  |  |

| н                 | Х                                                                                    | L   | Х            | No Change                | Loaded with 000 <sub>H</sub>                 |  |

| н                 | Х                                                                                    | Ŷ   | н            | No Change                | Latched with 000 <sub>H</sub>                |  |

| ↑ Pos             | ↑ Positive Logic Transition; $\downarrow$ Negative Logic Transition; X = Don't Care. |     |              |                          |                                              |  |

NOTES: (1)  $\overline{CS}$  and CLK are interchangeable. (2) A HIGH value is suggested in order to avoid to "false clock" from advancing the shift register and changing the DAC voltage. (3) If data is clocked into the serial register while  $\overline{LD}$  is LOW, the DAC output voltage will change, reflecting the current value of the serial shift register.

#### TIMING SPECIFICATIONS

$T_{A}$  = –40°C to +85°C and  $V_{DD}$  = +5V.

| SYMBOL            | DESCRIPTION       |    | TYP | MAX | UNITS |

|-------------------|-------------------|----|-----|-----|-------|

| t <sub>CH</sub>   | Clock Width HIGH  | 30 |     |     | ns    |

| t <sub>CL</sub>   | Clock Width LOW   | 30 |     |     | ns    |

| t <sub>LDW</sub>  | Load Pulse Width  | 20 |     |     | ns    |

| t <sub>DS</sub>   | Data Setup        | 15 |     |     | ns    |

| t <sub>DH</sub>   | Data Hold         | 15 |     |     | ns    |

| t <sub>CLRW</sub> | Clear Pulse Width | 30 |     |     | ns    |

| t <sub>LD1</sub>  | Load Setup        | 15 |     |     | ns    |

| t <sub>LD2</sub>  | Load Hold         | 10 |     |     | ns    |

| t <sub>CSS</sub>  | Select            | 30 |     |     | ns    |

| t <sub>CSH</sub>  | Deselect          | 20 |     |     | ns    |

NOTE: All input control signals are specified with  $t_R = t_F = 5ns(10\% tb 90\% of +5V)$  and timed from a voltage level of 1.6V. These parameters are guaranteed by design and are not subject to production testing.

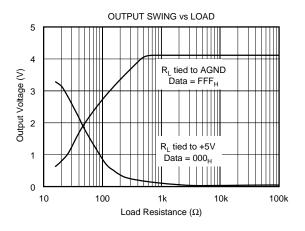

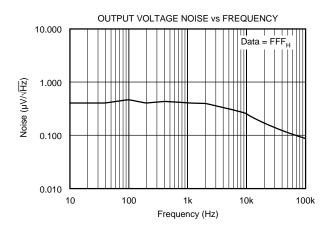

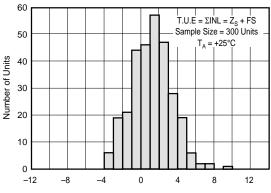

### **TYPICAL PERFORMANCE CURVES**

At  $T_{A}$  = +25°, and  $V_{DD}$  = 5V, unless otherwise specified.

### **TYPICAL PERFORMANCE CURVES (CONT)**

At  $T_A = +25^\circ$ , and  $V_{DD} = 5V$ , unless otherwise specified.

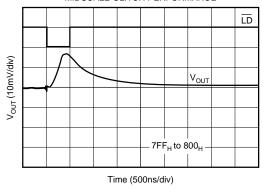

MIDSCALE GLITCH PERFORMANCE

DAC7611

## TYPICAL PERFORMANCE CURVES (CONT)

At T<sub>A</sub> = +25°, and V<sub>DD</sub> = 5V, unless otherwise specified.

LONG-TERM DRIFT ACCELERATED BY BURN-IN 5 120 Units 4 Output Voltage Change (mV) 3 2 1 min 0 avg -1 max -2 -3 -4 -5 0 200 400 600 800 1000 1200 Hours of Operation at +150°C

TOTAL UNADJUSTED ERROR HISTOGRAM

### **TYPICAL PERFORMANCE CURVES (CONT)**

At  $T_A$  = +25°, and  $V_{DD}$  = 5V, unless otherwise specified.

### **OPERATION**

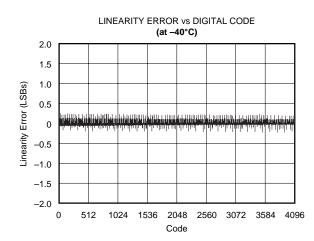

The DAC7611 is a 12-bit digital-to-analog converter (DAC) complete with a serial-to-parallel shift register, DAC register, laser-trimmed 12-bit DAC, on-board reference, and a rail-to-rail output amplifier. Figure 1 shows the basic operation of the DAC7611.

#### INTERFACE

Figure 1 shows the basic connection between a microcontroller and the DAC7611. The interface consists of a serial clock (CLK), serial data (SDI), and a load strobe signal ( $\overline{\text{LD}}$ ). In addition, a chip select ( $\overline{\text{CS}}$ ) input is available to enable serial communication when there are multiple serial devices. The data format is Straight Binary and is loaded MSB-first into the shift registers. An asynchronous

| DAC7611 Full-Scale Range = 4.095V<br>Least Significant Bit = 1mV                                 |                                           |                                                                              |  |  |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|

| DIGITAL INPUT CODE<br>STRAIGHT BINARY                                                            | ANALOG OUTPUT<br>(V)                      | DESCRIPTION                                                                  |  |  |  |  |

| FFF <sub>H</sub><br>801 <sub>H</sub><br>800 <sub>H</sub><br>7FF <sub>H</sub><br>000 <sub>H</sub> | +4.095<br>+2.049<br>+2.048<br>+2.047<br>0 | Full Scale<br>Midscale + 1 LSB<br>Midscale<br>Midscale – 1 LSB<br>Zero Scale |  |  |  |  |

TABLE I. Digital Input Code and Corresponding Ideal

Analog Output.

FIGURE 1. Basic Operation of the DAC7611.

clear input  $(\overline{\text{CLR}})$  is provided to simplify start-up or periodic resets. Table I shows the relationship between input code and output voltage.

The digital data into the DAC7611 is double-buffered. This means that new data can be entered into the DAC without disturbing the old data and the analog output of the converter. At some point after the data has been entered into the serial shift register, this data can be transferred into the DAC register. This transfer is accomplished with a HIGH to LOW transition of the LD pin. However, the LD pin makes the DAC register transparent. If new data is shifted into the shift register while LD is LOW, the DAC output voltage will change as each new bit is entered. To prevent this, LD must be returned HIGH prior to shifting in new serial data.

At any time, the contents of the DAC register can be set to  $000_{\rm H}$  (analog output equals 0V) by taking the  $\overline{\rm CLR}$  input LOW. The DAC register will remain at this value until  $\overline{\rm CLR}$  is returned HIGH and  $\overline{\rm LD}$  is taken LOW to allow the contents of the shift register to be transferred to the DAC register. If  $\overline{\rm LD}$  is LOW when  $\overline{\rm CLR}$  is taken LOW, the DAC register will be set to  $000_{\rm H}$  and the analog output driven to 0V. When  $\overline{\rm CLR}$  is returned HIGH, the DAC register will be set to the current value in the serial shift register and the analog output will respond accordingly.

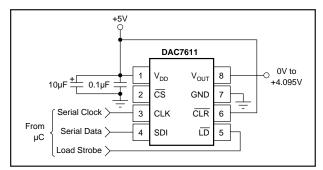

#### DIGITAL-TO-ANALOG CONVERTER

The internal DAC section is a 12-bit voltage output device that swings between ground and the internal reference voltage. The DAC is realized by a laser-trimmed R-2R ladder network which is switched by N-channel MOSFETs. The DAC output is internally connected to the rail-to-rail output operational amplifier.

#### **OUTPUT AMPLIFIER**

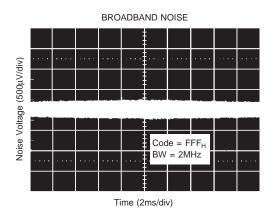

A precision, low-power amplifier buffers the output of the DAC section and provides additional gain to achieve a 0 to 4.095V range. The amplifier has low offset voltage, low noise, and a set gain of 1.682V/V (4.095/2.435). See Figure 2 for an equivalent circuit schematic of the analog portion of the DAC7611.

FIGURE 2. Simplified Schematic of Analog Portion.

The output amplifier has a  $7\mu s$  typical settling time to  $\pm 1$  LSB of the final value. Note that there are differences in the settling time for negative-going signals versus positive-going signals.

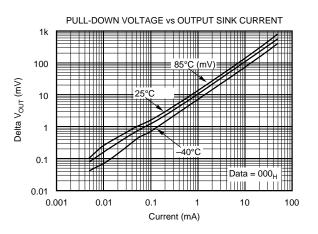

The rail-to-rail output stage of the amplifier provides the full-scale range of 0V to 4.095V while operating on a supply voltage as low as 4.75V. In addition to its ability to drive resistive loads, the amplifier will remain stable while driving capacitive loads of up to 500pF. See Figure 3 for an equivalent circuit schematic of the amplifier's output driver and the Typical Performance Curves section for more information regarding settling time, load driving capability, and output noise.

FIGURE 3. Simplified Driver Section of Output Amplifier.

#### **POWER SUPPLY**

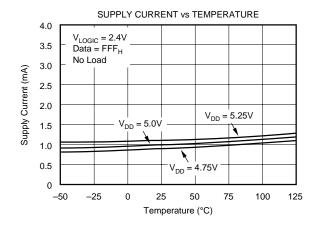

A BiCMOS process and careful design of the bipolar and CMOS sections of the DAC7611 result in a very low power device. Bipolar transistors are used where tight matching and low noise are needed to achieve analog accuracy, and CMOS transistors are used for logic, switching functions and for other low power stages.

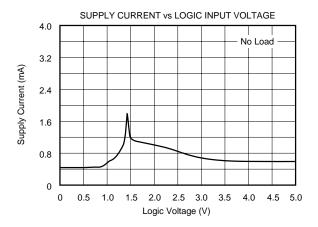

If power consumption is critical, it is important to keep the logic levels on the digital inputs (SDI, CLK,  $\overline{CS}$ ,  $\overline{LD}$ ,  $\overline{CLR}$ ) as close as possible to either  $V_{DD}$  or ground. This will keep the CMOS inputs (see "Supply Current vs Logic Input Voltages" in the Typical Performance Curves) from shunting current between  $V_{DD}$  and ground. Thus, CMOS logic levels rather than TTL logic levels, are strongly recommended for driving the DAC7611.

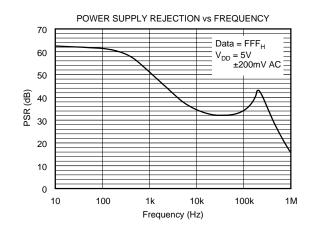

The DAC7611 power supply should be bypassed as shown in Figure 1. The bypass capacitors should be placed as close to the device as possible, with the 0.1uF capacitor taking priority in this regard. The Power Supply Rejection vs Frequency graph in the Typical Performance Curves section shows the PSRR performance of the DAC7611. This should be taken into account when using switching power supplies or DC/DC converters.

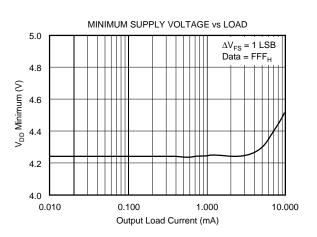

In addition to offering guaranteed performance with  $V_{DD}$  in the 4.75V to 5.25V range, the DAC7611 will operate with reduced performance down to 4.5V. Operation between 4.5V and 4.75V will result in longer settling time, reduced performance, and current sourcing capability. Consult the  $V_{DD}$  vs Load Current graph in the Typical Performance Curves section for more information.

### **APPLICATIONS**

#### POWER AND GROUNDING

The DAC7611 can be used in a wide variety of situations from low power, battery operated systems to large-scale industrial process control systems. In addition, some applications require better performance than others, or are particularly sensitive to one or two specific parameters. This diversity makes it difficult to define definite rules to follow concerning the power supply, bypassing, and grounding. The following discussion must be considered in relation to the desired performance and needs of the particular system.

A precision analog component requires careful layout, adequate bypassing, and a clean, well-regulated power supply. As the DAC7611 is a single-supply, +5V component, it will often be used in conjunction with digital logic, microcontrollers, microprocessors, and digital signal processors. The more digital logic present in the design and the higher the switching speed, the more difficult it will be to achieve good performance.

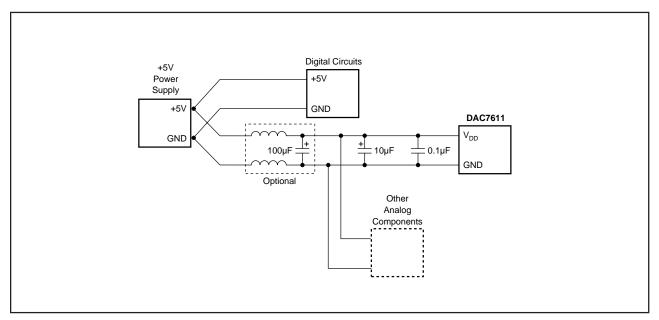

Because the DAC7611 has a single ground pin, all return currents, including digital and analog return currents, must flow through this pin. The GND pin is also the ground reference point for the internal bandgap reference. Ideally, GND would be connected directly to an analog ground plane. This plane would be separate from the ground connection for the digital components until they are connected at the power entry point of the system (see Figure 4).

The power applied to  $V_{DD}$  should be well regulated and lownoise. Switching power supplies and DC/DC converters will often have high-frequency glitches or spikes riding on the output voltage. In addition, digital components can create similar high frequency spikes as their internal logic switches states. This noise can easily couple into the DAC output voltage through various paths between  $V_{DD}$  and  $V_{OUT}$ .

**DAC7611**

As with the GND connection,  $V_{DD}$  should be connected to a +5V power supply plane or trace that is separate from the connection for digital logic until they are connected at the power entry point. In addition, the 10µF and 0.1µF capacitors shown in Figure 4 are strongly recommended and should be installed as close to  $V_{DD}$  and ground as possible. In some situations, additional bypassing may be required such as a 100µF electrolytic capacitor or even a "Pi" filter made up of inductors and capacitors—all designed to essentially lowpass filter the +5V supply, removing the high frequency noise (see Figure 4).

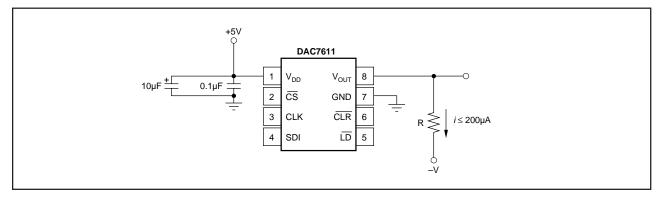

#### OFFSET ERROR MEASUREMENT

As with most DACs, the DAC7611 can have an offset error (or zero scale error) which is either negative or positive. If the error is positive, the output voltage for an input code of  $000_{\rm H}$  will be greater than 0V. If the error is negative, the output voltage is below 0V. However, since the DAC7611 is a single-supply device and cannot swing below ground, the output voltage will be 0V, giving the impression that the offset error is zero.

Since measuring the offset error on a DAC is such a common task, a method is needed to reliably measure the offset error of the DAC7611. This can easily be done as shown in Figure 5. The resistor between  $V_{OUT}$  and a negative voltage provides the output amplifier some ability to swing below ground.

FIGURE 4. Suggested Power and Ground Connections for a DAC7611 Sharing a +5V Supply with a Digital System.

FIGURE 5. Offset Error Measurement Circuit.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated