### Product Change Notification / SYST-30NOPZ312

| D | a | t | ۵ | • |

|---|---|---|---|---|

| u | a | L | ᆮ | • |

02-Oct-2020

### **Product Category:**

8-bit Microcontrollers

# **PCN Type:**

**Document Change**

# **Notification Subject:**

Data Sheet - PIC16(L)F1717/8/9 Cost Effective 8-Bit Intelligent Analog Flash MCU Data Sheet Document Revision

### **Affected CPNs:**

SYST-30NOPZ312\_Affected\_CPN\_10022020.pdf SYST-30NOPZ312\_Affected\_CPN\_10022020.csv

### **Notification Text:**

SYST-30NOPZ312

Microchip has released a new Product Documents for the PIC16(L)F1717/8/9 Cost Effective 8-Bit Intelligent Analog Flash MCU Data Sheet of devices. If you are using one of these devices please read the document located at PIC16(L)F1717/8/9 Cost Effective 8-Bit Intelligent Analog Flash MCU Data Sheet.

Notification Status: Final

#### **Description of Change:**

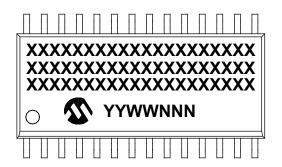

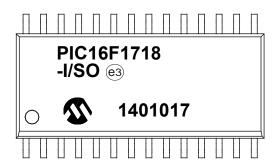

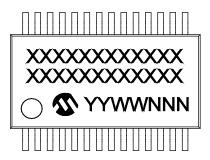

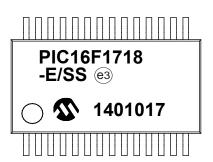

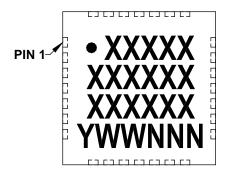

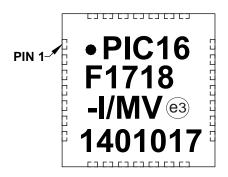

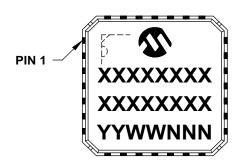

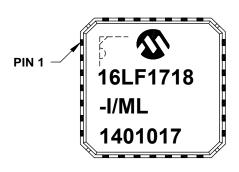

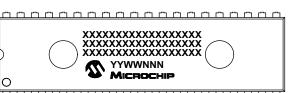

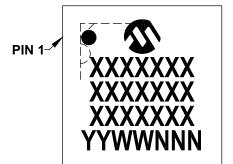

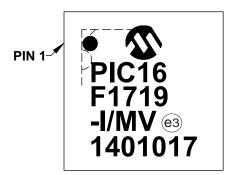

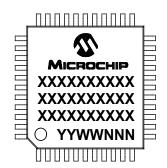

- 1) Updated Table 34-6, the Package Marking Information, and the Product Identification System page.

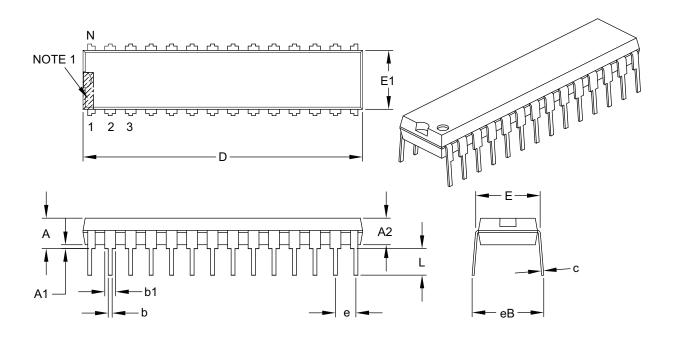

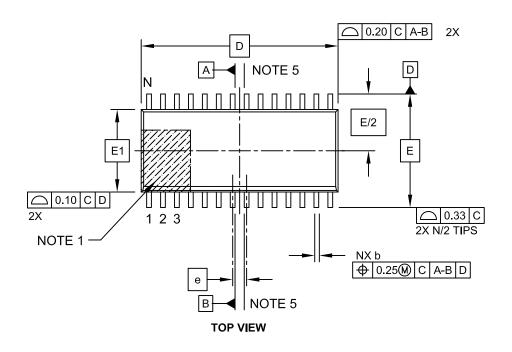

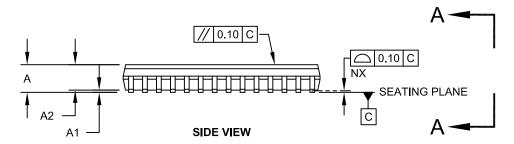

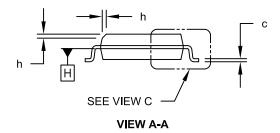

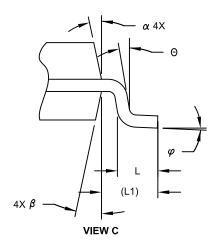

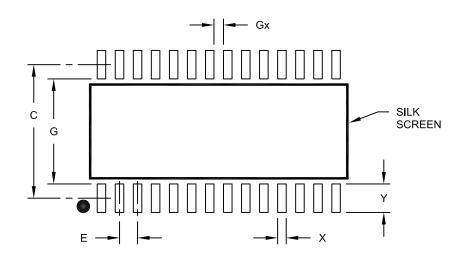

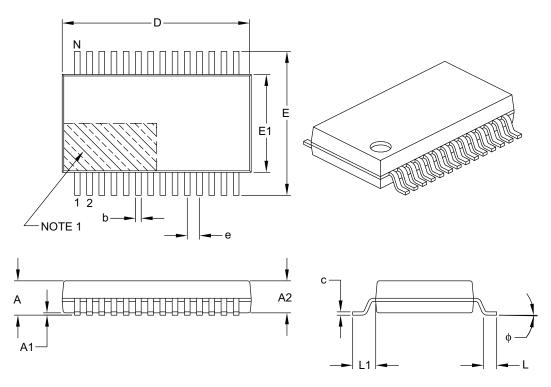

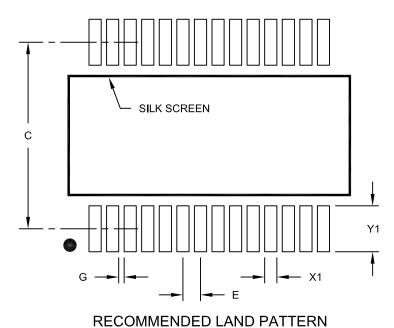

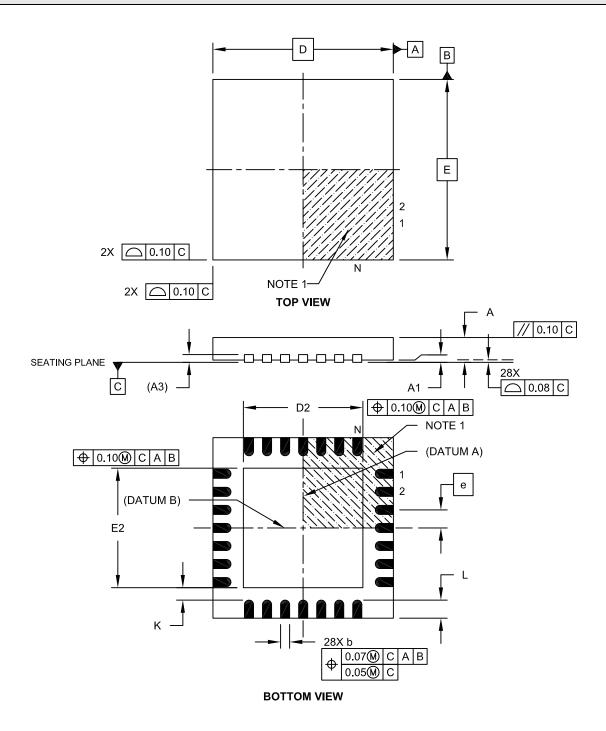

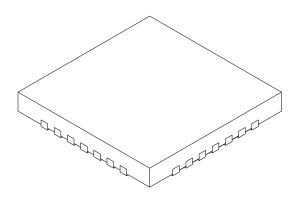

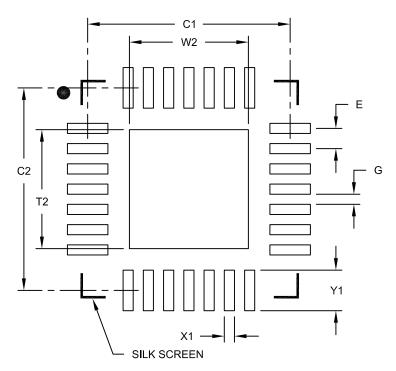

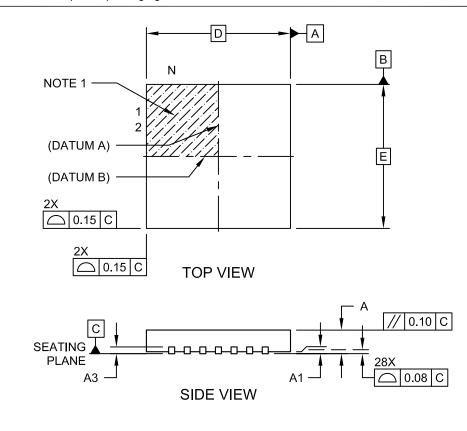

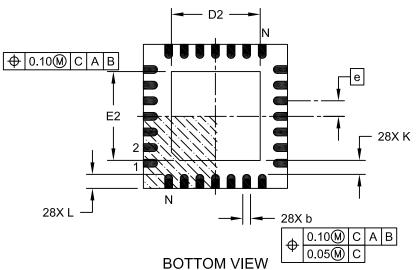

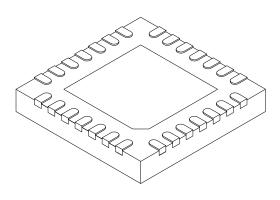

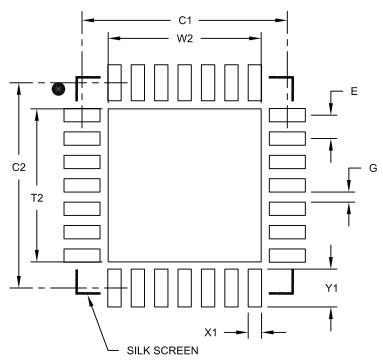

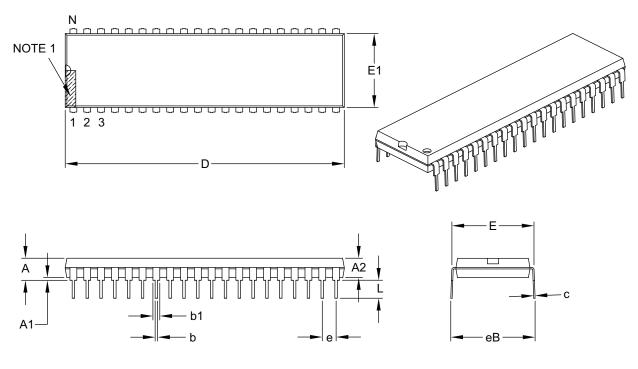

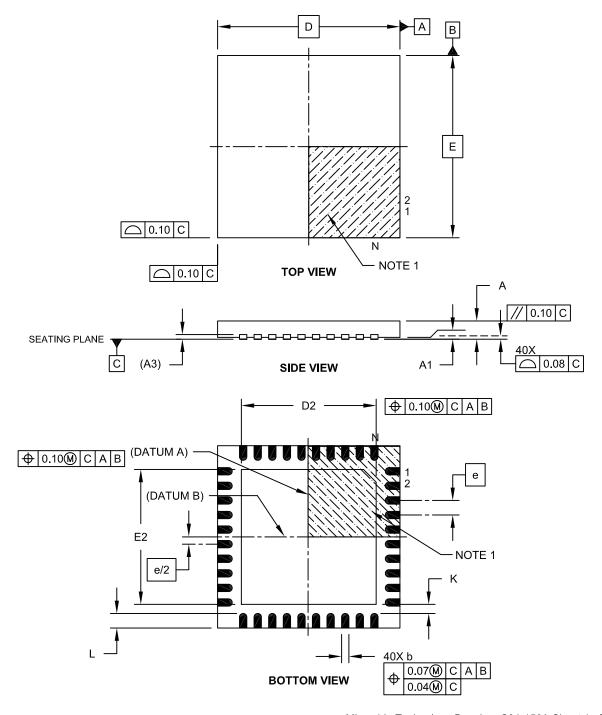

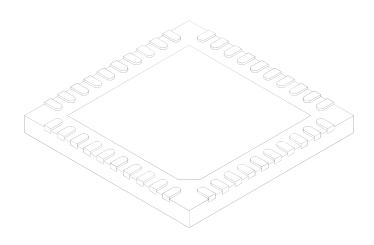

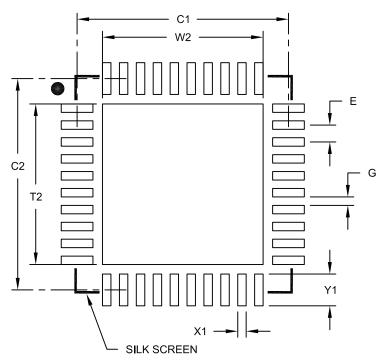

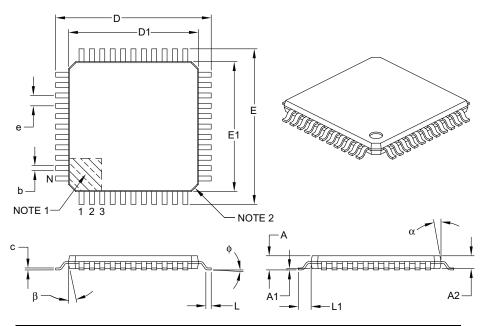

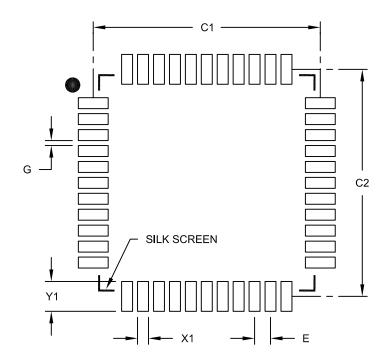

- 2) Replaced three Packaging Information images.

Impacts to Data Sheet: None

Reason for Change: To Improve Productivity

Change Implementation Status: Complete

**Date Document Changes Effective:** 02 Oct 2020

NOTE: Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

## **Attachments:**

PIC16(L)F1717/8/9 Cost Effective 8-Bit Intelligent Analog Flash MCU Data Sheet

Please contact your local Microchip sales office with questions or concerns regarding this notification.

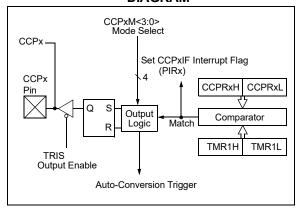

### **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN</u> home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section.

If you wish to <u>change your PCN profile</u>, <u>including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.

$SYST-30NOPZ312-Data\ Sheet-PIC16(L)F1717/8/9\ Cost\ Effective\ 8-Bit\ Intelligent\ Analog\ Flash\ MCU\ Data\ Sheet\ Document\ Revision$

### Affected Catalog Part Numbers (CPN)

PIC16F1717-E/ML

PIC16F1717-E/MV

PIC16F1717-E/P

PIC16F1717-E/PT

PIC16F1717-I/MV

PIC16F1717-I/P

PIC16F1717-I/PT

PIC16F1717T-E/MVVAO

PIC16F1717T-I/ML

PIC16F1717T-I/MV

PIC16F1717T-I/PT

PIC16F1718-E/ML

PIC16F1718-E/MV

PIC16F1718-E/SO

PIC16F1718-E/SP

PIC16F1718-E/SS

PIC16F1718-I/ML

PIC16F1718-I/MLVAO

PIC16F1718-I/MV

PIC16F1718-I/SO

PIC16F1718-I/SP

PIC16F1718-I/SS

PIC16F1718T-E/MV

PIC16F1718T-I/ML

PIC16F1718T-I/MLVAO

PIC16F1718T-I/MV

PIC16F1718T-I/SO

PIC16F1718T-I/SS

PIC16F1718T-I/SS020

PIC16F1718T-I/SSC01

PIC16F1719-E/ML

PIC16F1719-E/MV

PIC16F1719-E/P

PIC16F1719-E/PT

PIC16F1719-E/PTVAO

PIC16F1719-I/ML

PIC16F1719-I/MV

PIC16F1719-I/P

PIC16F1719-I/PT

PIC16F1719-ME2/PF

PIC16F1719T-E/PTVAO

PIC16F1719T-I/ML

PIC16F1719T-I/MV

PIC16F1719T-I/PT

PIC16LF1717-E/ML

PIC16LF1717-E/MV

Date: Thursday, October 01, 2020

| SYST-30NOPZ312 - Data Sheet - PIC16(L)F1717/8/9 Cost Effective 8-Bit Intelligent Analog Flash MCU Data Sheet Document Revision |

|--------------------------------------------------------------------------------------------------------------------------------|

| PIC16LF1717-E/P                                                                                                                |

| PIC16LF1717-E/PT                                                                                                               |

| PIC16LF1717-I/MV                                                                                                               |

| PIC16LF1717-I/P                                                                                                                |

| PIC16LF1717-I/PT                                                                                                               |

| PIC16LF1717T-I/ML                                                                                                              |

| PIC16LF1717T-I/MV                                                                                                              |

| PIC16LF1717T-I/PT                                                                                                              |

| PIC16LF1718-E/ML                                                                                                               |

| PIC16LF1718-E/MV                                                                                                               |

| PIC16LF1718-E/SO                                                                                                               |

| PIC16LF1718-E/SS                                                                                                               |

| PIC16LF1718-I/ML                                                                                                               |

| PIC16LF1718-I/MV                                                                                                               |

| PIC16LF1718-I/SO                                                                                                               |

| PIC16LF1718-I/SP                                                                                                               |

| PIC16LF1718-I/SS                                                                                                               |

| PIC16LF1718T-I/ML                                                                                                              |

| PIC16LF1718T-I/MV                                                                                                              |

| PIC16LF1718T-I/SO                                                                                                              |

| PIC16LF1718T-I/SS                                                                                                              |

| PIC16LF1718T-I/SSV01                                                                                                           |

| PIC16LF1719-E/ML                                                                                                               |

| PIC16LF1719-E/MV                                                                                                               |

| PIC16LF1719-E/P                                                                                                                |

| PIC16LF1719-E/PT                                                                                                               |

| PIC16LF1719-I/ML                                                                                                               |

| PIC16LF1719-I/MV                                                                                                               |

| PIC16LF1719-I/P                                                                                                                |

| PIC16LF1719-I/PT                                                                                                               |

| PIC16LF1719T-I/ML                                                                                                              |

| PIC16LF1719T-I/MV                                                                                                              |

| PIC16LF1719T-I/PT                                                                                                              |

|                                                                                                                                |

|                                                                                                                                |

|                                                                                                                                |

|                                                                                                                                |

|                                                                                                                                |

|                                                                                                                                |

|                                                                                                                                |

|                                                                                                                                |

|                                                                                                                                |

|                                                                                                                                |

|                                                                                                                                |

|                                                                                                                                |

Date: Thursday, October 01, 2020

# **Cost-Effective 8-Bit Intelligent Analog Flash Microcontrollers**

### **Description:**

PIC16(L)F1717/8/9 microcontrollers combine Intelligent Analog integration with low cost and extreme low power (XLP) to suit a variety of general purpose applications. These 28-pin and 40-pin devices deliver on-chip op amps, Core Independent Peripherals (CLC, NCO and COG), Peripheral Pin Select and Zero-Cross Detect, providing for increased design flexibility.

#### **Core Features:**

- · C Compiler Optimized RISC Architecture

- · Only 49 Instructions

- · Operating Speed:

- 0-32 MHz clock input

- 125 ns minimum instruction cycle

- Interrupt Capability

- 16-Level Deep Hardware Stack

- Up to Four 8-Bit Timers

- · One 16-Bit Timer

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Low-Power Brown-out Reset (LPBOR)

- Programmable Watchdog Timer (WDT) up to 256s

- · Programmable Code Protection

#### Memory:

- · Up to 16 Kwords Flash Program Memory

- Up to 2048 Bytes Data SRAM Memory

- · Direct, Indirect and Relative Addressing modes

- High-Endurance Flash (HEF):

- 128B of nonvolatile data storage

- 100K Erase/Write cycles

### **Operating Characteristics:**

- · Operating Voltage Range:

- 1.8V to 3.6V (PIC16LF1717/8/9)

- 2.3V to 5.5V (PIC16F1717/8/9)

- · Temperature Range:

- Industrial: -40°C to 85°C

- Extended: -40°C to 125°C

### eXtreme Low-Power (XLP) Features:

- Sleep mode: 50 nA @ 1.8V, typical

- Watchdog Timer: 500 nA @ 1.8V, typical

- Secondary Oscillator: 500 nA @ 32 kHz

- Operating Current:

- 8 uA @ 32 kHz, 1.8V, typical

- 32 uA/MHz @ 1.8V, typical

### **Digital Peripherals:**

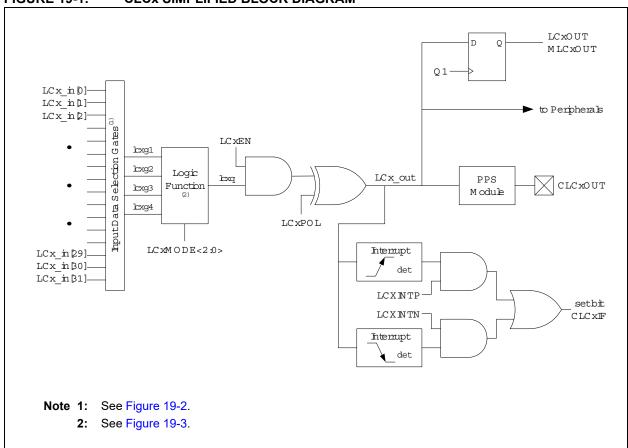

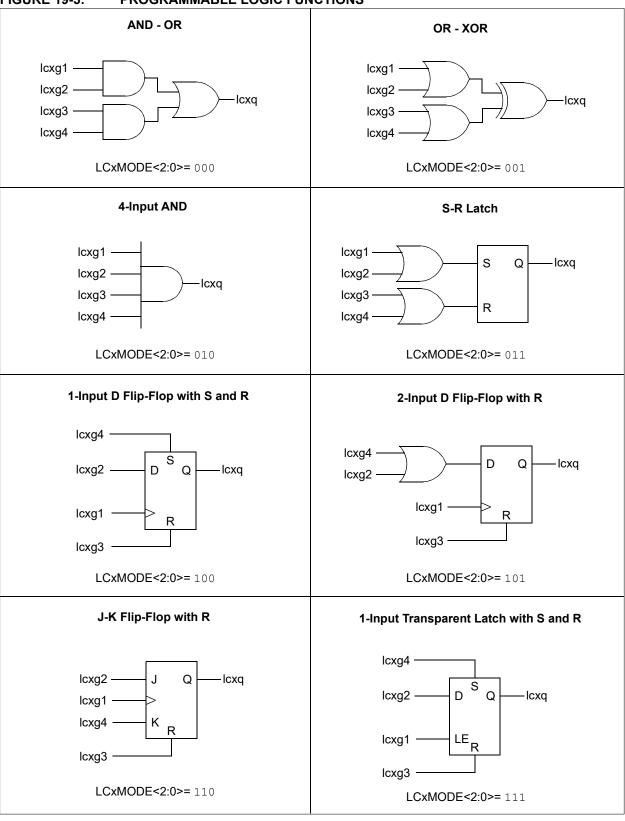

- · Configurable Logic Cell (CLC):

- Integrated combinational and sequential logic

- · Complementary Output Generator (COG):

- Rising/falling edge dead-band control/ blanking

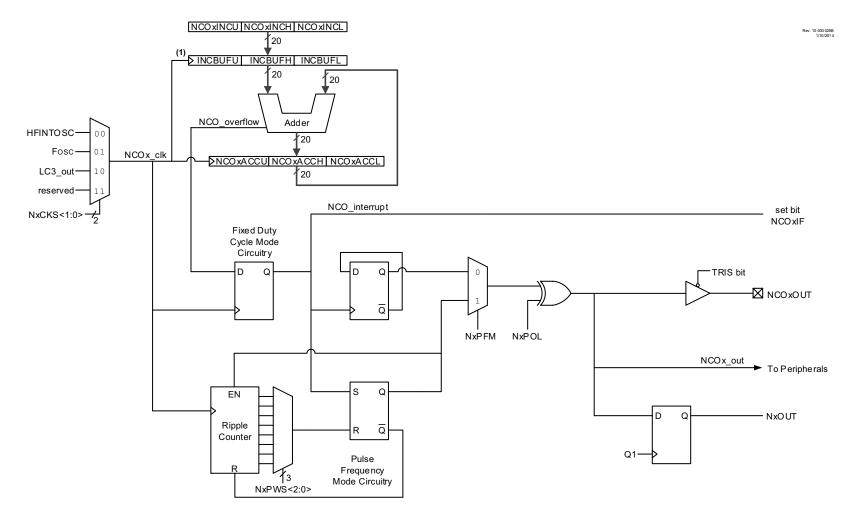

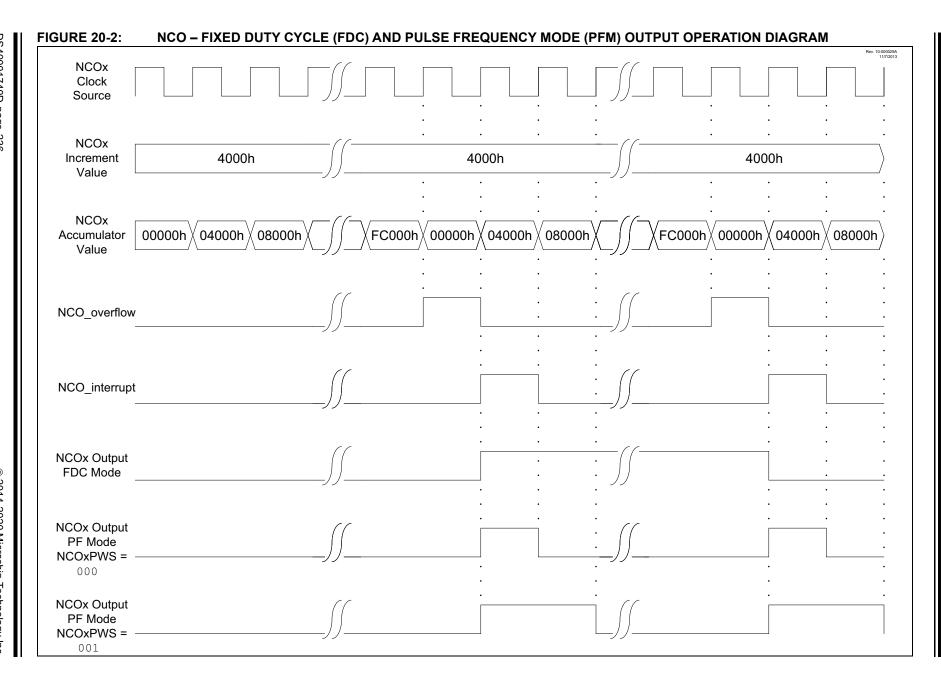

- Numerically Controlled Oscillator (NCO):

- Generates true linear frequency control and increased frequency resolution

- Input Clock: 0 Hz < FNCO < 32 MHz

- Resolution: FNCO/220

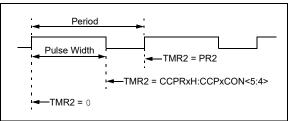

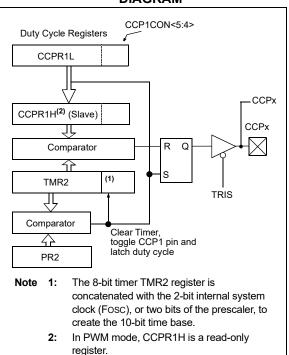

- Capture/Compare/PWM (CCP) module

- PWM: Two 10-Bit Pulse-Width Modulators

- · Serial Communications:

- SPI, I<sup>2</sup>C, RS-232, RS-485, LIN compatible

- Auto-Baud Detect, auto-wake-up on start

- Up to 35 I/O Pins and One Input Pin:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-Change with edge-select

- · Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

### **Intelligent Analog Peripherals:**

- · Operational Amplifiers:

- Two configurable rail-to-rail op amps

- Selectable internal and external channels

- 2 MHz gain bandwidth product

- · High-Speed Comparators:

- Up to two comparators

- 50 ns response time

- Rail-to-rail inputs

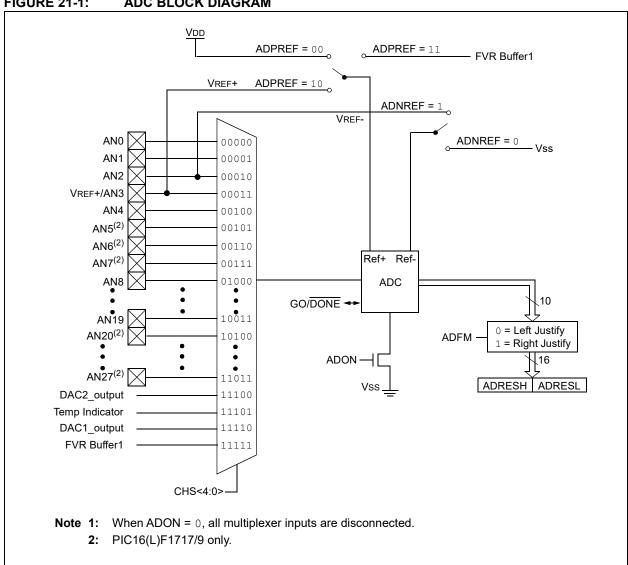

- 10-Bit Analog-to-Digital Converter (ADC):

- Up to 28 external channels

- Conversion available during Sleep

- Temperature indicator

- · Zero-Cross Detector (ZCD):

- Detect when AC signal on pin crosses ground

- 8-Bit Digital-to-Analog Converter (DAC):

- Output available externally

- Internal connections to comparators, op amps, Fixed Voltage Reference (FVR) and ADC

- · Internal Voltage Reference module

### **Clocking Structure:**

- 16 MHz Internal Oscillator Block:

- ±1% at calibration

- Selectable frequency range from 0 to 32 MHz

- 31 kHz Low-Power Internal Oscillator

- External Oscillator Block with:

- Three crystal/resonator modes up to 20 MHz

- Two external clock modes up to 20 MHz

- · Fail-Safe Clock Monitor

- · Two-Speed Oscillator Start-up

- Oscillator Start-up Timer (OST)

### **Programming/Debug Features:**

- · In-Circuit Debug Integrated On-Chip

- Emulation Header for Advanced Debug:

- Provides trace, background debug and up to 32 hardware break points

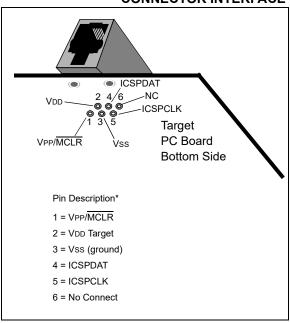

- In-Circuit Serial Programming™ (ICSP™) via Two Pins

| PIC16   | (L)F1           | 71X  | <b>Family</b> | Types |

|---------|-----------------|------|---------------|-------|

| 1 10 10 | \ <b>-</b> /' ' | 1 1/ | . alliliy     | IYPCS |

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM (bytes) | High Endurance Flash<br>(bytes) | I/Os <sup>(2)</sup> | 10-bit ADC (ch) | 5/8-bit DAC | High-Speed/<br>Comparators | Op Amp | Zero Cross | Timers<br>(8/16-bit) | CCP | PWM | 900 | EUSART | MSSP (I <sup>2</sup> C/SPI) | CLC | NCO | PPS | Debug <sup>(1)</sup> | XLP |

|---------------|------------------|---------------------------------|-------------------|---------------------------------|---------------------|-----------------|-------------|----------------------------|--------|------------|----------------------|-----|-----|-----|--------|-----------------------------|-----|-----|-----|----------------------|-----|

| PIC16(L)F1713 | (1)              | 4096                            | 512               | 128                             | 25                  | 17              | 1/1         | 2                          | 2      | 1          | 4/1                  | 2   | 2   | 1   | 1      | 1                           | 4   | 1   | Υ   | I/E                  | Υ   |

| PIC16(L)F1716 | (1)              | 8192                            | 1024              | 128                             | 25                  | 17              | 1/1         | 2                          | 2      | 1          | 4/1                  | 2   | 2   | 1   | 1      | 1                           | 4   | 1   | Υ   | I/E                  | Υ   |

| PIC16(L)F1717 | (2)              | 8192                            | 1024              | 128                             | 36                  | 28              | 1/1         | 2                          | 2      | 1          | 4/1                  | 2   | 2   | 1   | 1      | 1                           | 4   | 1   | Υ   | I/E                  | Υ   |

| PIC16(L)F1718 | (2)              | 16384                           | 2048              | 128                             | 25                  | 17              | 1/1         | 2                          | 2      | 1          | 4/1                  | 2   | 2   | 1   | 1      | 1                           | 4   | 1   | Υ   | I/E                  | Υ   |

| PIC16(L)F1719 | (2)              | 16384                           | 2048              | 128                             | 36                  | 28              | 1/1         | 2                          | 2      | 1          | 4/1                  | 2   | 2   | 1   | 1      | 1                           | 4   | 1   | Υ   | I/E                  | Υ   |

Note 1: Debugging Methods: (I) – Integrated on Chip; (H) – using Debug Header; E – using Emulation Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS40001726 PIC16(L)F1713/6 Data Sheet, 28-Pin Flash, 8-bit Microcontrollers.

2: DS40001740 PIC16(L)F1717/8/9 Data Sheet, 28/40-Pin Flash, 8-bit Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit <a href="http://www.microchip.com/packaging">http://www.microchip.com/packaging</a> or contact your local sales office.

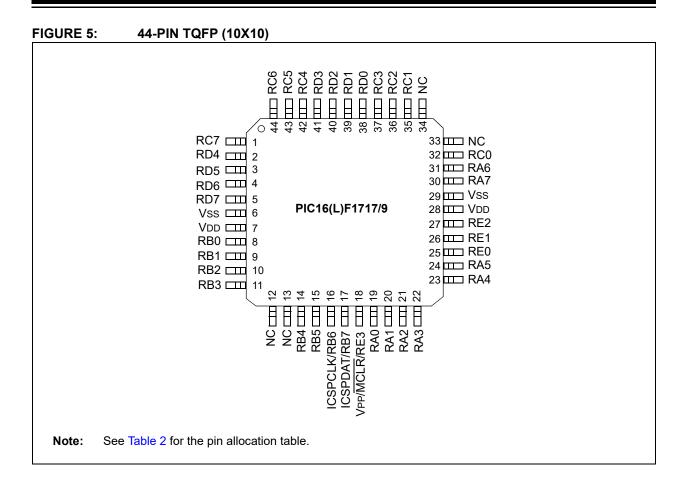

### **Pin Diagrams**

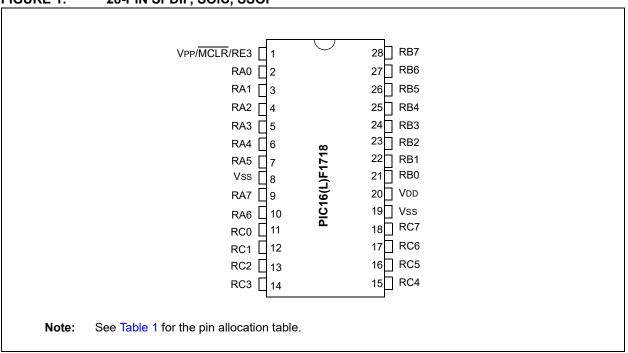

FIGURE 1: 28-PIN SPDIP, SOIC, SSOP

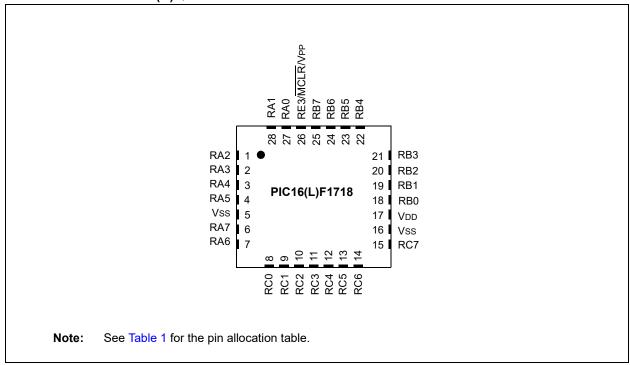

FIGURE 2: 28-PIN (U)QFN

DS40001740D-page 4

TABLE 1: 28-PIN ALLOCATION TABLE (PIC16(L)F1718)

| 1/0(2) | SPDIP,SOIC,<br>SSOP | QFN, UQFN | ADC  | Reference          | Comparator       | Ор Атр  | DAC                  | Zero Cross | Timers                          | CCP                 | NCO | PWM | 900   |                  | MSSP                   | EUSART | CLC                   | Interrupt                 | Pull-up | Basic          |

|--------|---------------------|-----------|------|--------------------|------------------|---------|----------------------|------------|---------------------------------|---------------------|-----|-----|-------|------------------|------------------------|--------|-----------------------|---------------------------|---------|----------------|

| RA0    | 2                   | 27        | AN0  |                    | C1IN0-<br>C2IN0- |         |                      |            |                                 |                     |     |     |       |                  |                        |        | CLCINO <sup>(1)</sup> | IOC                       | Υ       |                |

| RA1    | 3                   | 28        | AN1  |                    | C1IN1-<br>C2IN1- | OPA1OUT |                      |            |                                 |                     |     |     |       |                  |                        |        | CLCIN1 <sup>(1)</sup> | IOC                       | Υ       |                |

| RA2    | 4                   | 1         | AN2  | V <sub>REF</sub> - | C1IN0+<br>C2IN0+ |         | DAC1OUT1             |            |                                 |                     |     |     |       |                  |                        |        |                       | IOC                       | Υ       |                |

| RA3    | 5                   | 2         | AN3  | V <sub>REF</sub> + | C1IN1+           |         |                      |            |                                 |                     |     |     |       |                  |                        |        |                       | IOC                       | Υ       |                |

| RA4    | 6                   | 3         |      |                    |                  | OPA1IN+ |                      |            | T0CKI <sup>(1)</sup>            |                     |     |     |       |                  |                        |        |                       | IOC                       | Υ       |                |

| RA5    | 7                   | 4         | AN4  |                    |                  | OPA1IN- | DAC2OUT1             |            |                                 |                     |     |     |       |                  | nSS <sup>(1)</sup>     |        | 1-1-1-1               | IOC                       | Υ       |                |

| RA6    | 10                  | 7         |      |                    |                  |         |                      |            |                                 |                     |     |     |       |                  |                        |        |                       | IOC                       | Υ       | OSC2<br>CLKOUT |

| RA7    | 9                   | 6         |      |                    |                  |         |                      |            |                                 |                     |     |     |       |                  |                        |        |                       | IOC                       | Υ       | OSC1<br>CLKIN  |

| RB0    | 21                  | 18        | AN12 |                    | C2IN1+           |         |                      | ZCD        |                                 |                     |     |     | COG1I | N <sup>(1)</sup> |                        |        |                       | INT <sup>(1)</sup><br>IOC | Y       |                |

| RB1    | 22                  | 19        | AN10 |                    | C1IN3-<br>C2IN3- | OPA2OUT |                      |            |                                 |                     |     |     |       |                  |                        |        |                       | IOC                       | Υ       |                |

| RB2    | 23                  | 20        | AN8  |                    |                  | OPA2IN- |                      |            |                                 |                     |     |     |       |                  |                        |        |                       | IOC                       | Υ       |                |

| RB3    | 24                  | 21        | AN9  |                    | C1IN2-<br>C2IN2- | OPA2IN+ |                      |            |                                 |                     |     |     |       |                  |                        |        |                       | IOC                       | Υ       |                |

| RB4    | 25                  | 22        | AN11 |                    |                  |         |                      |            | 1.1.1                           |                     |     |     |       |                  | 14:41                  |        | -1-1-1-1              | IOC                       | Υ       |                |

| RB5    | 26                  | 23        | AN13 |                    |                  |         |                      |            | T1G <sup>(1)</sup>              |                     |     |     |       |                  |                        |        |                       | IOC                       | Υ       |                |

| RB6    | 27                  | 24        |      |                    |                  |         |                      |            |                                 |                     |     |     |       |                  |                        |        | CLCIN2 <sup>(1)</sup> | IOC                       | Υ       | ICSPCLK        |

| RB7    | 28                  | 25        |      |                    |                  |         | DAC1OUT2<br>DAC2OUT2 |            |                                 |                     |     |     |       |                  |                        |        | CLCIN3 <sup>(1)</sup> | IOC                       | Υ       | ICSPDAT        |

| RC0    | 11                  | 8         |      |                    |                  |         |                      |            | T1CKI <sup>(1)</sup> .<br>SOSCO |                     |     |     |       |                  |                        |        |                       | loc                       | Υ       |                |

| RC1    | 12                  | 9         |      |                    |                  |         |                      |            | SOSCI                           | CCP2 <sup>(1)</sup> |     |     |       |                  |                        |        |                       | · IOC ·                   | Υ       |                |

| RC2    | 13                  | 10        | AN14 |                    |                  |         |                      |            |                                 | CCP1 <sup>(1)</sup> |     |     |       |                  |                        |        |                       | · IOC ·                   | Υ       |                |

| RC3    | 14                  | 11        | AN15 |                    |                  |         |                      |            |                                 |                     |     |     |       |                  | SCL/SCK <sup>(1)</sup> |        |                       | ioc.                      | Υ       |                |

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

<sup>2:</sup> All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

<sup>3:</sup> These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

<sup>4:</sup> Alternate outputs are excluded from solid shaded areas.

<sup>5:</sup> Alternate inputs are excluded from dot shaded areas.

TABLE 1: 28-PIN ALLOCATION TABLE (PIC16(L)F1718) (CONTINUED)

| 1/0(2)             | SPDIP,SOIC,<br>SSOP | QFN, UQFN | ADC  | Reference | omoração. | Comparator | Ор Атр | DAC | Zero Cross |     | Timers |       | CCP  |      | NCO     | MANG    |         |       | 900    |       |       | MSSP                                         |                                        | TOVOL             |              |         | 2       |         | Interrupt | Pull-up | Basic                   |

|--------------------|---------------------|-----------|------|-----------|-----------|------------|--------|-----|------------|-----|--------|-------|------|------|---------|---------|---------|-------|--------|-------|-------|----------------------------------------------|----------------------------------------|-------------------|--------------|---------|---------|---------|-----------|---------|-------------------------|

| RC4                | 15                  | 12        | AN16 |           |           |            |        |     |            |     |        |       |      |      |         |         |         |       |        |       |       | SD<br>SD                                     | )I <sup>(1)</sup><br>)A <sup>(1)</sup> |                   |              |         |         |         | ioc.      | Υ       |                         |

| RC5                | 16                  | 13        | AN17 |           |           |            |        |     |            |     |        |       |      |      |         |         |         |       |        |       |       |                                              |                                        |                   |              |         |         |         | [ loc.    | Υ       |                         |

| RC6                | 17                  | 14        | AN18 |           |           |            |        |     |            |     |        |       |      |      |         |         |         |       |        |       |       |                                              |                                        | Cł                | <b>(</b> 3)  |         |         |         | : IOC     | Υ       |                         |

| RC7                | 18                  | 15        | AN19 |           |           |            |        |     |            |     |        |       |      |      |         |         |         |       |        |       |       |                                              |                                        | R)                | <b>(</b> (3) |         |         |         | · ЮC·     | Υ       |                         |

| RE3                | 1                   | 26        |      |           |           |            |        |     |            |     |        |       |      |      |         |         |         |       |        |       |       |                                              |                                        |                   |              |         |         |         | IOC       | Υ       | MCLR<br>V <sub>PP</sub> |

| V <sub>DD</sub>    | 20                  | 17        |      |           |           |            |        |     |            |     |        |       |      |      |         |         |         |       |        |       |       |                                              |                                        |                   |              |         |         |         |           |         | $V_{DD}$                |

| Vss                | 8                   | 5         |      |           |           |            |        |     |            |     |        |       |      |      |         |         |         |       |        |       |       |                                              |                                        |                   |              |         |         |         |           |         | V <sub>SS</sub>         |

| V SS               | 19                  | 16        |      |           |           |            |        |     |            |     |        |       |      |      |         |         |         |       |        |       |       |                                              |                                        |                   |              |         |         |         |           |         |                         |

| OUT <sup>(4)</sup> |                     |           |      |           | C10UT     | С2ОUT      |        |     |            |     |        |       | CCP1 | CCP2 | NC010UT | PWM3OUT | PWM40UT | COG1A | COG1B  | C0G1C | C0G1D | SDA <sup>(3)</sup><br>SCK/SCL <sup>(3)</sup> | SDO                                    | TX/CK             | DT(3)        | CLC40UT | CLC3OUT | CLC2OUT |           |         |                         |

| IN <sup>(5)</sup>  |                     |           |      |           |           |            |        |     |            | T1G | T1CKI  | T0CKI | CCP1 | CCP2 |         |         |         |       | COG1IN |       |       | SDI<br>SCK/SCL <sup>(3)</sup>                | SS                                     | RX <sup>(3)</sup> | S            | CLCINO  | CLCIN1  | CLCIN2  | INT       |         |                         |

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

<sup>2:</sup> All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

<sup>3:</sup> These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

<sup>4:</sup> Alternate outputs are excluded from solid shaded areas.

<sup>5:</sup> Alternate inputs are excluded from dot shaded areas.

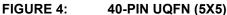

FIGURE 3: **40-PIN PDIP** 40 RB7/ICSPDAT VPP/MCLR/RE3 ☐1 39 RB6/ICSPCLK RA0 ∏2 38 RB5 RA1 ∏3 37 RB4 RA2 **□**4 36 RB3 RA3 ∏5 35 RB2 RA4 **□**6 34 RB1 RA5 ∏7 33 RB0 RE0 **□**8 32 VDD RE1 **9** RE2 10 31 Vss 30 RD7 VDD **□**11 29 RD6 Vss ∏12 RA7 🛮 13 28 RD5 27 RD4 RA6 □14 26 RC7 RC0 ∏15 25 RC6 RC1 16 24 RC5 RC2 17 23 RC4 RC3 ∏18 22 RD3 RD0 🛮 19 21 RD2 RD1 20

See Table 2 for the pin allocation table.

Note:

DS40001740D-page 8

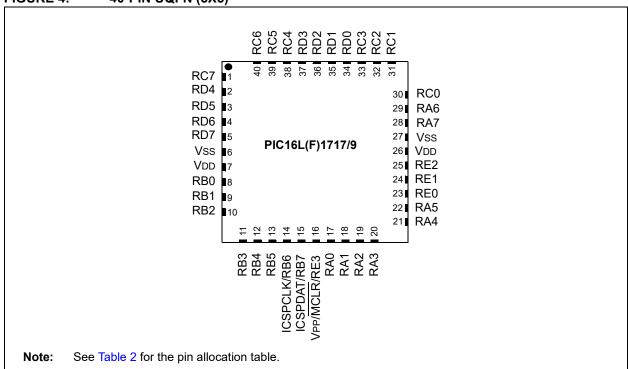

TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC16(L)F1717/9)

| I/O <sup>(2)</sup> | PDIP | TQFP | NGFN | ADC  | Reference          | Comparator       | Ор Атр  | DAC                  | Zero Cross |     | Timers |       | CCP  |     | NCO | PWM | 900                   | MSSP             |                  | EUSART | CLC                     | Interrupt          | Pullup | Basic          |

|--------------------|------|------|------|------|--------------------|------------------|---------|----------------------|------------|-----|--------|-------|------|-----|-----|-----|-----------------------|------------------|------------------|--------|-------------------------|--------------------|--------|----------------|

| RA0                | 2    | 19   | 17   | AN0  |                    | C1IN0-<br>C2IN0- |         |                      |            |     |        |       |      |     |     |     |                       |                  |                  |        | CLCINO <sup>(1)</sup>   | IOC                | Υ      |                |

| RA1                | 3    | 20   | 18   | AN1  |                    | C1IN1-<br>C2IN1- | OPA1OUT |                      |            |     |        |       |      |     |     |     |                       |                  |                  |        | CLCIN1 <sup>(1)</sup>   | ioc                | Υ      |                |

| RA2                | 4    | 21   | 19   | AN2  | V <sub>REF</sub> - | C1IN0+<br>C2IN0+ |         | DAC1OUT1             |            |     |        |       |      |     |     |     |                       |                  |                  |        |                         | OC                 | Υ      |                |

| RA3                | 5    | 22   | 20   | AN3  | V <sub>REF</sub> + | C1IN1+           |         |                      |            | ::: |        |       |      |     |     |     |                       |                  |                  |        | .:-:-:-                 | : IOC              | Υ      |                |

| RA4                | 6    | 23   | 21   |      |                    |                  | OPA1IN+ |                      |            | ΪŤΟ | CKI    | (1)   |      |     |     |     |                       |                  |                  |        | 1:11:1                  | OC                 | Υ      |                |

| RA5                | 7    | 24   | 22   | AN4  |                    |                  | OPA1IN- | DAC2OUT1             |            |     |        |       |      |     |     |     |                       | nSS <sup>(</sup> | 1)               |        |                         | · IOC              | Υ      |                |

| RA6                | 14   | 31   | 29   |      |                    |                  |         |                      |            |     |        |       |      |     |     |     |                       |                  |                  |        |                         | IOC                | Υ      | OSC2<br>CLKOUT |

| RA7                | 13   | 30   | 28   |      |                    |                  |         |                      |            |     |        |       |      |     |     |     |                       |                  |                  |        |                         | IOC                | Υ      | OSC1<br>CLKIN  |

| RB0                | 33   | 8    | 8    | AN12 |                    | C2IN1+           |         |                      | ZCD        |     |        |       |      |     |     |     | COG1IN <sup>(1)</sup> |                  |                  |        |                         | INT <sup>(1)</sup> | Υ      |                |

| RB1                | 34   | 9    | 9    | AN10 |                    | C1IN3-<br>C2IN3- | OPA2OUT |                      |            |     |        |       |      |     |     |     |                       |                  |                  |        |                         | ЮС                 | Υ      |                |

| RB2                | 35   | 10   | 10   | AN8  |                    |                  | OPA2IN- |                      |            |     |        |       |      |     |     |     |                       |                  |                  |        |                         | IOC                | Υ      |                |

| RB3                | 36   | 11   | 11   | AN9  |                    | C1IN2-<br>C2IN2- | OPA2IN+ |                      |            |     |        |       |      |     |     |     |                       |                  |                  |        |                         | ЮС                 | Υ      |                |

| RB4                | 37   | 14   | 12   | AN11 |                    |                  |         |                      |            |     |        |       |      |     |     |     |                       |                  |                  |        |                         | IOC                | Υ      |                |

| RB5                | 38   | 15   | 13   | AN13 |                    |                  |         |                      |            |     | T1G    | (1)   |      |     |     |     |                       |                  |                  |        |                         | IOC                | Υ      |                |

| RB6                | 39   | 16   | 14   |      |                    |                  |         |                      |            |     |        |       |      |     |     |     |                       |                  |                  |        | ∴ CLCIN2 <sup>(1)</sup> | IOC                | Υ      | ICSPCLK        |

| RB7                | 40   | 17   | 15   |      |                    |                  |         | DAC1OUT2<br>DAC2OUT2 |            |     |        |       |      |     |     |     |                       |                  |                  |        | ÇĽCIN3 <sup>(1)</sup>   | IOC                | Υ      | ICSPDAT        |

| RC0                | 15   | 32   | 30   |      |                    |                  |         |                      |            | SC  | 1CK    | o :   |      |     |     |     |                       |                  |                  |        |                         | loc                | Υ      |                |

| RC1                | 16   | 35   | 31   |      |                    |                  |         |                      |            | S   | os¢    | ) : K | CCP2 | (1) |     |     |                       |                  |                  |        | 1-1-1-1-                | : IQ¢              | Υ      |                |

| RC2                | 17   | 36   |      | AN14 |                    |                  |         |                      |            |     |        |       | CCP1 | (1) |     |     |                       |                  |                  |        |                         | IOC                | Υ      |                |

| RC3                | 18   | 37   | 33   | AN15 |                    |                  |         |                      |            |     |        |       |      |     |     |     |                       | SCL/SC           | < <sup>(1)</sup> |        |                         | IOC                | Υ      |                |

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

<sup>2:</sup> All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

<sup>3:</sup> These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

<sup>4:</sup> Alternate outputs are excluded from solid shaded areas.

<sup>5:</sup> Alternate inputs are excluded from dot shaded areas.

DS40001740D-page 9

TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC16(L)F1717/9) (CONTINUED)

| 1/0(2)             | PDIP | TQFP | UQFN | ADC  | Reference |       | Comparator | Ор Атр | DAC           | Zero Cross |     | Timers   |         | 900  | 5    | NCO     | DWM            |         |       | 500    |       |       | O                  | 5                                    | i i    | EUSAKI           |         |         | }       |         | Interrupt | Pullup | Basic                   |

|--------------------|------|------|------|------|-----------|-------|------------|--------|---------------|------------|-----|----------|---------|------|------|---------|----------------|---------|-------|--------|-------|-------|--------------------|--------------------------------------|--------|------------------|---------|---------|---------|---------|-----------|--------|-------------------------|

| RC4                | 23   | 42   | 38   | AN16 |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       | SD<br>SD           | I <sup>(1)</sup><br>A <sup>(1)</sup> |        |                  |         |         |         | . )(    | OC:       | Υ      |                         |

| RC5                | 24   | 43   | 39   | AN17 |           |       |            |        |               |            |     |          | • : • : |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         | . 10    |           | Υ      |                         |

| RC6                | 25   | 44   | 40   | AN18 |           |       |            |        |               |            |     |          | • • • • |      |      |         |                |         |       |        |       |       |                    |                                      | : c    | K <sup>(3)</sup> |         |         |         | · i (   | OC.       | Υ      |                         |

| RC7                | 26   | 1    | 1    | AN19 |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       |                    |                                      | ; R    | X <sup>(3)</sup> |         |         | :::::   | 10      |           | Υ      |                         |

| RD0                | 19   | 38   | 34   | AN20 |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         |         |           | Υ      |                         |

| RD1                | 20   | 39   | 35   | AN21 |           |       |            |        |               |            |     |          | :::     |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  | :::     | : : :   |         |         |           | Υ      |                         |

| RD2                | 21   | 40   | 36   | AN22 |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         |         |           | Υ      |                         |

| RD3                | 22   | 41   | 37   | AN23 |           |       |            |        |               |            |     | $\cdots$ | • : • : |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         | • : • : |         |         |           | Υ      |                         |

| RD4                | 27   | 2    | 2    | AN24 |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         |         |           | Υ      |                         |

| RD5                | 28   | 3    | 3    | AN25 |           |       |            |        |               |            |     | ::::     | :::     |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  | :::     |         |         |         |           | Υ      |                         |

| RD6                | 29   | 4    | 4    | AN26 |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         | :::     |         |         |           | Υ      |                         |

| RD7                | 30   | 5    | 5    | AN27 |           |       |            |        |               |            |     |          | • : :   |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  | :::     | • • • • |         |         |           | Υ      |                         |

| RE0                | 8    | 25   | 23   | AN5  |           |       |            |        |               |            |     | ::::     |         |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         | :::     |           | Υ      |                         |

| RE1                | 9    | 26   | 24   | AN6  |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         |         |           | Υ      |                         |

| RE2                | 10   | 27   | 25   | AN7  |           |       |            |        |               |            |     | ::::     | : · : · |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         |         | -:-:-     | Υ      |                         |

| RE3                | 1    | 18   | 16   |      |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         | 10      | ос        | Υ      | MCLR<br>V <sub>PP</sub> |

| \/                 | 11   | 7    | 7    |      |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         |         |           |        | $V_{DD}$                |

| V <sub>DD</sub>    | 32   | 28   | 26   |      |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         |         |           |        |                         |

| V <sub>SS</sub>    | 12   | 6    | 6    |      |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         |         |           |        | $V_{SS}$                |

| v ss               | 31   | 29   | 27   |      |           |       |            |        |               |            |     |          |         |      |      |         |                |         |       |        |       |       |                    |                                      |        |                  |         |         |         |         |           |        |                         |

| OUT <sup>(4)</sup> |      |      |      |      |           | C10UT | CZOUT      |        |               |            |     |          |         | CCP1 | CCP2 | NC010UT | <b>PWM30UT</b> | PWM40UT | COG1A | COG1B  | C0G1C | C0G1D | SDA <sup>(3)</sup> |                                      | TX/CK  | DT (3)           | CLC40UT | CLC3OUT | CLC2OUT | CLCTOUL |           |        |                         |

| 1N <sup>(5)</sup>  |      |      |      |      |           |       |            |        | a the pariphe |            | T1G |          | T0CKI   | CCP1 | CCP2 |         |                |         |       | COG1IN |       |       | SDI                |                                      | RX (3) | S                | CLCINO  | CLCIN1  | CLCIN2  | CLCIN3  | L<br>Z    |        |                         |

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

<sup>2:</sup> All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

<sup>3:</sup> These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

<sup>4:</sup> Alternate outputs are excluded from solid shaded areas.

<sup>5:</sup> Alternate inputs are excluded from dot shaded areas.

### **Table of Contents**

| 1.0  | Device Overview                                                           | 12  |

|------|---------------------------------------------------------------------------|-----|

| 2.0  | Enhanced Mid-Range CPU                                                    | 22  |

| 3.0  | Memory Organization                                                       | 24  |

| 4.0  | Device Configuration                                                      | 55  |

| 5.0  | Resets                                                                    | 60  |

| 6.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          | 68  |

| 7.0  | Interrupts                                                                | 86  |

| 8.0  | Power-Down Mode (Sleep)                                                   | 98  |

| 9.0  | Watchdog Timer (WDT)                                                      | 102 |

| 10.0 | Flash Program Memory Control                                              | 106 |

| 11.0 | I/O Ports                                                                 | 122 |

| 12.0 | Peripheral Pin Select (PPS) Module                                        | 150 |

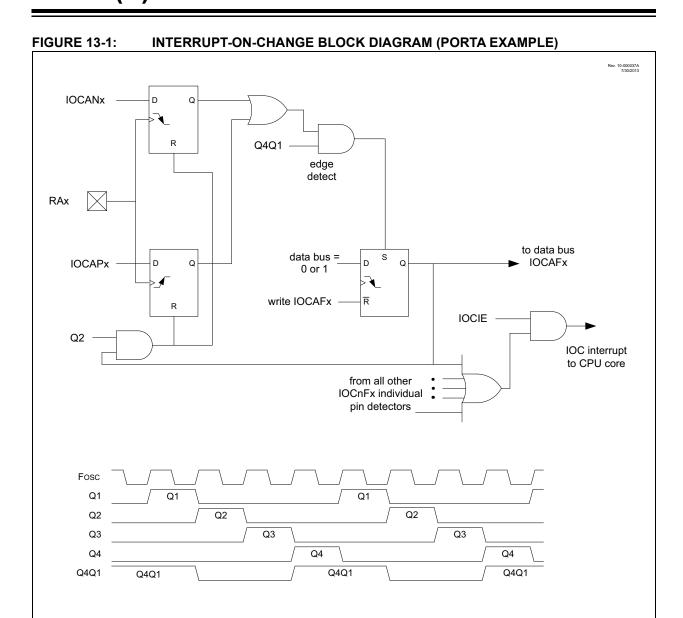

| 13.0 | Interrupt-on-Change                                                       | 156 |

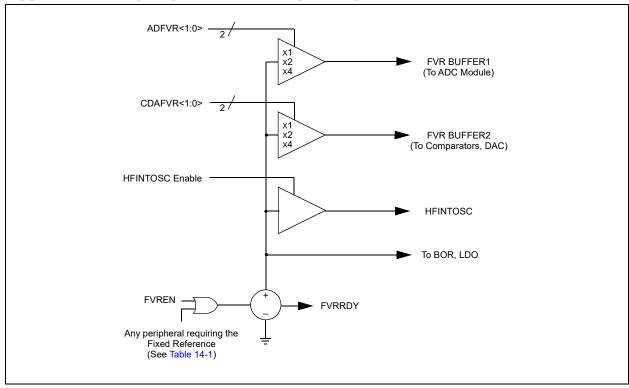

| 14.0 | Fixed Voltage Reference (FVR)                                             | 163 |

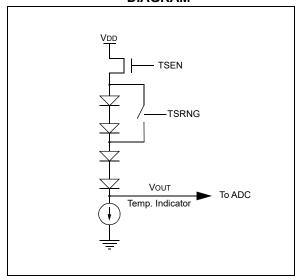

| 15.0 | Temperature Indicator Module                                              | 166 |

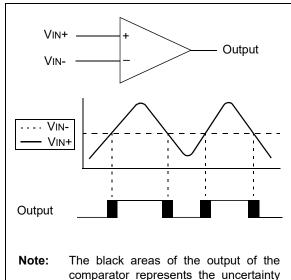

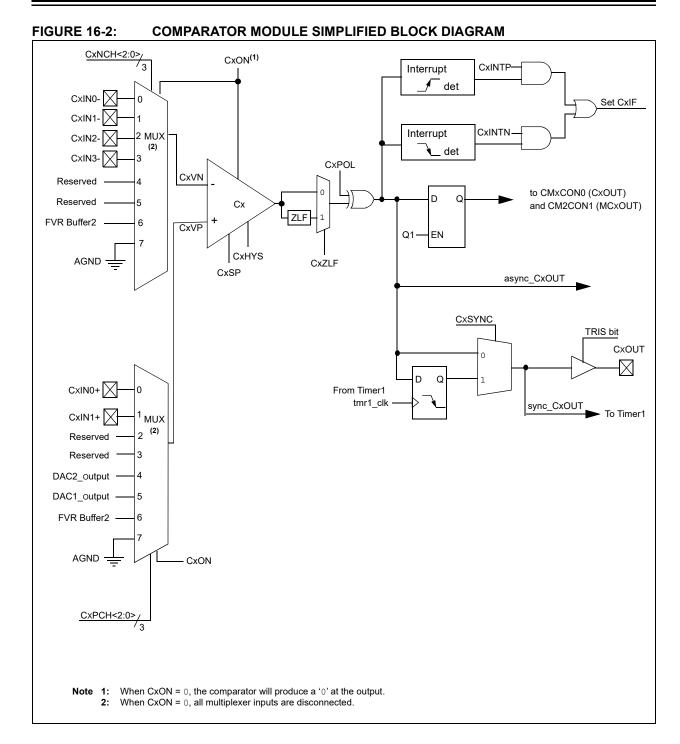

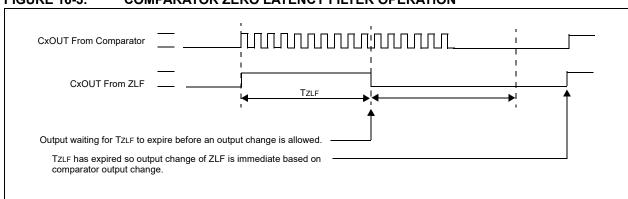

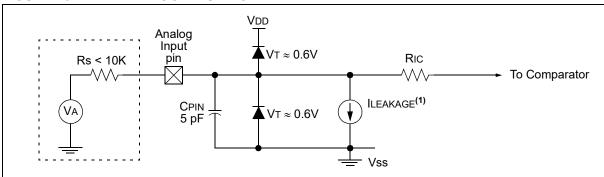

| 16.0 | Comparator Module                                                         | 168 |

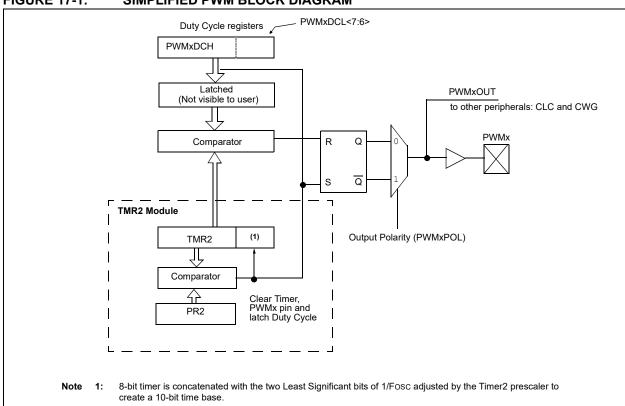

| 17.0 | Pulse Width Modulation (PWM)                                              | 177 |

|      | Complementary Output Generator (COG) Module                               |     |

| 19.0 | Configurable Logic Cell (CLC)                                             | 218 |

|      | Numerically Controlled Oscillator (NCO) Module                            |     |

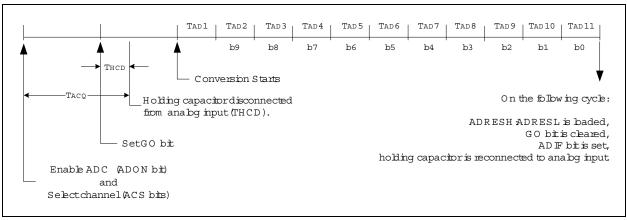

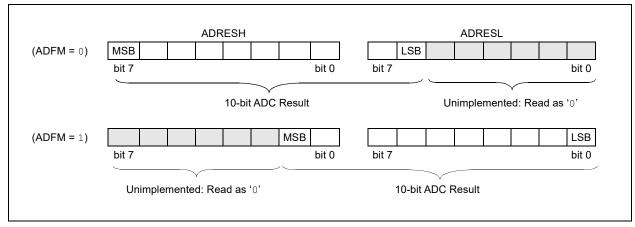

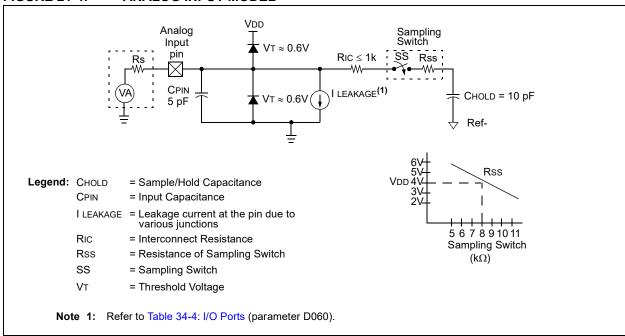

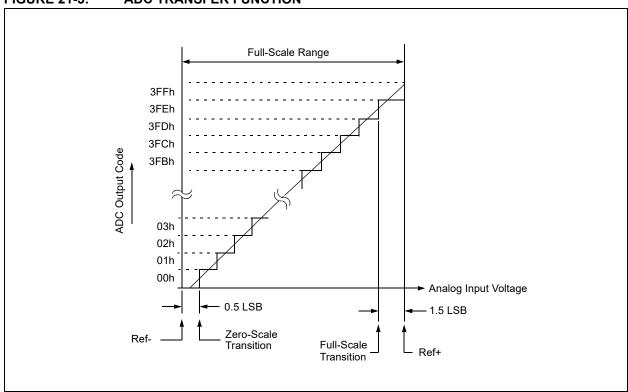

|      | Analog-to-Digital Converter (ADC) Module                                  |     |

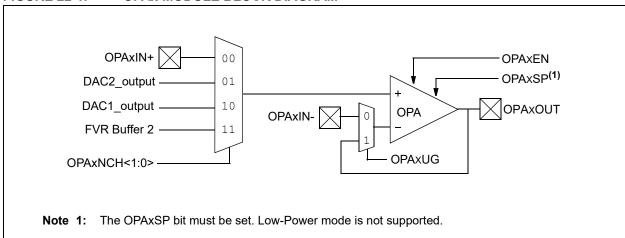

| 22.0 | Operational Amplifier (OPA) Modules                                       | 255 |

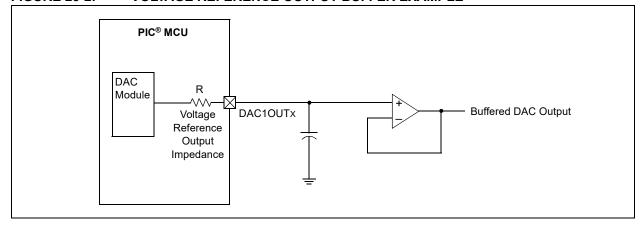

| 23.0 | 8-Bit Digital-to-Analog Converter (DAC1) Module                           | 258 |

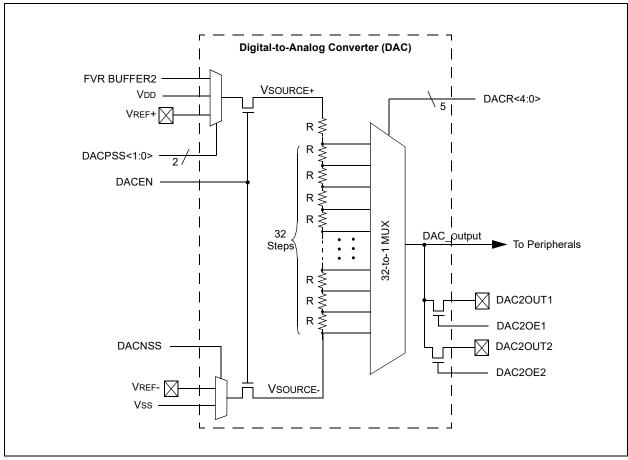

| 24.0 | 5-Bit Digital-to-Analog Converter (DAC2) Module                           | 261 |

| 25.0 | Zero-Cross Detection (ZCD) Module                                         | 264 |

| 26.0 | Timer0 Module                                                             | 271 |

|      | Timer1 Module with Gate Control                                           |     |

| 28.0 | Timer2/4/6 Module                                                         | 285 |

| 29.0 | Capture/Compare/PWM Modules                                               | 290 |

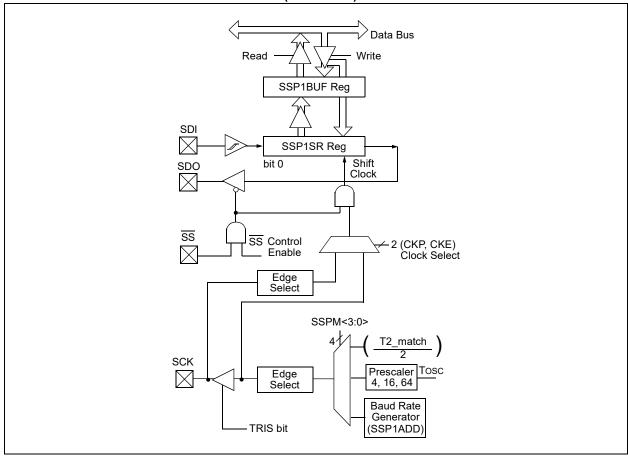

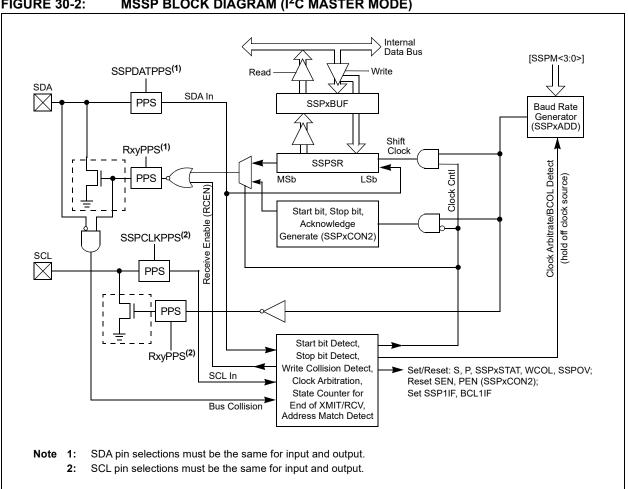

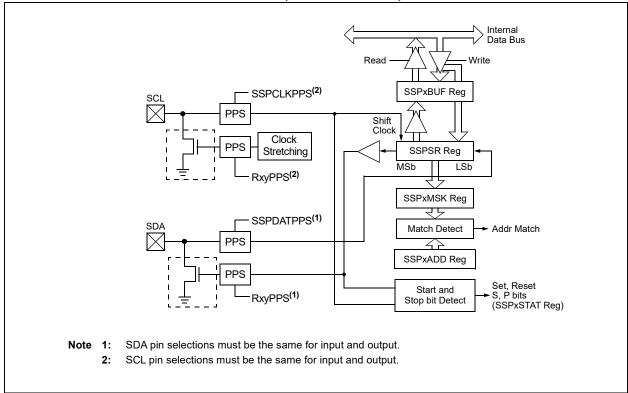

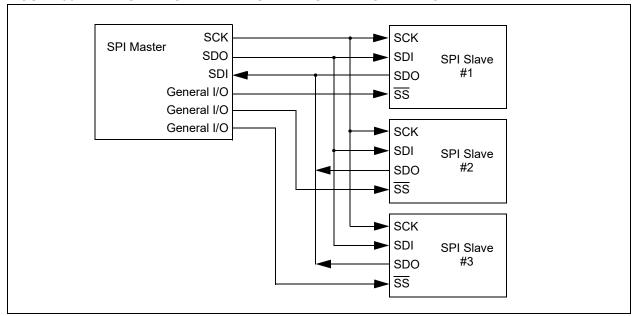

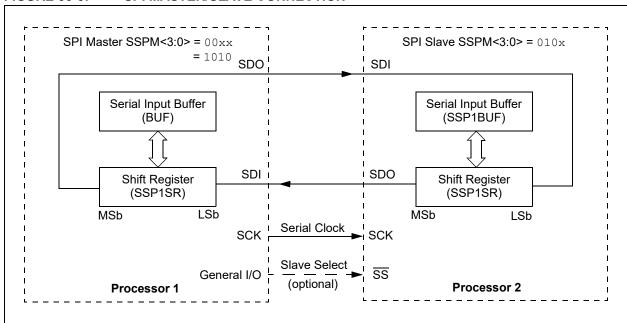

| 30.0 | Master Synchronous Serial Port (MSSP) Module                              | 298 |

| 31.0 | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 354 |

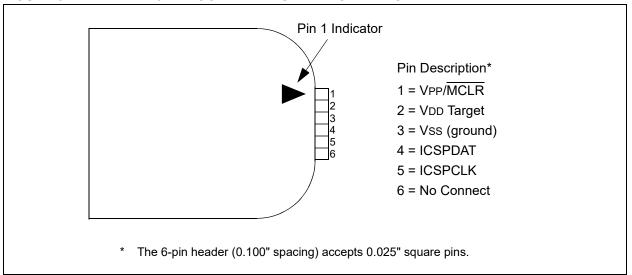

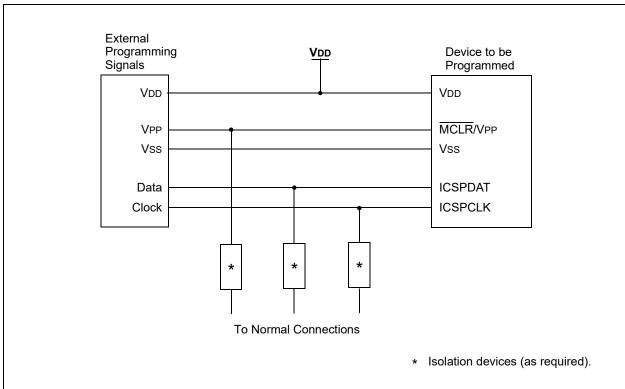

| 32.0 | In-Circuit Serial Programming (ICSP™)                                     | 384 |

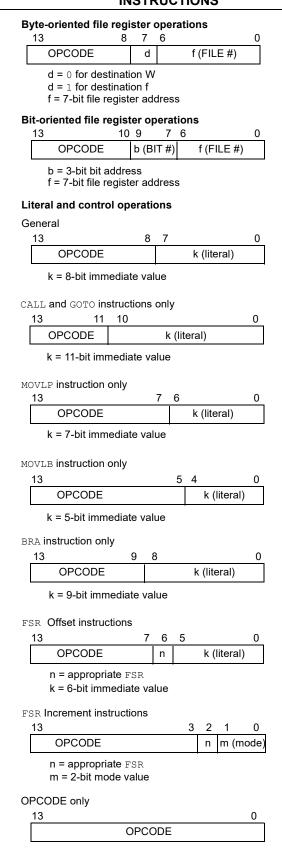

| 33.0 | Instruction Set Summary                                                   | 386 |

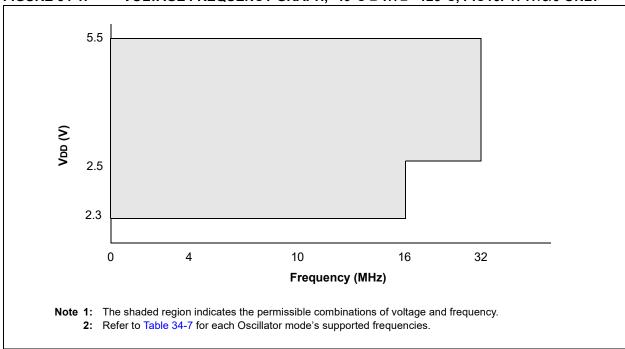

| 34.0 | Electrical Specifications                                                 | 400 |

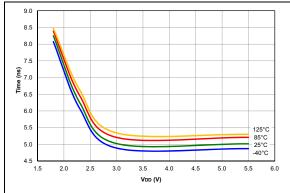

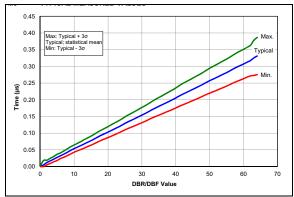

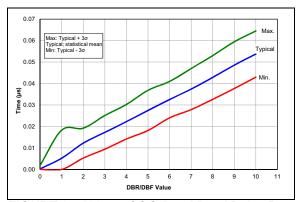

|      | DC and AC Characteristics Graphs and Charts                               |     |

| 36.0 | Development Support                                                       | 456 |

|      | Packaging Information                                                     |     |

|      | andix A: Data Sheet Revision History                                      | 191 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

### 1.0 DEVICE OVERVIEW

The PIC16(L)F1717/8/9 devices are described within this data sheet. They are available in the following package configurations:

- 28-pin SPDIP, SSOP, SOIC, QFN and UQFN

- 40-pin PDIP and UQFN

- 44-pin TQFP

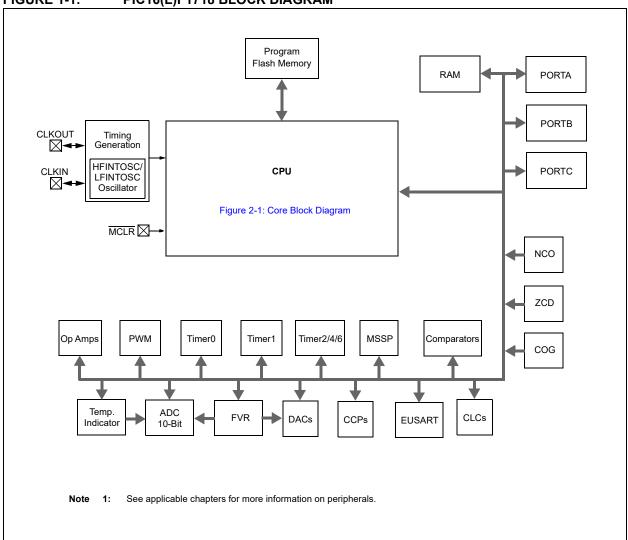

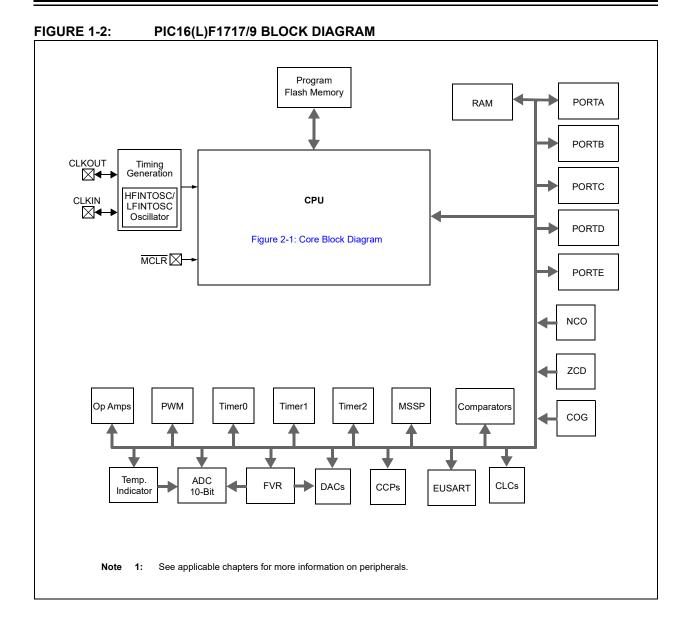

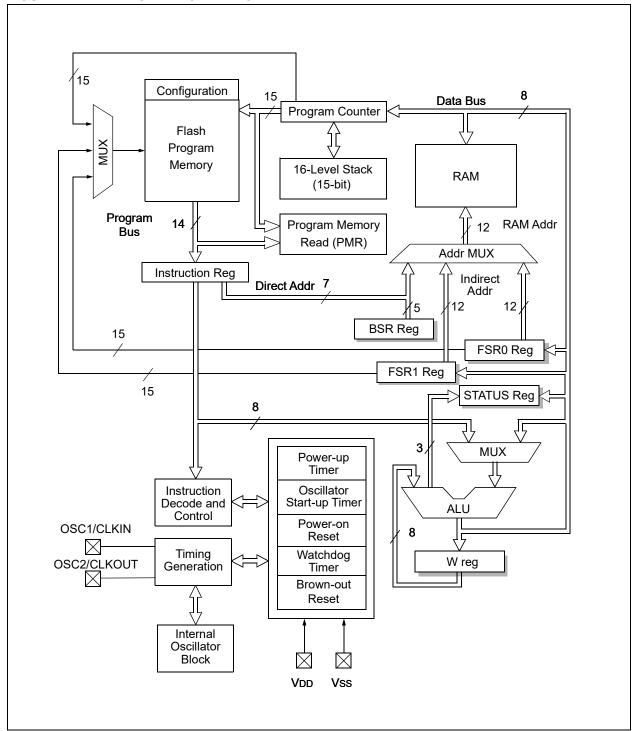

Figure 1-1 and Figure 1-2 show block diagrams of the PIC16(L)F1717/8/9 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| SUIVIIV                                            | IAINI          |               |               |               |

|----------------------------------------------------|----------------|---------------|---------------|---------------|

| Peripheral                                         |                | PIC16(L)F1717 | PIC16(L)F1718 | PIC16(L)F1719 |

| Analog-to-Digital Conver                           | ter (ADC)      | •             | •             | •             |

| Fixed Voltage Reference                            | (FVR)          | •             | •             | •             |

| Zero-Cross Detection (Z                            | CD)            | •             | •             | •             |

| Temperature Indicator                              |                | •             | •             | •             |

| Complementary Output                               | Generator (C   | OG)           |               |               |

|                                                    | COG            | •             | •             | •             |

| Numerically Controlled C                           | Oscillator (NC | O)            |               |               |

|                                                    | NCO            | •             | •             | •             |

| Digital-to-Analog Conver                           | ter (DAC)      |               |               |               |

|                                                    | DAC1           | •             | •             | •             |

|                                                    | DAC2           | •             | •             | •             |

| Capture/Compare/PWM                                | (CCP/ECCP      | ) Mod         | ules          |               |

|                                                    | CCP1           | •             | •             | •             |

|                                                    | CCP2           | •             | •             | •             |

| Comparators                                        |                | I             |               |               |

|                                                    | C1             | •             | •             | •             |

|                                                    | C2             | •             | •             | •             |

| Configurable Logic Cell                            | (CLC)          | ı             |               |               |

|                                                    | CLC1           | •             | •             | •             |

|                                                    | CLC2           | •             | •             | •             |

|                                                    | CLC3           | •             | •             | •             |

|                                                    | CLC4           | •             | •             | •             |

| Enhanced Universal Syr<br>Receiver/Transmitter (El |                | ynchr         | onous         | 5             |

|                                                    | EUSART         | •             | •             | •             |

| Master Synchronous Se                              | rial Ports     | •             |               |               |

|                                                    | MSSP           | •             | •             | •             |

| Op Amp                                             |                |               |               |               |

|                                                    | Op Amp 1       | •             | •             | •             |

|                                                    | Op Amp 2       | •             | •             | •             |

| Pulse-Width Modulator (                            | PWM)           |               |               |               |

|                                                    | PWM3           | •             | •             | •             |

|                                                    | PWM4           | •             | •             | •             |

| Timers                                             | •              |               |               |               |

|                                                    | Timer0         | •             | •             | •             |

|                                                    | Timer1         | •             | •             | •             |

|                                                    | Timer2         | •             | •             | •             |

|                                                    | Timer4         | •             | •             | •             |

|                                                    | Timer6         | •             | •             | •             |

|                                                    | -              |               |               |               |

# 1.1 Register and Bit Naming Conventions

### 1.1.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

#### 1.1.2 BIT NAMES

There are two variants for bit names:

- · Short name: Bit function abbreviation

- · Long name: Peripheral abbreviation + short name

#### 1.1.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is RegisterNamebits.ShortName. For example, the enable bit, EN, in the COG1CON0 register can be set in C programs with the instruction COG1CON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

### 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the <code>BSF COG1CON0, G1EN</code> instruction.

#### 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

```

COG1CON0bits.MD = 0x5;

```

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name MD2, and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

#### Example 1:

```

MOVLW ~ (1<<G1MD1)

ANDWF COG1CONO,F

MOVLW 1<<G1MD2 | 1<<G1MD0

IORWF COG1CONO,F

```

### Example 2:

| BSF | COG1CON0, G1MD2 |

|-----|-----------------|

| BCF | COG1CON0, G1MD1 |

| BSF | COG1CON0, G1MD0 |

# 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

### 1.1.3.1 Status, Interrupt and Mirror Bits

Status, interrupt enables, interrupt flags and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique, so there is no prefix or short name variant.

### 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

FIGURE 1-1: PIC16(L)F1718 BLOCK DIAGRAM

TABLE 1-2: PIC16(L)F1718 PINOUT DESCRIPTION

| Name                             | Function | Input<br>Type | Output<br>Type | Description                                  |

|----------------------------------|----------|---------------|----------------|----------------------------------------------|

| RA0/AN0/C1IN0-/C2IN0-/           | RA0      | TTL/ST        | CMOS           | General purpose I/O.                         |

| CLCINO <sup>(1)</sup>            | AN0      | AN            | _              | ADC Channel 0 input.                         |

|                                  | C1IN0-   | AN            | _              | Comparator C2 negative input.                |

|                                  | C2IN0-   | AN            | _              | Comparator C3 negative input.                |

|                                  | CLCIN0   | TTL/ST        | _              | Configurable Logic Cell source input.        |

| RA1/AN1/C1IN1-/C2IN1-/           | RA1      | TTL/ST        | CMOS           | General purpose I/O.                         |

| OPA1OUT/CLCIN1 <sup>(1)</sup>    | AN1      | AN            | _              | ADC Channel 1 input.                         |

|                                  | C1IN1-   | AN            | _              | Comparator C1 negative input.                |

|                                  | C2IN1-   | AN            | _              | Comparator C2 negative input.                |

|                                  | OPA1OUT  | _             | AN             | Operational Amplifier 1 output.              |

|                                  | CLCIN1   | TTL/ST        | _              | Configurable Logic Cell source input.        |

| RA2/AN2/VREF-/C1IN0+/C2IN0+/     | RA2      | TTL/ST        | CMOS           | General purpose I/O.                         |

| DAC1OUT1                         | AN2      | AN            | _              | ADC Channel 2 input.                         |

|                                  | VREF-    | AN            | _              | ADC Negative Voltage Reference input.        |

|                                  | C1IN0+   | AN            | _              | Comparator C2 positive input.                |

|                                  | C2IN0+   | AN            | _              | Comparator C3 positive input.                |

|                                  | DAC1OUT1 | _             | AN             | Digital-to-Analog Converter output.          |

| RA3/AN3/VREF+/C1IN1+             | RA3      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | AN3      | AN            | _              | ADC Channel 3 input.                         |

|                                  | VREF+    | AN            | _              | ADC Voltage Reference input.                 |

|                                  | C1IN1+   | AN            | _              | Comparator C1 positive input.                |

| RA4/OPA1IN+/T0CKI <sup>(1)</sup> | RA4      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | OPA1IN+  | AN            | _              | Operational Amplifier 1 non-inverting input. |

|                                  | T0CKI    | TTL/ST        | _              | Timer0 gate input.                           |

| RA5/AN4/OPA1IN-/DAC2OUT1/        | RA5      | TTL/ST        | CMOS           | General purpose I/O.                         |

| <del>SS</del> <sup>(1)</sup>     | AN4      | AN            | _              | ADC Channel 4 input.                         |

|                                  | OPA1IN-  | AN            | _              | Operational Amplifier 1 inverting input.     |

|                                  | DAC2OUT1 | _             | AN             | Digital-to-Analog Converter output.          |

|                                  | SS       | TTL/ST        | _              | Slave Select enable input.                   |

| RA6/OSC2/CLKOUT                  | RA6      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | OSC2     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).        |

|                                  | CLKOUT   | _             | CMOS           | Fosc/4 output.                               |

| RA7/OSC1/CLKIN                   | RA7      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | OSC1     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).        |

|                                  | CLKIN    | ST            | _              | External clock input (EC mode).              |

| RB0/AN12/C2IN1+/ZCD/             | RB0      | TTL/ST        | CMOS           | General purpose I/O.                         |

| COGIN <sup>(1)</sup>             | AN12     | AN            | _              | ADC Channel 12 input.                        |

|                                  | C2IN1+   | AN            | _              | Comparator C2 positive input.                |

|                                  | ZCD      | AN            | _              | Zero-Cross Detection Current Source/Sink.    |

|                                  | COGIN    | TTL/ST        | CMOS           | Complementary Output Generator input.        |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$

HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

<sup>2:</sup> All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

<sup>3:</sup> These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

TABLE 1-2: PIC16(L)F1718 PINOUT DESCRIPTION (CONTINUED)

| Name                                            | Function | Input<br>Type    | Output<br>Type | Description                                  |

|-------------------------------------------------|----------|------------------|----------------|----------------------------------------------|

| RB1/AN10/C1IN3-/C2IN3-/                         | RB1      | TTL/ST           | CMOS           | General purpose I/O.                         |

| OPA2OUT                                         | AN10     | AN               | _              | ADC Channel 10 input.                        |

|                                                 | C1IN3-   | AN               | _              | Comparator C1 negative input.                |

|                                                 | C2IN3-   | AN               | _              | Comparator C2 negative input.                |

|                                                 | OPA2OUT  | _                | AN             | Operational Amplifier 2 output.              |

| RB2/AN8/OPA2IN-                                 | RB2      | TTL/ST           | CMOS           | General purpose I/O.                         |

|                                                 | AN8      | AN               | _              | ADC Channel 8 input.                         |

|                                                 | OPA2IN-  | AN               | _              | Operational Amplifier 2 inverting input.     |

| RB3/AN9/C1IN2-/C2IN2-/                          | RB3      | TTL/ST           | CMOS           | General purpose I/O.                         |

| OPA2IN+                                         | AN9      | AN               | _              | ADC Channel 9 input.                         |

|                                                 | C1IN2-   | AN               | _              | Comparator C1 negative input.                |

|                                                 | C2IN2-   | AN               | _              | Comparator C2 negative input.                |

|                                                 | OPA2IN+  | AN               | _              | Operational Amplifier 2 non-inverting input. |

| RB4/AN11                                        | RB4      | TTL/ST           | CMOS           | General purpose I/O.                         |

|                                                 | AN11     | AN               | _              | ADC Channel 11 input.                        |

| RB5/AN13/T1G <sup>(1)</sup>                     | RB5      | TTL/ST           | CMOS           | General purpose I/O.                         |

|                                                 | AN13     | AN               | _              | ADC Channel 13 input.                        |

|                                                 | T1G      | TTL/ST           | _              | Timer1 gate input.                           |

| RB6/CLCIN2 <sup>(1)</sup> /ICSPCLK              | RB6      | TTL/ST           | CMOS           | General purpose I/O.                         |

|                                                 | CLCIN2   | TTL/ST           | _              | Configurable Logic Cell source input.        |

|                                                 | ICSPCLK  | ST               | _              | Serial Programming Clock.                    |

| RB7/DAC1OUT2/DAC2OUT2/                          | RB7      | TTL/ST           | CMOS           | General purpose I/O.                         |

| CLCIN3 <sup>(1)</sup> /ICSPDAT                  | DAC1OUT2 | _                | AN             | Digital-to-Analog Converter output.          |

|                                                 | DAC2OUT2 | _                | AN             | Digital-to-Analog Converter output.          |

|                                                 | CLCIN3   | TTL/ST           | _              | Configurable Logic Cell source input.        |

|                                                 | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                              |

| RC0/T1CKI <sup>(1)</sup> /SOSCO                 | RC0      | TTL/ST           | CMOS           | General purpose I/O.                         |

|                                                 | T1CKI    | TTL/ST           | _              | Timer1 clock input.                          |

|                                                 | sosco    | XTAL             | XTAL           | Secondary Oscillator Connection.             |

| RC1/SOSCI/CCP2 <sup>(1)</sup>                   | RC1      | TTL/ST           | CMOS           | General purpose I/O.                         |

|                                                 | SOSCI    | XTAL             | XTAL           | Secondary Oscillator Connection.             |

|                                                 | CCP2     | TTL/ST           | _              | Capture input                                |

| RC2/AN14/CCP1 <sup>(1)</sup>                    | RC2      | TTL/ST           | CMOS           | General purpose I/O.                         |

|                                                 | AN14     | AN               |                | ADC Channel 14 input.                        |

|                                                 | CCP1     | TTL/ST           | _              | Capture input                                |

| RC3/AN15/SCK <sup>(1)</sup> /SCL <sup>(1)</sup> | RC3      | TTL/ST           | CMOS           | General purpose I/O.                         |

|                                                 | AN15     | AN               | _              | ADC Channel 15 input.                        |

|                                                 | SCK      | TTL/ST           | _              | SPI clock input                              |

|                                                 | SCL      | I <sup>2</sup> C | _              | I <sup>2</sup> C clock input.                |

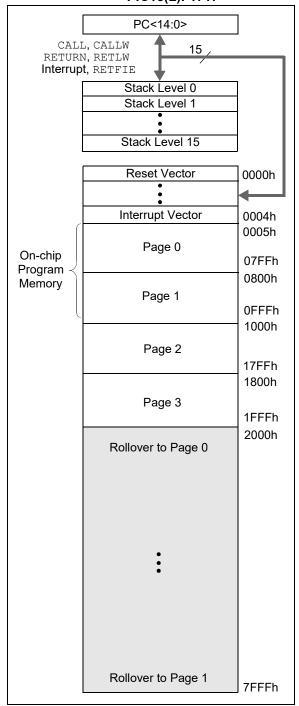

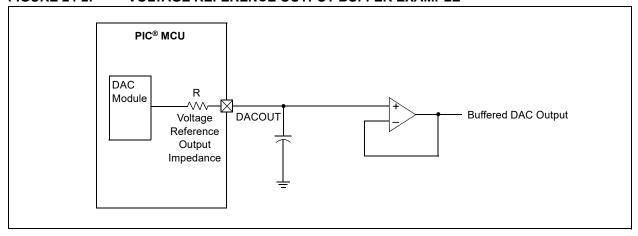

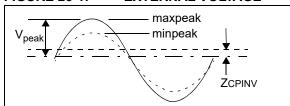

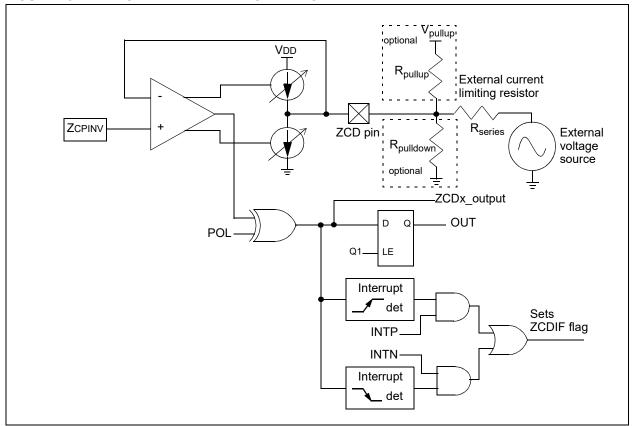

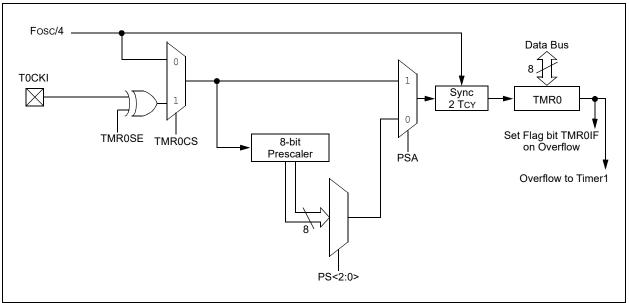

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C