## **VFC110**

# High-Frequency VOLTAGE-TO-FREQUENCY CONVERTER

## **FEATURES**

- HIGH-FREQUENCY OPERATION: 4MHz FS max

- EXCELLENT LINEARITY: ±0.02% typ at 2MHz

- PRECISION 5V REFERENCE

- DISABLE PIN

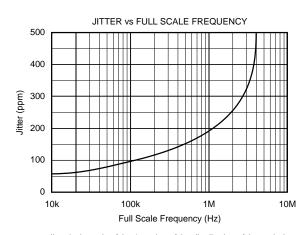

- LOW JITTER

## **APPLICATIONS**

- INTEGRATING A/D CONVERSION

- PROCESS CONTROL

- VOLTAGE ISOLATION

- VOLTAGE-CONTROLLED OSCILLATOR

- FM TELEMETRY

## **DESCRIPTION**

The VFC110 voltage-to-frequency converter is a thirdgeneration VFC offering improved features and performance. These include higher frequency operation, an on-board precision 5V reference and a Disable function.

The precision 5V reference can be used for offsetting the VFC transfer function, as well as exciting transducers or bridges. The Enable pin allows several VFCs' outputs to be paralleled, multiplexed, or simply to shut off the VFC. The open-collector frequency

output is TTL/CMOS-compatible. The output may be isolated by using an opto-coupler or transformer.

Internal input resistor, one-shot and integrator capacitors simplify applications circuits. These components are trimmed for a full-scale output frequency of 4MHz at 10V input. No additional components are required for many applications.

The VFC110 is packaged in plastic and ceramic 14-pin DIPs. Industrial and military temperature range gradeouts are available.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

At  $T_A$  = +25°C and  $V_S$  = ±15V, unless otherwise noted.

|                                                                                                                                                                                                |                                                                                                                                                                                                                 | VFC110BG   |                            | VFC110AG/SG/AP          |            |                           |               |                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------|-------------------------|------------|---------------------------|---------------|---------------------------------|

| PARAMETER                                                                                                                                                                                      | CONDITIONS                                                                                                                                                                                                      | MIN        | TYP                        | MAX                     | MIN        | TYP                       | MAX           | UNITS                           |

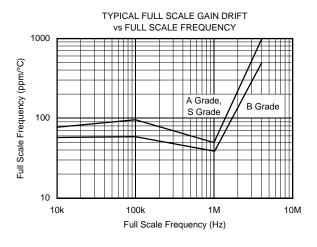

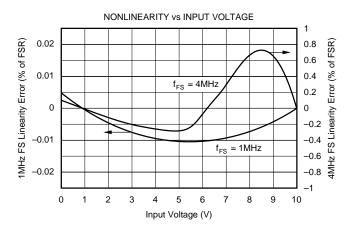

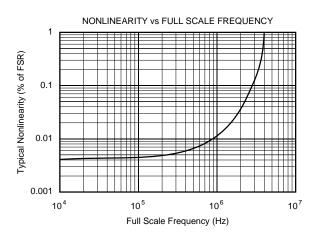

| VOLTAGE-TO-FREQUENCY OPERATION  Nonlinearity <sup>(1)</sup> : $f_{FS} = 100 \text{kHz}$ $f_{FS} = 1 \text{MHz}$ $f_{FS} = 2 \text{MHz}$ $f_{FS} = 4 \text{MHz}$ Gain Error, $f = 1 \text{MHz}$ | $C_{OS} = 2.2 n F, R_{IN} = 44 k \Omega$<br>$C_{OS} = 150 p F, R_{IN} = 40 k \Omega$<br>$C_{OS} = 56 p F, R_{IN} = 34 k \Omega$<br>$C_{OS} = (Int), R_{IN} = (Int)$<br>$C_{OS} = 150 p F, R_{IN} = 40 k \Omega$ |            | 0.005<br>0.01<br>0.02<br>1 | 0.01<br>0.05            |            | 0.01                      | 0.05<br>0.1   | %FS<br>%FS<br>%FS<br>%FS<br>%   |

| Gain Drift, f = 1MHz<br>Relative to V <sub>REF</sub><br>PSRR                                                                                                                                   | Specified Temp Range<br>Specified Temp Range<br>V <sub>S</sub> = ±8V to ±18V                                                                                                                                    |            | 50                         | 50<br>0.05              |            | 100                       | 100<br>0.1    | ppm/°C<br>ppm/°C<br>%/V         |

| INPUT Full Scale Input Current I <sub>B</sub> — (Inverting Input) I <sub>B</sub> + (Non-Inverting Input) Vos Vos Vos Drift                                                                     | Specified Temp Range                                                                                                                                                                                            |            | 250<br>15<br>250           | 500<br>60<br>3          |            | * 20<br>*                 | *<br>100<br>3 | μΑ<br>nA<br>nA<br>mV<br>μV/°C   |

| INTEGRATOR AMPLIFIER OUTPUT Output Voltage Range Output Current Drive Capacitive Load                                                                                                          | $R_L = 2k\Omega$<br>No Oscillations                                                                                                                                                                             | -0.2<br>5  | 20<br>10                   | +V <sub>S</sub> - 4     | *          | *<br>10                   | *             | V<br>mA<br>nF                   |

| COMPARATOR INPUT I <sub>B</sub> (Input Bias Current) Trigger Voltage Input Voltage Range                                                                                                       |                                                                                                                                                                                                                 | <b>-</b> 5 | −5<br>±50                  | +V <sub>S</sub>         | *          | *                         | *             | μA<br>mV<br>V                   |

| OPEN COLLECTOR OUTPUT  V <sub>O</sub> Low  I <sub>LEAKAGE</sub> Fall Time  Delay to Rise  Settling Time                                                                                        | To Specified Linearity for a<br>Full-Scale Input Step                                                                                                                                                           |            | 0.1<br>25<br>25<br>One F   | 0.4<br>1<br>Pulse of Ne | w Frequenc | *<br>*<br>*<br>y Plus 1μs | *             | V<br>μA<br>ns<br>ns             |

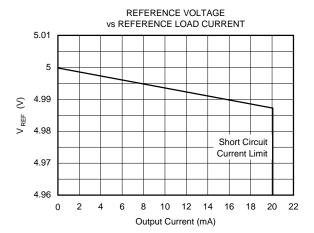

| REFERENCE VOLTAGE Voltage Voltage Drift Load Regulation PSRR Current Limit                                                                                                                     | $I_O = 0$ to 10mA<br>$V_S = \pm 8V$ to $\pm 18V$<br>Short Circuit                                                                                                                                               | 4.97<br>15 | 5<br>2<br>5<br>20          | 5.03<br>20<br>10        | *          | * * * *                   | *<br>50<br>*  | V<br>ppm/°C<br>mV<br>mV/V<br>mA |

| ENABLE INPUT  V <sub>HIGH</sub> (f <sub>OUT</sub> Enabled)  V <sub>LOW</sub> (f <sub>OUT</sub> Disabled)  I <sub>HIGH</sub> I <sub>LOW</sub>                                                   | Specified Temp Range<br>Specified Temp Range                                                                                                                                                                    | 2          | 0.1<br>1                   | 0.4                     | *          | *                         | *             | V<br>V<br>μΑ<br>μΑ              |

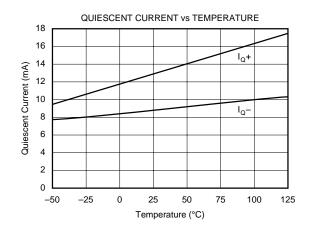

| POWER SUPPLY<br>Voltage, ±V <sub>S</sub><br>Current                                                                                                                                            |                                                                                                                                                                                                                 | ±8         | ±15<br>13                  | ±18<br>16               | *          | *                         | *             | V<br>mA                         |

| TEMPERATURE RANGE Specified AG, BG, AP SG Storage                                                                                                                                              |                                                                                                                                                                                                                 | -25<br>-55 |                            | +85<br>+125             | *          |                           | *             | °C                              |

| AG, BG, SG<br>AP                                                                                                                                                                               |                                                                                                                                                                                                                 | -65<br>-40 |                            | +150<br>+125            | *          |                           | *             | °C<br>°C                        |

<sup>\*</sup> Same specifications as VFC110BG.

NOTE: (1) Nonlinearity measured from 1V to 10V input.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

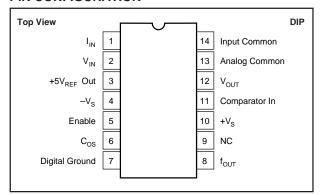

#### **PIN CONFIGURATION**

## **ABSOLUTE MAXIMUM RATINGS**

| Power Supply Voltages (+V <sub>S</sub> to -V <sub>S</sub> ) | 40V                    |

|-------------------------------------------------------------|------------------------|

| f <sub>OUT</sub> Sink Current                               | 50mA                   |

| Comparator In Voltage                                       | –5V to +V <sub>S</sub> |

| Enable Input                                                |                        |

| Integrator Common-Mode Voltage                              |                        |

| Integrator Differential Input Voltage                       |                        |

| Integrator Out (short-circuit)                              |                        |

| V <sub>REF</sub> Out (short-circuit)                        |                        |

| Operating Temperature Range                                 |                        |

| G Package                                                   | –55°C to +125°C        |

| P Package                                                   |                        |

| Storage Temperature                                         |                        |

| G Package                                                   | 60°C to +150°C         |

| P Package                                                   |                        |

| Lead Temperature (soldering, 10s)                           |                        |

## **PACKAGE INFORMATION**

| PRODUCT  | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|--------------------|------------------------------------------|

| VFC110AG | 14-Pin Ceramic DIP | 169                                      |

| VFC110BG | 14-Pin Ceramic DIP | 169                                      |

| VFC110SG | 14-Pin Ceramic DIP | 169                                      |

| VFC110AP | 14-Pin Plastic DIP | 010                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

## **ORDERING INFORMATION**

| PRODUCT  | PACKAGE     | TEMPERATURE<br>RANGE |

|----------|-------------|----------------------|

| VFC110AG | Ceramic DIP | –25°C to +85°C       |

| VFC110BG | Ceramic DIP | –25°C to +85°C       |

| VFC110SG | Ceramic DIP | -55°C to +125°C      |

| VFC110AP | Plastic DIP | -25°C to +85°C       |

# **TYPICAL PERFORMANCE CURVES**

At  $T_A = +25$ °C,  $V_S = \pm 15$ V, unless otherwise noted.

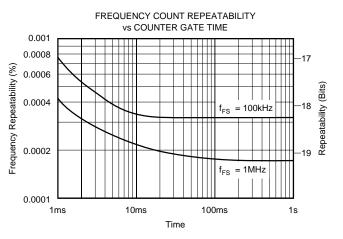

Jitter is the ratio of the  $1\sigma$  value of the distribution of the period (1/f\_OUT, max) to the mean of the period.

This graph describes the low frequency stability of the VFC110: the ratio of the  $1\sigma$  point of the distribution of 100 runs (where each mean frequency came from 1000 readings for each gate time) to the overall mean frequency.

# TYPICAL PERFORMANCE CURVES (CONT)

At  $T_A = +25$ °C,  $V_S = \pm 15$ V, unless otherwise noted.

## **OPERATION**

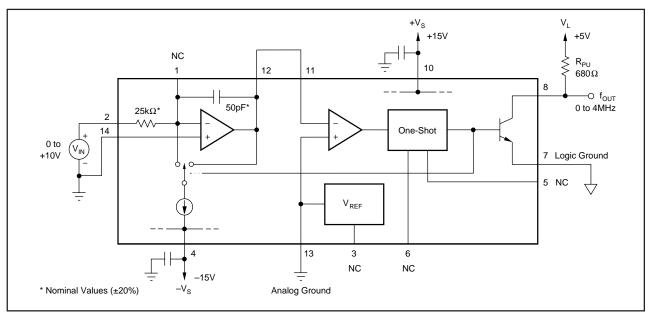

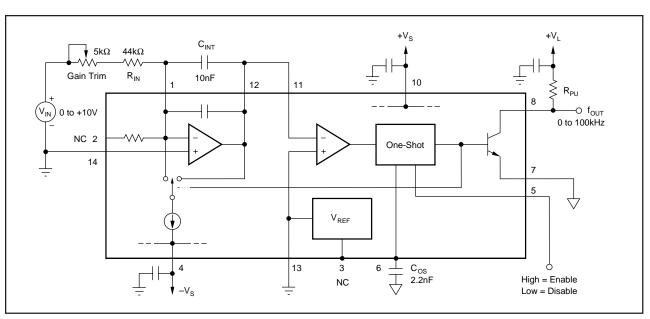

Figure 1 shows the connections required for operation at a full-scale output frequency of 4MHz. Only power supply bypass capacitors and an output pull-up resistor,  $R_{PU}$ , are required for this mode of operation. A 0V to 10V input voltage produces a 0Hz to 4MHz output frequency. The internal input resistor, one-shot and integrator capacitors set the full-scale output frequency. The input is applied to the summing junction of the integrator amplifier through the  $25k\Omega$  internal input resistor. Pin 14 (the non-inverting amplifier input) should be referred directly to the negative side of  $V_{\rm IN}$ . The common-mode range of the integrating amplifier is limited to approximately -1V to +1V referred to analog ground. This allows the non-inverting input to Kelvin-sense the common connection of  $V_{\rm IN}$ , easily accommodating any

ground-drop errors. The input impedance loading  $V_{\rm IN}$  is equal to the input resistor—approximately 25k $\Omega$ .

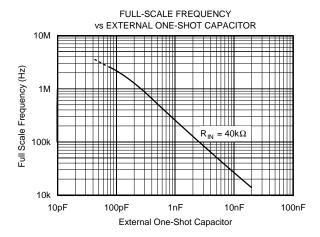

#### **OPERATION AT LOWER FREQUENCIES**

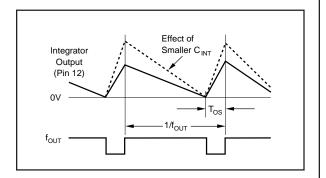

The VFC110 can be operated at lower frequencies simply by limiting the input voltage to less than the nominal 10V full-scale input. To maintain a 10V FS input and highest accuracy, however, external components are required (see Table I). Small adjustments may be required in the nominal values indicated. Integrator and one-shot capacitors are added in parallel to internal capacitors. Figure 2 shows the connections required for 100kHz full scale output. The one-shot capacitor,  $C_{\rm OS}$ , should be connected to logic ground. The one-shot connection (pin 6) is not short-circuit protected. Short-circuits to ground may damage the device.

5

FIGURE 1. 4MHz Full-Scale Operation.

**VFC110**

The integrator capacitor's value does not directly affect the output frequency, but determines the magnitude of the voltage swing on the integrator's output. Using a  $C_{\rm INT}$  equal to  $C_{\rm OS}$  provides an integrator output swing from 0V to approximately 1.5V.

## COMPONENT SELECTION

Selection of the external resistor and capacitor type is important. Temperature drift of an external input resistor and one-shot capacitor will affect temperature stability of the output frequency. NPO ceramic capacitors will normally produce the best results. Silver-mica types will result in slightly higher drift, but may be adequate in many applications. A low temperature coefficient film resistor should be used for  $R_{\rm IN}$ .

The integrator capacitor serves as a "charge bucket," where charge is accumulated from the input,  $V_{IN}$ , and that charge is drained during the one-shot period. While the size of the bucket (capacitor value) is not critical, it must not leak. Capacitor leakage or dielectric absorption can affect the

| FULL-SCALE                 | EXTERNAL COMPONENTS |       |                  |  |

|----------------------------|---------------------|-------|------------------|--|

| FREQUENCY, f <sub>FS</sub> | R <sub>IN</sub>     | Cos   | C <sub>INT</sub> |  |

| 4MHz                       | *                   | *     | *                |  |

| 2MHz                       | 34kΩ                | 56pF  | *                |  |

| 1MHz                       | 40kΩ                | 150pF | *                |  |

| 500kHz                     | 58kΩ                | 330pF | 2nF              |  |

| 100kHz                     | 44kΩ                | 2.2nF | 10nF             |  |

| 50kHz                      | 88kΩ                | 2.2nF | 0.1μF            |  |

| 10kHz                      | 44kΩ                | 22nF  | 0.1μF            |  |

<sup>\*</sup> Use internal component only.

The values given were determined empirically to give the optimal performance, taking into consideration tradeoffs between linearity and jitter for each given full scale frequency of operation. The capacitors listed were chosen from standard values of NPO ceramic type capacitors while the resistor values were rounded off. Larger  $C_{\text{INT}}$  values may improve linearity, but may also increase frequency noise.

TABLE I. Component Selection Table.

linearity and offset of the transfer function. High-quality ceramic capacitors can be used for values less than  $0.01\mu F$ . Use caution with higher value ceramic capacitors. High-k ceramic capacitors may have voltage nonlinearities which can degrade overall linearity. Polystyrene, polycarbonate, or mylar film capacitors are superior for high values.

#### **PULL-UP RESISTOR**

The VFC110's frequency output is an open-collector transistor. A pull-up resistor should be connected from  $f_{OUT}$  to the logic supply voltage,  $+V_{\rm L}$ . The output transistor is On during the one-shot period, causing the output to be a logic Low. The current flowing in this resistor should be limited to 8mA to assure a 0.4V maximum logic Low. The value chosen for the pull-up resistor may depend on the full-scale frequency and capacitance on the output line. Excessive capacitance on  $f_{\rm OUT}$  will cause a slow, rounded rising edge at the end of an output pulse. This effect can be minimized by using a pull-up resistor which sets the output current to its maximum of 8mA. The logic power supply can be any positive voltage up to  $+V_{\rm S}$ .

#### **ENABLE PIN**

If left unconnected, the Enable input will assume a logic High level, enabling operation. Alternatively, the Enable input may be connected directly to  $+V_S$ . Since an internal pull-up current is included, the Enable input may be driven by an open-collector logic signal.

A logic Low at the Enable input causes output pulses to cease. This is accomplished by interrupting the signal path through the one-shot circuitry. While disabled, all circuitry remains active and quiescent current is unchanged. Since no reset current pulses can occur while disabled, any positive input voltage will cause the integrator op amp to ramp negatively and saturate at its most negative output swing of approximately –0.7V.

FIGURE 2. 100kHz Full-Scale Operation.

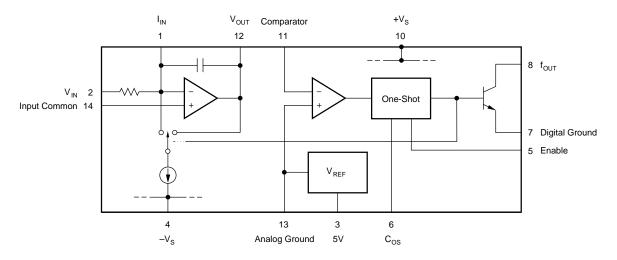

#### PRINCIPLE OF OPERATION

The VFC110 uses a charge-balance technique to achieve high accuracy. The heart of this technique is an analog integrator formed by the integrator op amp, feedback capacitor  $C_{\text{INT}}$ , and input resistor  $R_{\text{IN}}$ . The integrator's output voltage is proportional to the charge stored in  $C_{\text{INT}}$ . An input voltage develops an input current of  $V_{\text{IN}}/R_{\text{IN}}$ , which is forced to flow through  $C_{\text{INT}}$ . This current charges  $C_{\text{INT}}$ , causing the integrator output voltage to ramp negatively.

When the output of the integrator ramps to 0V, the comparator trips, triggering the one-shot. This connects the reference current,  $I_{REF}$ , to the integrator input during the one-shot period,  $T_{OS}$ . This switched current causes the integrator output to ramp positively until the one-shot period ends. Then the cycle starts again.

The oscillation is regulated by the balance of current (or charge) between the input current and the time-averaged

reset current. The equation of current balance is

$$I_{IN} = I_{REF} \bullet Duty Cycle$$

$V_{IN}/R_{IN} = I_{REF} \bullet f_{OUT} \bullet T_{OUT}$

where  $T_{_{\rm O}}$  is the one-shot period and  $f_{_{\rm OUT}}$  is the oscillation frequency.

When the Enable input receives a logic High (greater than +2V), a reset current cycle is initiated (causing  $f_{OUT}$  to go Low). The integrator ramps positively and normal operation is established. The time required for the output frequency to stabilize is equal to approximately one cycle of the final output frequency plus  $1\mu s$ .

Using the Enable input, several VFCs' outputs can be connected to a single output line. All disabled VFCs will have a high output impedance; one active VFC can then transmit on the output line. Since the disabled VFCs are not oscillating, they cannot interfere or "lock" with the operating VFC. Locking can occur when one VFC operates at nearly the same frequency as—or a multiple of—a nearby VFC. Coupling between the two may cause them to lock to the same or exact multiple frequency. It then takes a small incremental input voltage change to unlock them. Locking cannot occur when unneeded VFCs are disabled.

#### REFERENCE VOLTAGE

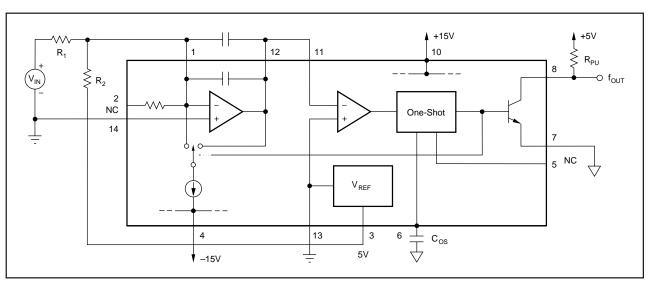

The  $V_{REF}$  output is useful for offsetting the transfer function and exciting sensors. Figure 3 shows  $V_{REF}$  used to offset the transfer function of the VFC110 to achieve a bipolar input voltage range. Sub-surface zener reference circuitry is used for low noise and excellent temperature drift. Output current is specified to 10mA and current-limited to approximately 20mA. Excessive or variable loads on  $V_{REF}$  can decrease frequency stability due to internal heating.

#### MEASURING THE OUTPUT FREQUENCY

To complete an integrating A/D conversion, the output frequency of the VFC110 must be counted. Simple frequency counting is accomplished by counting output pulses for a reference time (usually derived from a crystal oscilla-

7

FIGURE 3. Offsetting the Frequency Output.

tor). This can be implemented with counter/timer peripheral chips available for many popular microprocessor families. Many micro-controllers have counter inputs that can be programmed for frequency measurement.

Since  $f_{OUT}$  is an open-collector device, the negative-going edge provides the fastest logic transition. Clocking the counter on the falling edge will provide the best results in noisy environments.

Frequency can also be measured by accurately timing the period of one or more cycles of the VFC's output. Frequency must then be computed since it is inversely proportional to the measured period. This measurement technique can provide higher measurement resolution in short conversion times. It is the method used in most high-performance laboratory frequency counters. It is usually necessary to offset the transfer function so 0V input causes a finite frequency out. Otherwise the output period (and therefore the conversion time) approaches infinity.

#### FREQUENCY NOISE

Frequency noise (small random variation in the output frequency) limits the useful resolution of fast frequency measurement techniques. Long measurement time averages the effect of frequency noise and achieves the maximum useful resolution. The VFC110 is designed to minimize frequency noise and allows improved useful resolution with short measurement times. The typical curve "Frequency Count Repeatability vs Counter Gate Time" shows the effect of noise as the counter gate time is varied. It shows the one

standard deviation  $(1\sigma)$  count variation (as a percentage of FS counts) versus counter gate time.

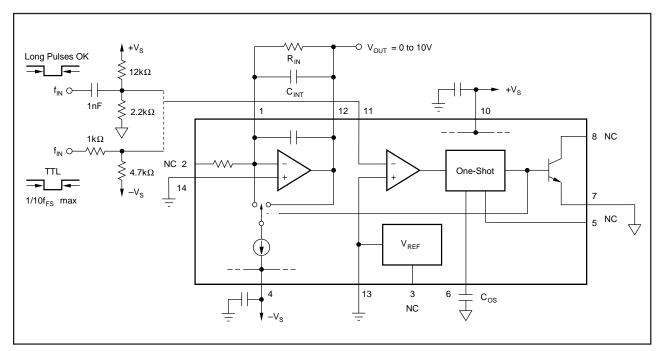

#### FREQUENCY-TO-VOLTAGE CONVERSION

The VFC110 can also be connected as a frequency-to-voltage converter (Figure 4). Input frequency pulses are applied to the comparator input. A negative-going pulse crossing 0V initiates a reference current pulse which is averaged by the integrator op amp. The values of the one-shot capacitor and feedback resistor (same as  $R_{\rm IN}$ ) are determined with Table I. The input frequency pulse must not remain negative for longer than the duration of the one-shot period. Figure 4 shows the required timing to assure this. If the negative-going input frequency pulses are longer in duration, the capacitive coupling circuit shown can be used. Level shift or capacitive coupling circuitry should not provide pulses which go lower than  $-5\mathrm{V}$  or damage to the comparator input may occur.

This frequency-to-voltage converter operates by averaging (filtering) the reference current pulses triggered on every falling edge at the frequency input. Voltage ripple with a frequency equal to the input will be present in the output voltage. The magnitude of this ripple voltage is inversely proportional to the integrator capacitor. The ripple can be made arbitrarily small with a large capacitor, but at the sacrifice of settling time. The R-C time constant of  $C_{\rm INT}$  and  $R_{\rm IN}$  determine the settling behavior. A better compromise between output ripple and settling time can be achieved by adding a low-pass filter following the voltage output.

FIGURE 4. Frequency-to-Voltage Conversion.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.