# **MPQ5031** Single Port USB PD Controller for Source Only, AEC-Q100 Qualified

## DESCRIPTION

The MPQ5031 is a USB power delivery controller compatible with Type-C 2.0 and USB PD3.0 specifications. It targets DFP (provider) applications, such as charging-only USB PD ports and USB hubs.

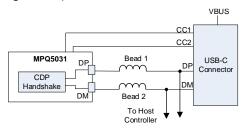

The device is backward compatible, supporting DCP schemes for Quick Charge 3.0, battery charging specifications (BC1.2), Apple divider mode, Huawei FCP, and 1.2V/1.2V mode without outside user interaction. It also supports BC1.2 CDP handshaking. The I<sup>2</sup>C interface and GPIO pins provide good communication with an external power converter.

The MPQ5031 supports up to 100W PD power and PPS as well. It can flexibly configure the PDO list, select slave devices, configure charging protocols, and set the protection mode.

Two NTC pins can be used to monitor for abnormal temperature rise, such as on the Type-C receptacle and PCB board. Power sharing functionality supports smart power budget management between two USB PD ports. PDO capability is reduced when the car battery voltage is low. High-voltage I/O pins support short to battery and short to VBUS protection for the DC/DC converter.

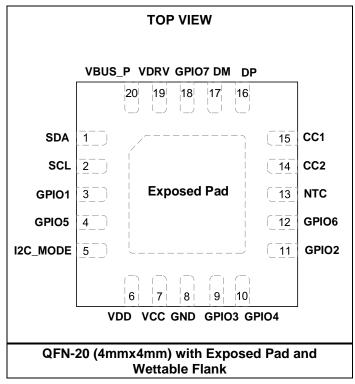

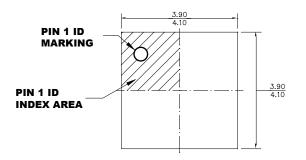

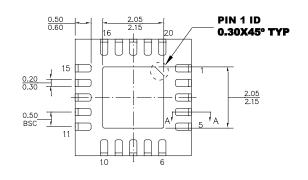

The MPQ5031 is available in a QFN-20 (4mmx4mm) package with wettable flanks.

## FEATURES

- Supports a 3.3V to 21V Bus Voltage Range

- 4.6V to 5.5V VCC Supply Voltage Range

- Integrated Physical Layer for BMC

- Integrated Protocol Layer

- Integrated Policy Engine

- Low Standby I<sub>Q</sub>: 100µA

- Supports One Type-C DFP Port with USB PD3.0 and PPS

- Supports DCP Schemes for BC1.2, 3A Divider, and 1.2V/1.2V Mode

- Supports QC3.0, Huawei FCP

- VBUS Isolation N-Channel MOSFET Driver

- EN Off Timer Up to 120 Minutes

- I<sup>2</sup>C Master/Slave Interface and Interrupt

- Load-Shedding with NTC or Battery Low Detection Function

- High-Voltage Pins for CC1, CC2, DP, and DM

- Integrated High-Voltage V<sub>CONN</sub> Supply Power Switch

- Passed 60W USB-IF PPS Certification with the MPQ4230 (TID: 2313)

- Passed 100W USB-IF PPS Certification with the MPQ4214 (TID: 2316)

- Available in a QFN-20 (4mmx4mm) Package with Wettable Flanks

- Available in Automotive AEC-Q100 Grade 1

## APPLICATIONS

- USB Power Delivery (Provider) Charging

Ports

- USB PD Hubs

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

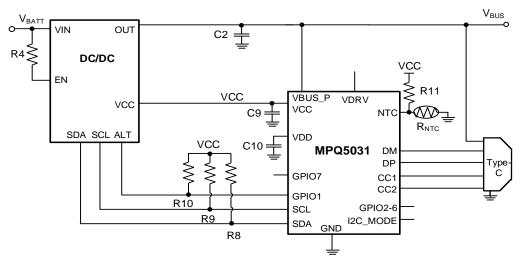

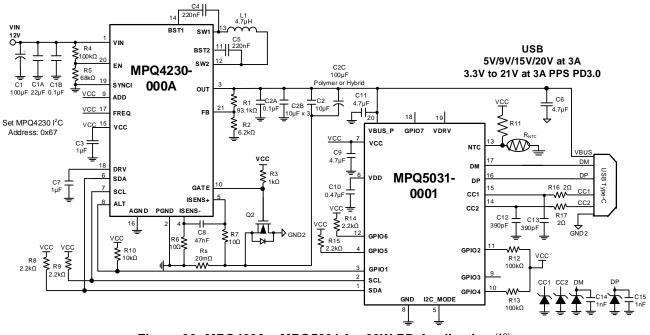

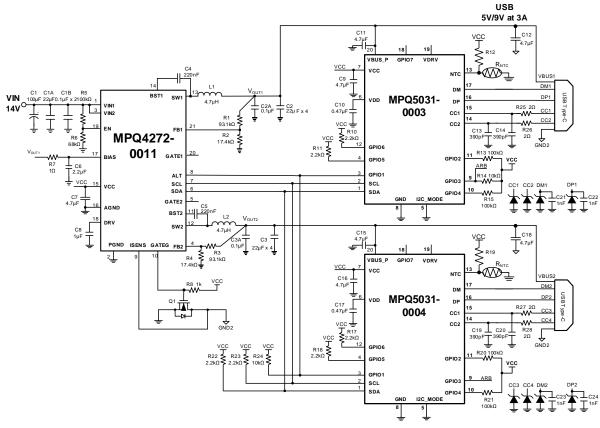

## **TYPICAL APPLICATION**

### **ORDERING INFORMATION**

| Part Number*           | Package             | Top Marking | MSL |

|------------------------|---------------------|-------------|-----|

| MPQ5031GRE-0001-AEC1   |                     |             |     |

| MPQ5031GRE-0002-AEC1   |                     |             |     |

| MPQ5031GRE-0003-AEC1   | QFN-20<br>(4mmx4mm) |             |     |

| MPQ5031GRE-0004-AEC1   |                     | See Below   | 1   |

| MPQ5031GRE-0013-AEC1   |                     |             |     |

| MPQ5031GRE-0015-AEC1   |                     |             |     |

| MPQ5031GRE-xxxx-AEC1** |                     |             |     |

| EVKT-MPQ5031           | -                   | -           | -   |

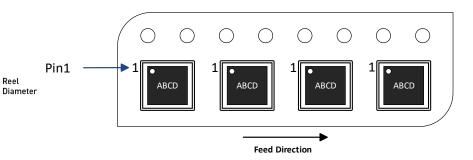

\* For Tape & Reel, add suffix –Z (e.g. MPQ5031GRE-xxxx-AEC1–Z).

\*\* "xxxx" is the configuration code identifier for the register setting stored in the OTP. Each "x" can be a hexadecimal value between 0 and F.

## **TOP MARKING**

## MPSYWW MP5031 LLLLLL E

MPS: MPS prefix Y: Year code WW: Week code MP5031: Part number LLLLLL: Lot number E: Wettable lead flank

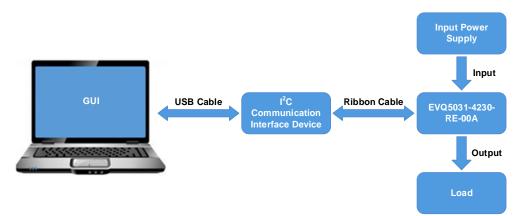

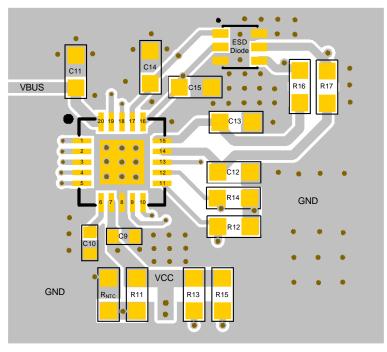

## **EVALUATION KIT EVKT-MPQ5031**

EVKT-MPQ5031 kit contents (items listed below can be ordered separately):

| # | Part Number              | Item                                                                                           | Quantity |

|---|--------------------------|------------------------------------------------------------------------------------------------|----------|

| 1 | EVQ5031-4230-RE-00A      | MPQ5031 + MPQ4230 evaluation board.                                                            | 1        |

| 2 | EVKT-USBI2C-02 bag       | Includes USB to I <sup>2</sup> C communication interface, one USB cable, and one ribbon cable. | 1        |

| 3 | MPQ5031GRE-0000-<br>AEC1 | IC with default configuration. Can be used for OTP configurations.                             | 2        |

### Order directly from MonolithicPower.com or our distributors.

Figure 1: EVKT-MPQ5031 Evaluation Kit Set-Up

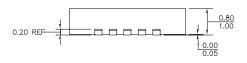

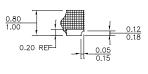

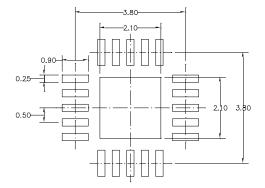

## PACKAGE REFERENCE

## **PIN FUNCTIONS**

| Pin #          | Name     | I/O           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | SDA      | Bidirectional | I <sup>2</sup> C data line.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2              | SCL      | Bidirectional | I <sup>2</sup> C clock signal input. When the MPQ5031 is selected as the master, SCL is an output pin.                                                                                                                                                                                                                                                                                                                                                    |

| 3              | GPIO1    | Bidirectional | <b>General purpose I/O 1.</b> See the GPIO register section on page 34 for more details.                                                                                                                                                                                                                                                                                                                                                                  |

| 4              | GPIO5    | Bidirectional | <b>General purpose I/O 5.</b> See the GPIO register section on page 35 for more details.                                                                                                                                                                                                                                                                                                                                                                  |

| 5              | I2C_MODE | Input         | <b>I<sup>2</sup>C operation mode setting.</b> Float or pull the I2C_MODE pin low to set the MPQ5031 as the I <sup>2</sup> C master. Pull this pin high to set the MPQ5031 as an I <sup>2</sup> C slave. When the MPQ5031 is set to I <sup>2</sup> C slave mode, the slave functions on GPIO5 and GPIO6 are disabled. Only pin 1 and pin 2 (SDA and SCL) are the I <sup>2</sup> C slave entrance. This pin has an internal 1M $\Omega$ pull-down resistor. |

| 6              | VDD      | Output        | Internal 1.8V LDO regulator output. Decouple with 0.47µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                       |

| 7              | VCC      | Input         | <b>5V power supply for all internal circuitry.</b> The MPQ5031 operates from a 4.5V to 5.5V input voltage. A 4.7 $\mu$ F ceramic capacitor (C <sub>IN</sub> ) must be used to supply power to the internal circuitry, including VCONN.                                                                                                                                                                                                                    |

| 8              | GND      | N/A           | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9              | GPIO3    | Bidirectional | <b>General purpose I/O 3.</b> See the GPIO register section on page 34 for more details.                                                                                                                                                                                                                                                                                                                                                                  |

| 10             | GPIO4    | Bidirectional | <b>General purpose I/O 4.</b> See the GPIO register section on page 33 for more details.                                                                                                                                                                                                                                                                                                                                                                  |

| 11             | GPIO2    | Bidirectional | <b>General purpose I/O 2.</b> See the GPIO register section on page 34 for more details.                                                                                                                                                                                                                                                                                                                                                                  |

| 12             | GPIO6    | Bidirectional | <b>General purpose I/O 6.</b> See the GPIO register section on page 35 for more details.                                                                                                                                                                                                                                                                                                                                                                  |

| 13             | NTC      | Input         | <b>External temperature-sense pin.</b> See the I <sup>2</sup> C register description on page 34 for the NTC trigger response.                                                                                                                                                                                                                                                                                                                             |

| 14             | CC2      | Bidirectional | <b>Configuration channel (CC).</b> CC2 is used for the discovery, configuration, and management of connections across a USB Type-C cable.                                                                                                                                                                                                                                                                                                                 |

| 15             | CC1      | Bidirectional | <b>Configuration channel (CC).</b> CC1 is used for the discovery, configuration, and management of connections across a USB Type-C cable.                                                                                                                                                                                                                                                                                                                 |

| 16             | DP       | Bidirectional | <b>D+ data line to USB connector.</b> The DP and DM pins are the input/output used for handshaking with portable devices.                                                                                                                                                                                                                                                                                                                                 |

| 17             | DM       | Bidirectional | <b>D- data line to USB connector.</b> The DP and DM pins are the input/output used for handshaking with portable devices.                                                                                                                                                                                                                                                                                                                                 |

| 18             | GPIO7    | Bidirectional | <b>General purpose I/O 7.</b> See the GPIO register section on page 35 for more details.                                                                                                                                                                                                                                                                                                                                                                  |

| 19             | VDRV     | Output        | <b>External N-Channel MOSFET gate driver signal.</b> When the sink is attached, VDRV drives the external N-channel MOSFET to turn on. Then power flows from the DC/DC output to the sink. When the sink is detached, VDRV drives the external N-channel MOSFET to turn off to isolate the power path.                                                                                                                                                     |

| 20             | VBUS_P   | Input         | Bus voltage sensing and discharge pin.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Exposed<br>pad | N/A      | N/A           | Exposed pad. Connect to ground when designing the PCB layout.                                                                                                                                                                                                                                                                                                                                                                                             |

### **ABSOLUTE MAXIMUM RATINGS** (1)

| VBUS_P0.3V (-5V for <10ns) to +24V<br>VDRVVBUS_P + 5V    |

|----------------------------------------------------------|

| VDD0.3V to +3V                                           |

| DM, DP, CC1, CC2                                         |

| 0.3V (-5V for <10ns) to +24V                             |

| GPIO4, GPIO6, NTC0.3V to +5.5V                           |

| All other pins0.3V to +6V                                |

| Continuous power dissipation $(T_A = 25^{\circ}C)^{(2)}$ |

| QFN-20 (4mmx4mm)2.1W                                     |

| Junction temperature                                     |

| Lead temperature                                         |

| Storage temperature65°C to +150°C                        |

### ESD Ratings

| Human body model (HE | 3M)   | ±2kV  |

|----------------------|-------|-------|

| Charged device model | (CDM) | ±750V |

### **Recommended Operating Conditions** <sup>(3)</sup>

| Power supply to VCC       | 5V/25mA                        |

|---------------------------|--------------------------------|

| Operating junction temp ( | T <sub>J</sub> )40°C to +125°C |

## Thermal Resistance <sup>(4)</sup> $\theta_{JA}$ $\theta_{JC}$

QFN-20 (4mmx4mm) ..... 60 ..... 12 ... °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the device may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB. The value of  $\theta_{JA}$  given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7 and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

## **ELECTRICAL CHARACTERISTICS**

### $V_{CC} = 5V$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$ , typical value is tested at $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                 | Symbol                  | Condition                                                                                                                                                                      | Min  | Тур  | Max  | Units    |

|-------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| Standby supply current                    | Іѕтв                    | VCC current, unattached                                                                                                                                                        |      | 100  |      | μA       |

| Supply current (on)                       | Ion                     | CC1 to GND with 5.1kΩ Rd (as defined by USB Type-C Cable and Connector Specification Revision 2.0, which can be downloaded from the official USB website at https://usb.org/). |      | 3.5  | 4.5  | mA       |

| Thermal shutdown (5)                      | T <sub>OTP_R</sub>      |                                                                                                                                                                                |      | 150  |      | °C       |

| Thermal hysteresis (5)                    | T <sub>OTP_HYS</sub>    |                                                                                                                                                                                |      | 20   |      | °C       |

| VDD regulator                             | Vdd                     |                                                                                                                                                                                | 1.7  | 1.8  | 1.9  | V        |

| VDD load regulation                       | Vdd_reg                 | I <sub>DD</sub> = 5mA                                                                                                                                                          |      | 3    |      | %        |

| VCC UVLO rising threshold                 | Vcc_rs                  |                                                                                                                                                                                | 4    | 4.3  | 4.6  | V        |

| VCC UVLO threshold<br>hysteresis          | V <sub>CC_HYS</sub>     |                                                                                                                                                                                |      | 350  |      | mV       |

| VBUS_P_UV falling<br>threshold            | VBUS_P_UV               | I <sup>2</sup> C set VBUS_UV_THD = 0b                                                                                                                                          | 2.79 | 2.97 | 3.15 | V        |

| GPIO7                                     | -                       |                                                                                                                                                                                |      |      |      |          |

| DISCHG output high                        | Vdis_high               | Discharge turn-on, $50k\Omega$ load                                                                                                                                            |      | 4.4  |      | V        |

| DISCHG output low                         | Rdis_low                |                                                                                                                                                                                |      | 3.3  |      | kΩ       |

| ADJ sink current                          | I <sub>ADJ</sub>        | GPIO3_ISENS+ = 1.5V                                                                                                                                                            | 1    | 2    | 3    | μA       |

| EN_OUT_MID                                | Ven_out_mid             | 100k $\Omega$ , pull-up resistor to 12V                                                                                                                                        | 0.8  | 1    | 1.2  | V        |

| EN_OUT high                               | Ven_out_h               | Open drain, 100kΩ,<br>pull-up resistor to VCC                                                                                                                                  | 4.5  |      |      | V        |

| EN_OUT low                                | Ven_out_l               |                                                                                                                                                                                |      |      | 0.4  | V        |

| GPIO5, GPIO6                              |                         |                                                                                                                                                                                |      |      |      |          |

| VBUS_UV_FIXPDO falling threshold          | VBUS_UVFIX_<br>FALL     | VBUS = 5V                                                                                                                                                                      | 0.91 | 0.96 | 1.01 | V        |

| IPWM duty cycle                           | IPWMDUTY                | 4.7kΩ, pull-up resistor to VCC,<br>3A PDO                                                                                                                                      |      | 50   |      | %        |

| SYNC_OUT1 frequency                       | fsync1                  | 4.7k $\Omega$ , pull-up resistor to VCC                                                                                                                                        |      | 450  |      | kHz      |

| SYNC_OUT2 frequency                       | fsync2                  | 4.7k $\Omega$ , pull-up resistor to VCC                                                                                                                                        |      | 450  |      | kHz      |

| I <sup>2</sup> C_SLV_SDA/SCL<br>frequency | fi2C_SLV_SDA_<br>SCL    | 4.7k $\Omega$ , pull-up resistor to VCC                                                                                                                                        |      | 400  |      | kHz      |

| VSEL2 output low                          | V <sub>SEL_LOW</sub>    | 100kΩ to VCC                                                                                                                                                                   |      |      | 0.4  | V        |

| GPIO4, GPIO3                              |                         | ·                                                                                                                                                                              |      | •    |      | <u>.</u> |

| EN UVLO rising threshold                  | V <sub>EN_H</sub>       |                                                                                                                                                                                | 1.33 | 1.43 | 1.53 | V        |

| EN UVLO falling hysteresis voltage        | Ven_L                   |                                                                                                                                                                                |      | 220  |      | mV       |

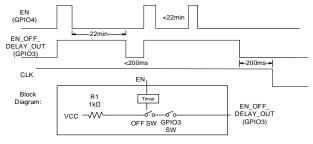

| EN_OFF_DELAY                              | ten_off_delay           | EN_OFF_TIMER = 010b                                                                                                                                                            |      | 22   |      | min      |

| VBATT low falling threshold               | VBATT_LOW_F             | Set GPIO4 = 11b                                                                                                                                                                | 1.07 | 1.12 | 1.17 | V        |

| VBATT low rising threshold                | V <sub>BATT_LOW_R</sub> | Set GPIO4 = 11b                                                                                                                                                                | 1.12 | 1.18 | 1.24 | V        |

### $V_{cc} = 5V$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$ , typical value is tested at $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                 | Symbol                   | Condition                                                     | Min | Тур  | Max  | Units |

|-------------------------------------------|--------------------------|---------------------------------------------------------------|-----|------|------|-------|

| ATTACH output high                        | VATTACH_HIGH             |                                                               | 4.5 |      |      | V     |

| ATTACH output low                         | VATTACH_LOW              | Sink is attached                                              |     |      | 0.4  | V     |

| IPWM duty cycle                           | IPWMDUTY                 | 4.7kΩ, pull-up resistor to VCC,<br>3A PDO                     |     | 50   |      | %     |

| Plug orientation (POL) output low         | V <sub>POL_L</sub>       | CC1 = 5.1kΩ                                                   |     |      | 0.4  | V     |

| POL output high                           | V <sub>POL_H</sub>       | CC2 = $5.1k\Omega$ , $10k\Omega$ ,<br>pull-up resistor to VCC | 4.5 |      |      | V     |

| GPIO2                                     |                          |                                                               |     |      |      |       |

| Power share input low                     | Vps_low                  | $10k\Omega$ pull-up resistor to VCC                           |     |      | 0.4  | V     |

| Power share input high                    | V <sub>PS_H</sub>        | 10kΩ pull-up resistor to VCC                                  | 3   |      |      | V     |

| POL output low                            | V <sub>POL_L</sub>       | CC1 = 5.1kΩ                                                   |     |      | 0.4  | V     |

| POL output high                           | V <sub>POL_H</sub>       | CC2 = $5.1k\Omega$ , $10k\Omega$ ,<br>pull-up resistor to VCC | 4.5 |      |      | V     |

| QC_12 pull low resistance                 | R <sub>QC_12</sub>       | DP/DM enter QC 12V                                            |     | 8    |      | Ω     |

| I2C_MODE                                  | 1                        |                                                               |     |      |      |       |

| Logic high threshold                      | V <sub>I2C_H</sub>       | Slave mode                                                    | 1   | 1.2  | 1.4  | V     |

| Hysteresis                                | VI2C_H_HYS               |                                                               |     | 100  |      | mV    |

| Resistance                                | RI2C_MODE                |                                                               |     | 1    |      | MΩ    |

| GPIO1                                     | 1                        |                                                               |     | 1    |      |       |

| VSEL1 pull low resistance                 | R <sub>VSEL1</sub>       | 12V PDO is selected                                           |     | 100  |      | kΩ    |

| VSEL1 output high                         | V <sub>SEL_HIGH</sub>    | 100kΩ to VCC                                                  | 4.5 |      |      | V     |

| INT logic high                            | VINT_HIGH                |                                                               | 4.5 |      |      | V     |

| INT logic low                             | VINT_LOW                 |                                                               |     |      | 0.4  | V     |

| Leakage                                   | Int_lkg                  |                                                               |     |      | 1    | μA    |

| PDO_SEL_OUTPUT (Config                    | ure SLAVE_D              | DEVICE_SEL = 101b)                                            |     | 1    |      |       |

| PDO2 to PDO3 SEL_OUT pull low resistance  | R <sub>PDO2_LOW</sub>    |                                                               |     | 7    |      | Ω     |

| PDO2-4 SEL OUT leakage                    | Vpdo_high                | 5V PDO is selected                                            |     |      | 1    | μA    |

| NTC, NTC2                                 | 1                        |                                                               |     |      |      |       |

| External thermal-sense trip threshold     | V <sub>NTC_R</sub>       | $R_{P} = 47k\Omega, R_{NTC} = 4.72k\Omega (100^{\circ}C)$     | 7.5 | 9.1  | 10.5 | %VCC  |

| External thermal-sense recovery threshold | VNTC_F                   | $R_{P} = 47k\Omega, R_{NTC} = 9.45k\Omega (80^{\circ}C)$      |     | 16.7 |      | %VCC  |

| Gate Drive (VDRV)                         |                          |                                                               |     | •    |      | •     |

| Gate drive voltage                        | Vdrv                     | Vdrv - Vbus_p                                                 |     | 4.85 |      | V     |

| Gate drive voltage at 15µA                | Vdrv_1                   | Isource = 15µA                                                |     | 4.4  |      | V     |

| Pull-down resistor                        | Rpull_down               |                                                               |     | 5    |      | kΩ    |

| BC1.2 DCP Mode                            | 1                        |                                                               |     |      |      |       |

| DP and DM short resistance                | R <sub>DP_DM_SHORT</sub> | $V_{DP}=0.8V,I_{DM}=1mA,T_{J}=25^{\circ}C$                    |     | 25   | 40   | Ω     |

MPQ5031 Rev. 1.0 12/15/2020 N

### $V_{cc} = 5V$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$ , typical value is tested at $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                                    | Symbol                     | Condition                               | Min  | Тур  | Max  | Units |

|--------------------------------------------------------------|----------------------------|-----------------------------------------|------|------|------|-------|

| Divider Mode                                                 |                            |                                         |      | 1    |      |       |

| DP output voltage                                            | VDIVIDER_DP                | V <sub>OUT</sub> = 5V                   | 2.55 | 2.75 | 2.95 | V     |

| DM output voltage                                            | VDIVIDER_DM                | V <sub>OUT</sub> = 5V                   | 3.35 | 3.6  | 3.85 | V     |

| DP output impedance                                          | R <sub>DIVIDER_DP</sub>    |                                         |      | 22   |      | kΩ    |

| DM output impedance                                          | R <sub>DIVIDER_DM</sub>    |                                         |      | 22   |      | kΩ    |

| 1.2V/1.2V Mode                                               |                            |                                         | •    |      |      |       |

| DP/DM output voltage                                         | Vdp_dm_1.2V                | V <sub>OUT</sub> = 5V                   | 1.05 | 1.20 | 1.35 | V     |

| DP/DM output impedance                                       | R <sub>DP_DM_1.2V</sub>    |                                         |      | 300  |      | kΩ    |

| Quick Charge 3.0 Mode                                        |                            |                                         | -    |      |      |       |

| DP/DM low voltage                                            | Vqc_low                    |                                         | 0.2  | 0.3  | 0.4  | V     |

| DP/DM high voltage                                           | Vqc_нідн                   |                                         | 1.8  | 2    | 2.2  | V     |

| DP output impendence                                         | Rdp_qc                     |                                         |      | 350  | 1500 | kΩ    |

| DM output impendence                                         | Rdm_qc                     |                                         |      | 20   |      | kΩ    |

| DM low glitch time <sup>(5)</sup>                            | t <sub>GLITCH_DM</sub>     |                                         |      | 10   |      | ms    |

| DP high glitch time                                          | tglitch_dp                 |                                         | 1000 |      | 1500 | ms    |

| Output voltage change glitch time <sup>(5)</sup>             | tglitch_v_<br>change       |                                         | 20   | 40   | 60   | ms    |

| Bus voltage step (5)                                         | V <sub>BUS_CONT_STEP</sub> |                                         | 150  | 200  | 250  | mV    |

| Time for VBUS to discharge to 5V when DP < $0.6V^{(5)}$      | t <sub>v_unplug</sub>      |                                         |      |      | 500  | ms    |

| FCP Mode                                                     |                            |                                         |      |      |      |       |

| DM Tx high voltage                                           | V <sub>FCPT_H</sub>        | $R_{LOAD} = 15k\Omega$                  | 2.55 |      | 5    | V     |

| DM Tx low voltage                                            | V <sub>FCPT_L</sub>        | R <sub>LOAD</sub> = 15kΩ                |      |      | 0.4  | V     |

| DM Rx high voltage                                           | V <sub>FCPR_H</sub>        |                                         | 1.5  |      | 5    | V     |

| DM Rx low voltage                                            | Vfcpr_l                    |                                         |      |      | 1    | V     |

| DM pull-low resistance (5)                                   | RLD_D-                     |                                         |      | 15   |      | kΩ    |

| Unit interval of PHY (5)                                     | UI                         | f <sub>CLK</sub> = 125kHz               | 144  | 160  | 176  | μs    |

| CDP Mode (I <sup>2</sup> C set CDP_EN                        | =1)                        |                                         | •    |      |      |       |

| DM CDP output voltage                                        | Vdm_src                    | V <sub>DP</sub> = 0.6V, DM_SINK = 250µA | 0.5  | 0.6  | 0.7  | V     |

| DP rising lower window threshold for V <sub>DM_SRC</sub>     | Vdat_ref                   |                                         | 0.25 | 0.35 | 0.45 | V     |

| DP rising lower window threshold hysteresis                  | V <sub>DAT_REF_HYS</sub>   |                                         |      | 50   |      | mV    |

| DP rising upper window threshold for V <sub>DM_SRC</sub>     | Vlgc_src                   |                                         | 0.8  | 0.95 | 1.1  | V     |

| DP rising upper window threshold hysteresis                  | VLGC_SRC_HYS               |                                         |      | 80   |      | mV    |

| USB Type-C – CC1 and CC2                                     | pins                       | •                                       | •    |      |      |       |

| CC pull-up current 1                                         | I <sub>RP1</sub>           | VBUS = 5V/3A, T <sub>J</sub> = 25°C     | 304  | 330  | 356  | μA    |

| CC pull-up current 2                                         | I <sub>RP2</sub>           | VBUS = 5V/1.5A, TJ = 25°C               | 162  | 180  | 198  | μΑ    |

| CC voltage to enable V <sub>CONN</sub><br>for 3A Type-C mode | V <sub>RA1</sub>           | T <sub>J</sub> = 25°C                   |      |      | 0.75 | V     |

### $V_{cc} = 5V$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$ , typical value is tested at $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                          | Symbol                   | Condition                      | Min  | Тур  | Max  | Units |

|----------------------------------------------------|--------------------------|--------------------------------|------|------|------|-------|

| CC voltage to enable $V_{BUS}$ for 3A Type-C mode  | V <sub>RD1</sub>         | T <sub>J</sub> = 25°C          | 0.85 |      | 2.45 | V     |

| CC detach threshold for 3A<br>Type-C mode          | Vopen1                   | T <sub>J</sub> = 25°C          | 2.75 |      |      | V     |

| CC voltage falling debounce timer                  | t <sub>CC_DEBOUNCE</sub> | VBUS enable deglitch           | 100  | 150  | 200  | ms    |

| CC voltage rising debounce timer                   | tpd_debounce             | VBUS disable deglitch          | 5    | 10   | 15   | ms    |

| VCONN output power                                 | Pv_conn                  | VCC supplies V <sub>CONN</sub> | 0.1  |      |      | W     |

| USB PD                                             |                          |                                |      |      |      |       |

| Unit interval                                      | tui                      | $T_J = 25^{\circ}C$            | 3.0  | 3.35 | 3.7  | μs    |

| Transmitter                                        |                          | ·                              |      |      |      |       |

| End drive BMC <sup>(5)</sup>                       | <b>t</b> EDBMC           |                                |      |      | 23   | μs    |

| Fall time <sup>(5)</sup>                           | tFALL                    |                                | 300  |      |      | ns    |

| Rise time <sup>(5)</sup>                           | t <sub>RISE</sub>        |                                | 300  |      |      | ns    |

| Hold low BMC <sup>(5)</sup>                        | tньвмс                   |                                | 1    |      |      | μs    |

| Logic high voltage                                 | Vlh                      |                                | 1    | 1.15 | 1.3  | V     |

| Logic low voltage                                  | VLL                      |                                |      |      | 100  | mV    |

| Output impedance                                   | RTX                      |                                |      | 50   |      | Ω     |

| Receiver <sup>(5)</sup>                            | ·                        |                                |      |      |      |       |

| CC receiver capacitance                            | CRECEIVER                |                                |      |      | 600  | pF    |

| Transitions for signal detection                   | NTRANSITION              |                                | 3    |      |      | edges |

| Rx bandwidth limiting filter                       | t <sub>RX_FILTER</sub>   |                                | 100  |      |      | ns    |

| Time Window for Detecting Non-idle                 | transition_<br>WINDOW    |                                | 12   |      | 20   | μs    |

| Receiver input impedance                           | RBMC_RX                  |                                | 1    |      |      | MΩ    |

| I <sup>2</sup> C Interface Specifications          | (5)                      | •                              |      | I.   | I.   |       |

| Input logic high                                   | VIL                      |                                | 1.4  |      |      | V     |

| Input logic low                                    | VIH                      |                                |      |      | 0.6  | V     |

| Output voltage logic low                           | Vout_l                   |                                |      |      | 0.4  | V     |

| SCL clock frequency                                | fsc∟                     |                                |      | 400  |      | kHz   |

| SCL high time                                      | tніgн                    |                                | 60   |      |      | ns    |

| SCL low time                                       | t <sub>LOW</sub>         |                                | 160  |      |      | ns    |

| Data set-up time                                   | t <sub>SU_DAT</sub>      |                                | 10   |      |      | ns    |

| Data hold time                                     | thd_dat                  |                                |      | 70   |      | ns    |

| Set-up time for repeated start                     | tsu_sta                  |                                | 160  |      |      | ns    |

| Hold time for a repeated start condition           | thd_sta                  |                                | 160  |      |      | ns    |

| Bus free time between a start and a stop condition | tвuғ                     |                                | 160  |      |      | ns    |

### $V_{cc} = 5V$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$ , typical value is tested at $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                         | Symbol         | Condition | Min | Тур | Max | Units |

|-----------------------------------|----------------|-----------|-----|-----|-----|-------|

| Set-up time for a stop condition  | tsu.sto        |           | 160 |     |     | ns    |

| SCL and SDA rise time             | t <sub>R</sub> |           | 10  |     | 300 | ns    |

| SCL and SDA fall time             | t⊧             |           | 10  |     | 300 | ns    |

| Pulse width of suppressed spike   | tsp            |           | 0   |     | 50  | ns    |

| Capacitance bus for each bus line | C <sub>B</sub> |           |     |     | 400 | pF    |

Note:

5) Guaranteed by characterization.

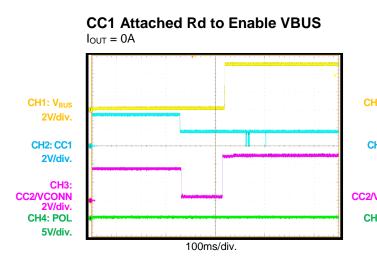

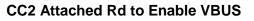

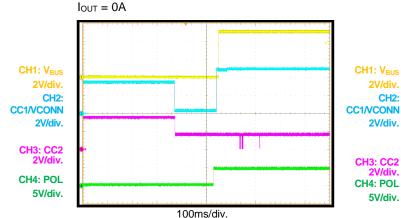

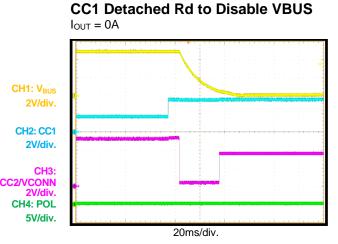

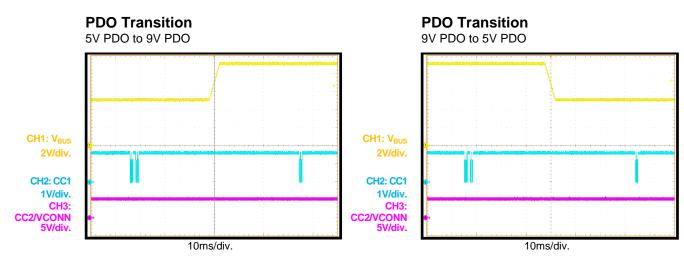

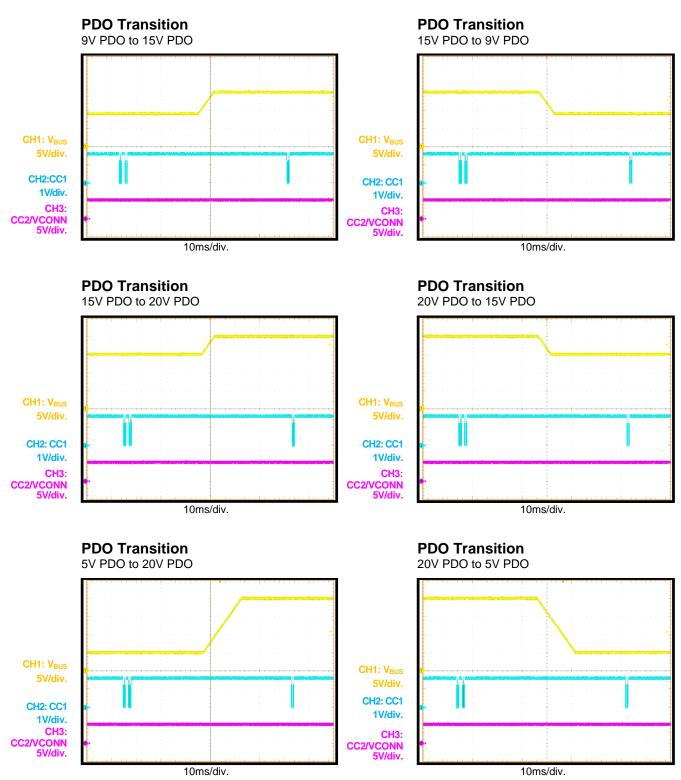

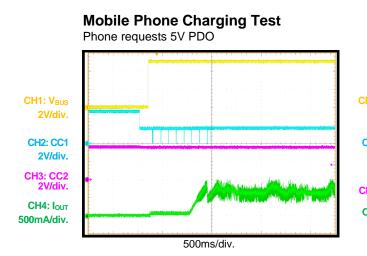

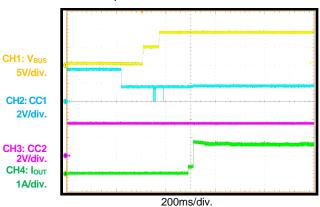

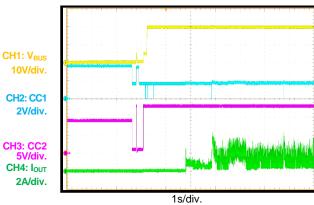

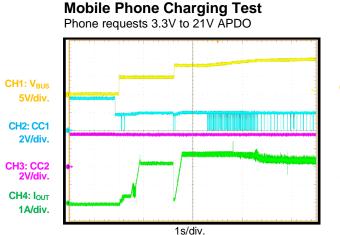

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{CC}$  = 5V,  $V_{BUS}$  = 5V to 20V,  $T_A$  = 25°C, unless otherwise noted. Connect the MPQ5031's VBUS\_P pin to the MPQ4230's output.

## CC2 Detached Rd to Disable VBUS

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

MPQ5031 Rev. 1.0 MonolithicPower.com 12/15/2020 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2020 MPS. All Rights Reserved.

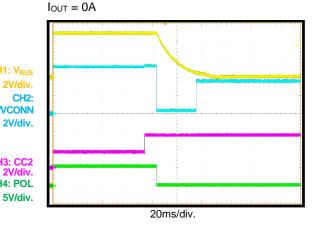

$V_{CC}$  = 5V,  $V_{BUS}$  = 5V to 20V,  $T_A$  = 25°C, unless otherwise noted. Connect the MPQ5031's VBUS\_P pin to the MPQ4230's output.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{CC}$  = 5V,  $V_{BUS}$  = 5V to 20V,  $T_A$  = 25°C, unless otherwise noted. Connect the MPQ5031's VBUS\_P pin to the MPQ4230's output.

Mobile Phone Charging Test Phone requests 9V PDO

Laptop Charging Test Laptop requests 20V PDO

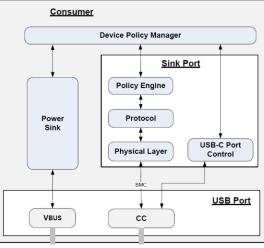

## FUNCTIONAL BLOCK DIAGRAM

Figure 2: Functional Block Diagram

## **OPERATION**

### Under-Voltage Lockout (UVLO)

Under-voltage lockout (UVLO) protects the chip from operating at an insufficient supply voltage. The MPQ5031's UVLO comparator monitors the VCC input voltage.

### VCC and VDD Regulator

The VCC pin is biased by an external 5V supply (e.g. the DC/DC converter's VCC pin). The VCC pin must have a decoupling capacitor between  $1\mu$ F and  $10\mu$ F.

The 1.8V internal VDD regulator uses VCC as the input. The VDD pin powers most of the digital circuitries, and requires a  $0.47\mu$ F decoupling capacitor.

### Charging Mode Auto-Detection

### Legacy USB 2.0 Mode

The MPQ5031 integrates a USB dedicated charging port auto-detection function that can recognize most mainstream portable devices. It supports the following charging schemes:

- USB Battery Charging Specification BC1.2/ Chinese Telecommunications Industry Standard YD/T 1591-2009

- Apple 3A divider mode

- 1.2V/1.2V mode

- QC3.0 Class A (3.3V to 12V)

- Huawei FCP Class A

The auto-detection function is a state machine that supports all of the above DCP charging schemes, starting in divider mode. If a device compliant with divider mode is attached, the MPQ5031 remains in divider mode. Then 3.6V is applied to the DM pin, and 2.7V is applied to the DP pin.

If a device compliant with BC1.2 or YD/T 1591-2009 is attached, the MPQ5031 operates in 1.2V/1.2V and BC1.2 DCP mode. DM and DP are shorted together with a resistance below  $40\Omega$ . The MPQ5031 remains in that mode until the device releases the data line. Then the device returns to divider mode.

When a QC3.0 or FCP device (without PD protocol) is attached, the MPQ5031 automatically enters high-voltage quick charge mode.

The MPQ5031 supports BC1.2 charging data

port (CDP) handshaking as well, which can be enabled by the I<sup>2</sup>C. DCP mode should be disabled (LEGACY\_CHARGING\_MODE\_SEL = 11b) when the CDP function is selected.

If a USB PD contract is established once the sink is attached, QC3.0 functionality is disabled, but BC1.2 short mode is still enabled.

### USB Type-C Port

The USB Type-C receptacle, plug, and cable solution incorporates a configuration process to detect a downstream-facing port (DFP) to upstream-facing port (UFP) connection for  $V_{BUS}$  management, and to determine the host-to-device relationship.

Initially, DFP-to-UFP attachment is detected by a host (DFP) when one of the CC pins at its USB Type-C receptacle senses a specified resistance to GND. Subsequently, UFP-to-DFP detachment is detected when the CC pin that was terminated at its USB Type-C receptacle is no longer connected to GND.

Power is not applied to the USB Type-C host or hub receptacle ( $V_{BUS}$  or  $V_{CONN}$ ) until the DFP detects the presence of an attached device (UFP) port. When a DFP-to-UFP attachment is detected, the DFP enables power to the receptacle and begins normal USB operation with the attached device. When a DFP-to-UFP detachment is detected, the port sourcing  $V_{BUS}$ removes power.

The MPQ5031 is a DFP (provider only), and its power supply capability is rated at 5V/3.0A by default.  $V_{CONN}$  is provided by the DFP to power the cables and electronics in the plug.  $V_{CONN}$  is provided instead of the CC pin if the CC pin is not connected to the cable's configuration channel (CC) wire.  $V_{CONN}$  has a maximum power output of 100mW.

$V_{\text{CONN}}$  is disabled until  $R_A$  is detected.  $R_A$  is a pulldown resistor connected from the CC pin to GND, and its resistance should be below  $1.2k\Omega$ .

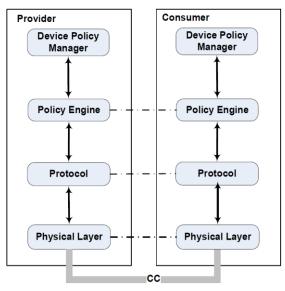

### **USB Power Delivery**

In USB power delivery (PD), pairs of directly attached ports negotiate voltage, current, and/or direction of power flow over the USB cable by

using the CC wire as the communication channel. The mechanisms that are implemented operate independently of other USB methods that are used to negotiate power.

Type-C connectors can support the CC wire as the communication channel. The USB PD engine is disabled until a valid Type-C connection is established. Figure 3 shows a USB PD communication stack.

Figure 3: USB PD Communication Stack

### **DFP Commands**

Table 1, Table 2, and Table 3 list the MPQ5031's supported commands. Table 1 lists the control messages.

Table 1: Control Message

| Table 1. Control Message |                  |  |  |  |  |

|--------------------------|------------------|--|--|--|--|

| Transmitted Message      | Received Message |  |  |  |  |

| Accept                   | Get_PPS_Status   |  |  |  |  |

| Get_Sink_Cap             | Get_Source_Cap   |  |  |  |  |

| Get_Sink_Cap_            | Get_Source_Cap_  |  |  |  |  |

| Extended                 | Extended         |  |  |  |  |

| Get_Status               | Get_Status       |  |  |  |  |

| GoodCRC                  | GoodCRC          |  |  |  |  |

| GotoMin                  | Not_Supported    |  |  |  |  |

| Not_Supported            | Reject           |  |  |  |  |

| PS_RDY                   | Soft_Reset       |  |  |  |  |

| Reject                   | VCONN_Swap       |  |  |  |  |

| Soft_Reset               |                  |  |  |  |  |

Table 2 lists the different data messages.

#### **Table 2: Data Messages**

| Transmitted<br>Message | Received Message  |

|------------------------|-------------------|

| Source_Capabilities    | Sink_Capabilities |

| BIST                   | Request           |

| Alert                  | BIST              |

|                        | Alert             |

Table 3 lists the extended messages.

**Table 3: Extended Messages**

| Transmitted Message  | Received Message |

|----------------------|------------------|

| Status               |                  |

| PPS_Status           |                  |

| Source_Capabilities_ |                  |

| Extended             |                  |

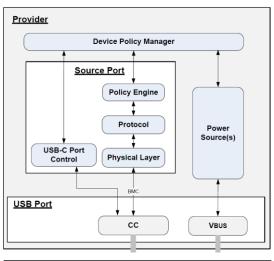

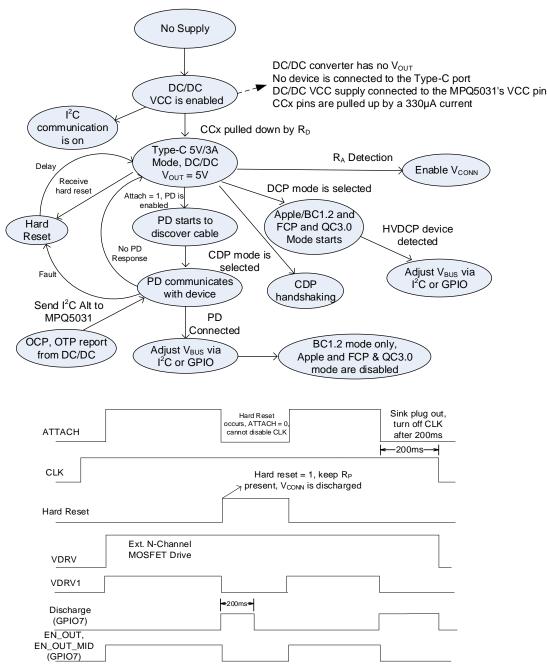

The MPQ5031 also supports soft reset, hard reset, and cable discovery for VDM signals. Figure 4 shows the device policy manager.

Figure 4: Device Policy Manager

### PD Contract Handshake

Figure 5 shows the MPQ5031's PD contract handshake sequence.

| #  | CH  | OS   | Power  | Data | Cable Plug | Туре                |

|----|-----|------|--------|------|------------|---------------------|

| 0  | CC2 | SOP' |        |      | UFP or DFP | Vendor_Defined      |

| 1  | CC2 | SOP' |        |      | Cable Plug | GoodCRC             |

| 2  | CC2 | SOP' |        |      | Cable Plug | Vendor_Defined      |

| 3  | CC2 | SOP' |        |      | UFP or DFP | GoodCRC             |

| 4  | CC2 | SOP  | Source | DFP  |            | Source_Capabilities |

| 5  | CC2 | SOP  | Sink   | UFP  |            | GoodCRC             |

| 6  | CC2 | SOP  | Sink   | UFP  |            | Request             |

| 7  | CC2 | SOP  | Source | DFP  |            | GoodCRC             |

| 8  | CC2 | SOP  | Source | DFP  |            | Accept              |

| 9  | CC2 | SOP  | Sink   | UFP  |            | GoodCRC             |

| 10 | CC2 | SOP  | Source | DFP  |            | PS_RDY              |

| 11 | CC2 | SOP  | Sink   | UFP  |            | GoodCRC             |

Figure 5: PD Contract Handshake

### VBUS and VCONN Discharge

When the sink is detached or a hard reset occurs, the MPQ5031 sends a command to turn off the DC/DC regulator's output voltage, and VBUS P's 200 $\Omega$  discharge resistor turns on for 200ms. The GPIO7 pin can also be used to control an external MOSFET to discharge the output voltage for 200ms. Meanwhile, the VCONN voltage is discharged with a  $1k\Omega$ resistor for 30ms.

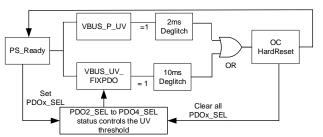

### **VBUS Under-Voltage (UV) Detection**

When a DC/DC converter with an I<sup>2</sup>C interface is under-voltage selected. the VBUS (UV) detection function is enabled by monitoring PG STATUS. If the VBUS P voltage is <2.97V (or <4.5V) during PPS operation, the VBUS UV bit is set to 1 internally, and a hard reset is triggered.

When a DC/DC converter without an I<sup>2</sup>C interface is selected, PPS functionality is disabled. In fixed PDO operation, GPIO5 can be configured to VBUS UV FIXPDO. For this function, connect GPIO5 to VBUS with a 1/5 resistor divider to detect the VBUS voltage. Table 4 lists how to set the VBUS UV threshold in a fixed PDO state. When the VBUS voltage is below the threshold, VBUS\_UV\_FIXPDO is set to 1 internally, and a hard reset is triggered.

Table 4: VBUS UV Threshold (Only Valid for DC/DC Converters without I<sup>2</sup>C )

| Sink<br>Requested     | VBUS_UV_<br>FIXPDO<br>Threshold (V) | VBUS UV<br>threshold<br>(V) |

|-----------------------|-------------------------------------|-----------------------------|

| Default,<br>Vout = 5V | 0.96                                | 4.8                         |

| Vout = 9V             | 1.743                               | 8.715                       |

| Vout = 15V            | 2.938                               | 14.69                       |

| Vout = 20V            | 3.88                                | 19.4                        |

Figure 6 shows a VBUS UV example.

### Figure 6: VBUS UV Detection for Non-I<sup>2</sup>C DC/DC ApplicationsStart-Up and Shutdown Timing

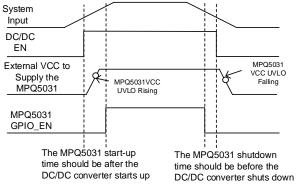

The GPIO3, GPIO4, and GPIO6 pins can be configured to be the EN input function that controls when the MPQ5031 is on or off.

If the MPQ5031's VCC exceeds 4.3V and the GPIOx EN pin is pulled high, the PD engine can be enabled. The MPQ5031's start-up time should begin after the DC/DC converter start-up time, and its shutdown time should be before the converter's shutdown time (see Figure 7).

#### Figure 7: MPQ5031 Start-Up and Shutdown Timing

When the MPQ421x, MPQ423x, MPQ426x or MPQ4272 is used as the DC/DC converter, the converter's 5V LDO output can power the MPQ5031's VCC. If the MP28167-A is selected as the DC/DC converter, an external 5V LDO should be added to power the MPQ5031. The

external 5V LDO's start-up timing should be later than the MP281671-A's timing.

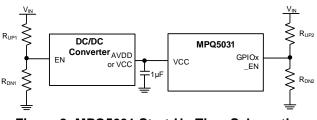

In the MPQ421x, MPQ4272, or MP28167-A PD solution, the MPQ5031's GPIOx\_EN pin should be added to control the PD engine's startup/shutdown time.

If connecting the MPQ5031 GPIOx EN pin to VIN, the input voltage  $(V_{IN})$  of the PD's start-up and shutdown sequence can be calculated with Equation (1) and Equation (2), respectively:

$V_{IN_{ON}}(V) = 1.43V \times (R_{DN2} + R_{UP2}) / R_{DN2}$ (1)

$V_{IN OFF}(V) = 1.21V \times (R_{DN2} + R_{UP2}) / R_{DN2}$  (2)

Figure 8 shows the MPQ5031's start-up time schematic.

Figure 8: MPQ5031 Start-Up Time Schematic

Table 5 lists the V<sub>IN</sub> start-up and shutdown thresholds.

|                      | DC/DC EN<br>Divider (kΩ) | MPQ5031 EN<br>Divider (kΩ) | DC/DC Start-Up/<br>Shutdown (V) | MPQ5031 Start-Up/<br>Shutdown (V) |

|----------------------|--------------------------|----------------------------|---------------------------------|-----------------------------------|

| MPQ5031 +<br>MPQ4214 | 100/30                   | 100/28.4                   | 5.85/5.07                       | 6.47/5.47                         |

| MPQ5031 +<br>MPQ4272 | 100/39                   | 100/28.4                   | 5.7/4.9                         | 6.47/5.47                         |

### Table 5: VIN Start-Up/Shutdown Threshold

### **EN Off Delay Timer**

GPIO3 pin can be configured for The EN OFF DELAY OUT functionality. When EN is high, the IC is enabled immediately. When the external signal ΕN off is received. EN OFF DELAY OUT (GPIO3) remains high for 22min (EN\_OFF\_TIMER = 010b) to enable the upstream DC/DC converter. Once the 22min delay time completes, the USB PD engine is disabled immediately and CLK is disabled after a 200ms delay (see Figure 9). Figure 10 on page 20 shows the timing sequence.

#### Figure 9: EN Off Timer

If EN OFF DELAY functionality is not required, configure the GPIO3 for a function that is not EN OFF DELAY OUT.

### **State Machine and Timing Sequence**

### **V**<sub>CONN</sub> Over-Current Protection (OCP)

The VCC to V<sub>CONN</sub> switch has a  $20\Omega$  resistance and a 50mA over-current protection (OCP) threshold. When V<sub>CONN</sub> OCP is triggered, the V<sub>CONN</sub> output latches off. The following actions can re-enable V<sub>CONN</sub> :

- Cycling power on VIN and EN

- A hard reset

- Detaching and reattaching the USB Type-C device

### **Bidirectional I<sup>2</sup>C Interface**

The MPQ5031's SDA and SCL pins support both I<sup>2</sup>C master and I<sup>2</sup>C slave functions. When cooperating with an external buck-boost converter (e.g. the MPQ4230), the MPQ5031 should operate in I<sup>2</sup>C master mode. When a user

wants to configure the MPQ5031's I<sup>2</sup>C register, I<sup>2</sup>C slave mode should be selected.

Float I2C\_MODE or pull it to GND to set the MPQ5031 to I<sup>2</sup>C master mode. Pull I2C\_MODE to VCC to set the MPQ5031 to I<sup>2</sup>C slave mode. In I<sup>2</sup>C slave mode (I2C\_MODE = VCC), the digital CLK is always on. The I<sup>2</sup>C register and I<sup>2</sup>C functionality are active once VCC is ready. The user does not need to wait for a Type-C sink to be attached.

The GPIO5 and GPIO6 pins can be configured as a second  $I^2C$  slave entrance, but an internal clock must be turned on to access full  $I^2C$ functionality. SDA, SCL, GPIO5, and GPIO6 cannot simultaneously work in  $I^2C$  slave mode (see Table 6).

| I2C_MODE<br>Input | Pin 1, Pin 2<br>(SDA, SCL)<br>Function | GPIO5, GPIO6 I <sup>2</sup> C<br>Function                                                                  | Internal Clock                                                                                      |  |  |  |  |  |

|-------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| VCC               | In I <sup>2</sup> C slave<br>mode      | I <sup>2</sup> C functionality is disabled                                                                 | Always on                                                                                           |  |  |  |  |  |

| GND               | In I <sup>2</sup> C master<br>mode     | In I <sup>2</sup> C slave mode.<br>Must turn on internal clock<br>to access full I <sup>2</sup> C function | Either USB Type-C attachment or<br>writing 0x55AA to register 0x14<br>can enable the internal clock |  |  |  |  |  |

#### Table 6: I<sup>2</sup>C Function on Pin 1, Pin 2 and GPIO5, GPIO6

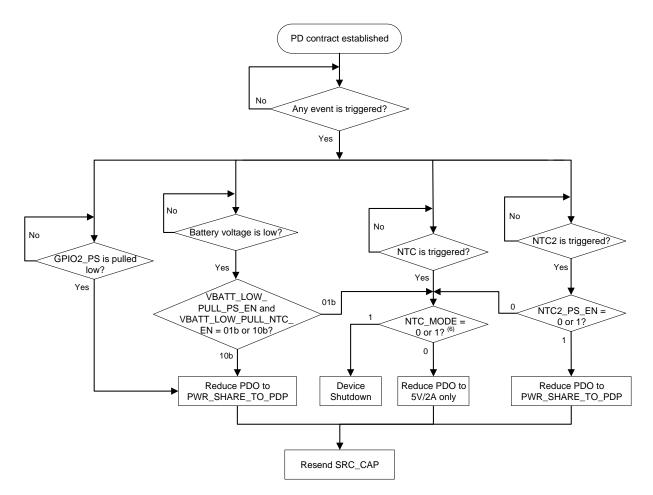

### **Battery Low Detection**

The GPIO4 and GPIO2 pins can be configured as an input battery voltage sense pin. If the battery voltage drops below a certain level (this level is configurable), then the USB PD engine updates the source capability based on the I<sup>2</sup>C control bits VBATT\_LOW\_PULL\_PS\_EN and VBATT\_LOW\_PULL\_NTC\_EN (see Table 7). When the battery voltage recovers, the USB PD engine changes the source capabilities to normal. If VBATT\_LOW\_PULL\_NTC\_EN = 1, the source capability returns to normal after a 16-second delay.

This function can also be disabled via I<sup>2</sup>C control bits VBATT\_LOW\_PULL\_PS\_EN and VBATT\_LOW\_PULL\_NTC\_EN.

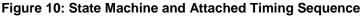

The recommended resistor divider ratio on VBATT\_SENSE pin is 1/10. The internal comparator falling threshold is 1.12V, and the rising threshold is 1.18V with a  $20\mu$ s deglitch time.

| VBATT_LOW_<br>PULL_PS_EN  | 0                                                        | 0                                                   | 1                                                             |

|---------------------------|----------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|

| VBATT_LOW_<br>PULL_NTC_EN | 0                                                        | 1                                                   | 0                                                             |

| Battery<br>Voltage Low    | PDO list is based on<br>the PDO_TYPE<br>register setting | Update PDO1 to<br>5V/2A, other PDOs<br>are disabled | Disable the PDO with a power<br>rating ≥ PWR_SHARE_TO_<br>PDP |

Table 7: Battery Low Update Source Capability

The battery voltage can be calculated with Equation (3):

$V_{BATT_LOW}(V) = 1.12V x (R_{DN} + R_{UP}) / R_{DN}$  (3)

Figure 11 shows the resistor divider.

Figure 11: VBATT\_SENSE Divider Resistor

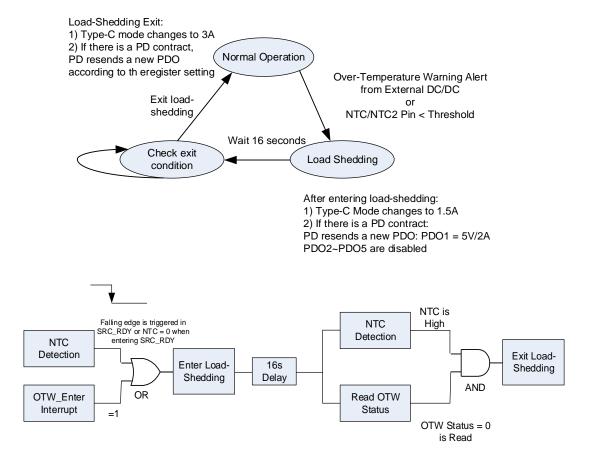

### Load-Shedding Entry and Recovery

When the NTC or NTC2 (NTC2\_PS\_EN = 0) falling threshold is triggered (NTC\_MODE = 0), the Type-C resistor ( $R_P$ ) pull-up current changes

from  $330\mu A$  to  $180\mu A$ , regardless of whether there is a PD contract.

When MPQ423x or MPQ426x device is selected (SLAVE\_DEVICE\_SEL = 001b), and it sends an OT\_WARNING signal and a PD contract exists, the Type-C pull-up current ( $R_P$ ) changes from 330µA to 180µA. The Type-C detection threshold then changes accordingly. If a PD contract exists, the USB PD PDO is updated to 5V/2A, and all other PDOs are disabled.

If the NTC or NTC2 voltage recovers to a normal value, and the external DC/DC converter OT\_WARNING = 0 (after a 16-second delay),  $R_P$  changes back to 330µA. If there was originally a PD contract, the MPQ5031 USB PD engine sends the default PDOs again. When NTC2\_PS\_EN = 1 and the NTC2 falling threshold is triggered, the MPQ5031 updates the PDO list based on the PWR\_SHARE\_TO\_PDP setting.

### **Thermal Shutdown**

Thermal shutdown prevents the chip from operating at exceedingly high temperatures. When the silicon die temperature exceeds  $150^{\circ}$ C or the NTC/NTC2 falling threshold is triggered (NTC\_MODE = 1), the MPQ5031 resets the USB PD engine and stops the DC/DC converter from switching via I<sup>2</sup>C communication, or by pulling the converter's EN pin low. When the temperature falls below its lower threshold (about 130°C), the chip is enabled for CCx detection. If the sink is attached, the MPQ5031 starts to enable the USB PD engine again.

The I<sup>2</sup>C slave is still operational during thermal shutdown.

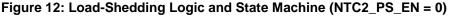

### **Power Sharing Function**

The GPIO2 pin can be configured for power share input functions. When GPIO2 (POWER\_SHARE) is pulled low, the USB PD engine disables the PDO if the power rating meets or exceeds PWR\_SHARE\_TO\_PDP, and all PPS APDOs are disabled.

The GPIO3, GPIO5, or GPIO7 pins can be configured for ATTACH indication. If using multiple devices, and the first MPQ5031 (MPQ5031 #1) detects that a sink is attached, it pulls GPIO3 low. Then the second MPQ5031's (MPQ5031 #2) GPIO2 is pulled low at the same time. MPQ5031 #2 disables the PDO with a power rating that is ≥PWR\_SHARE\_TO\_PDP, and all PPS APDOs are disabled.

The GPIO2 pin can also be used for power share output functions. When the MPQ5031's sinkrequested PDO power rating is ≥PWR\_SHARE\_OUTPUT\_THLD, GPIO2 is pulled low.

Figure 13: Power-Share Connection between Two MPQ5031s (Cut Total Power to 50%/50%)

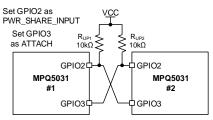

### I<sup>2</sup>C Arbitration

The GPIO3 pin can be configured for  $I^2C$  arbitration (I2C\_ARB) functions. When

MPQ5031 #1 sends an I<sup>2</sup>C command, it pulls down GPIO3 first. GPIO3 is pulled high again after MPQ5031 #1's I<sup>2</sup>C command is finished. MPQ5031 #2 always checks the GPIO3 status, and starts to send an I<sup>2</sup>C command until GPIO3 is released to high (see Figure 14). It is can be used in MPQ4272 reference design.

Figure 14: I<sup>2</sup>C Arbitration Connection

### **CDP Mode**

MPQ5031 The integrates CDP mode handshaking. Set CDP\_EN = 1 to enable CDP mode handshaking, and disable Apple divider mode, FCP, 1.2V/1.2V mode and other DCP DP schemes on and DM (LEGACY CHARGING MODE SEL = 11b) (see Figure 15).

Figure 15: CDP Mode Set-Up

### **Smart Line Drop Compensation**

The MPQ5031 has smart line drop compensation when the MPQ423x, MPQ426x or MPQ421x DC/DC converter is attached. Line drop compensation is active in fixed PDO or non-PD conditions. After entering a PPS condition, line drop compensation is disabled. If the other DC/DC converter is selected, the line drop compensation value is determined by the converter's set-up. The MPQ5031 does not disable line drop compensation in a PPS state.

When an MPQ423x or MPQ426x device is selected (SLAVE\_DEVICE\_SEL = 001b), the line drop compensation value is determined by the MPQ423x or MPQ426x's set-up. The MPQ5031 disables MPQ423x or MPQ426x line drop compensation after entering PPS.

When an MPQ421x device is selected (SLAVE\_DEVICE\_SEL = 000b), the MPQ5031 GPIO3 can be configured for ISENS+ functions to sense the MPQ421x's COMP pin voltage.

GPIO7 can be configured for ADJ functions to sink the  $2\mu$ A current on the MPQ421x's FB pin when the COMP voltage exceeds a certain voltage.

Figure 16: PDO Reduce Logic and State Machine

#### Note:

6) When NTC and PWR\_SHARE\_TO\_PDP events (GPIO2\_PS pulls low, battery voltage low or NTC2) are triggered at the same time, the PDO lists are updated based on the NTC set-up. If NTC\_MODE = 1, the device shuts down; if NTC\_MODE = 0, the PDO list is updated to 5V/2A.

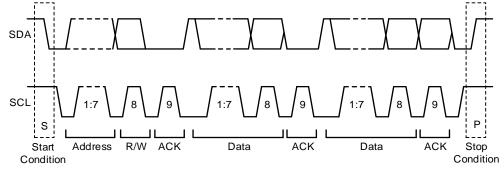

### I<sup>2</sup>C Transfer Data

Every byte put on the SDA line must be 8 bits long. Each byte must be followed by an acknowledge (ACK) bit. The master generates the acknowledge-related clock pulse. The transmitter releases the SDA line (high) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable (low) during the high period of this clock pulse. Figure 17 shows the data transfer format. After the start condition (S), a slave address is sent. This address is 7 bits long followed by an 8th data direction bit (R/W). A 0 indicates a transmission (write), while a 1 indicates a request for data (read). A data transfer is always terminated by a stop condition (P) generated by the master. For a master to continue communicating on a bus, it can generate a repeated start condition (Sr) and address another slave without first generating a stop condition.

Figure 17: Complete Data Transfer

The MPQ5031 includes a full  $I^2C$  slave controller. The  $I^2C$  slave fully complies with the  $I^2C$  specification requirements. It requires a start condition, valid  $I^2C$  address, register address byte, and data byte for a single data update. After receiving each byte, the MPQ5031 acknowledges the byte by pulling the SDA line low during the high period of a single clock pulse. A valid I<sup>2</sup>C address then selects the MPQ5031, and the MPQ5031 performs an update on the falling edge of the LSB byte.

Figure 18 shows an example of an  $I^2C$  read and write command.

### a) I<sup>2</sup>C Write Word

| 1  | 7                          | 1 1  | 8                    | 1   | 8             | 1      | 8 1          | 1   |                |     |

|----|----------------------------|------|----------------------|-----|---------------|--------|--------------|-----|----------------|-----|

| S  | Slave Address              | Wr A | I2C Register Address | А   | Data Byte Low | A Data | Byte High A  | Ρ   |                |     |

| b) | I <sup>2</sup> C Read Word | I    |                      |     |               |        |              |     |                |     |

| 1  | 7                          | 1 1  | 8                    | 1 1 | 7             | 1 1    | 8            | 1   | 8              | 1 1 |

| S  | Slave Address              | Wr A | I2C Register Address | A S | Slave Address | s Rd A | Data Byte Lo | w A | Data Byte High | AP  |

Figure 18: I<sup>2</sup>C Read and Write

## I<sup>2</sup>C REGISTER MAP

### I<sup>2</sup>C Slave, I2C\_MODE = VCC

| Add<br>(Hex) | Name         | R/W | D15                                                 | D14                                                       | D13                                 | D12                                       | D11                                                       | D1<br>0           | D9                | D8                                | D7                                               | D6                 | D5                 | D4                            | D3                                        | D2                   | D1                                          | D0                         |

|--------------|--------------|-----|-----------------------------------------------------|-----------------------------------------------------------|-------------------------------------|-------------------------------------------|-----------------------------------------------------------|-------------------|-------------------|-----------------------------------|--------------------------------------------------|--------------------|--------------------|-------------------------------|-------------------------------------------|----------------------|---------------------------------------------|----------------------------|

| 00           | PDO_<br>TYPE | R/W |                                                     | OTP_SOFTWARE_REVISION_NO (7)                              |                                     |                                           |                                                           |                   |                   | ERVED                             | PDO<br>5_EN<br>(7)                               | PDO<br>4_EN<br>(7) | PDO<br>3_EN<br>(7) | PDO<br>2_EN<br>(7)            | PDO5_<br>TYPE                             | PDO4_<br>TYPE<br>(7) | PDO3_<br>TYPE<br>(7)                        | PDO2<br>_TYPE              |

| 01           | PDO_<br>V1   | R   |                                                     |                                                           | RESER                               | VED                                       |                                                           |                   |                   |                                   | F                                                | DO1_\              | /OLTAG             | GE_SE                         | TTING (5                                  | ōV)                  |                                             |                            |

| 02           | PDO_I1       | R/W |                                                     | OTP                                                       | _SUFFI>                             | CODE                                      | (7)                                                       |                   |                   |                                   | PDO1                                             | _CURF              | RENT_S             | SETTIN                        | G (7) (3A                                 | default)             |                                             |                            |

| 03           | PDO_<br>V2   | R/W |                                                     |                                                           |                                     |                                           | PD                                                        | 02_V              | OLTAG             | E_SETTI                           | NG <sup>(7)</sup> (9                             | 9V defa            | ult)               |                               |                                           |                      |                                             |                            |

| 04           | PDO_l2       | R/W |                                                     |                                                           | RESER                               | VED                                       |                                                           |                   |                   |                                   | PDO2                                             | _CURF              | RENT_S             | SETTIN                        | G <sup>(7)</sup> (3A                      | default)             |                                             |                            |

| 05           | PDO_<br>V3   | R/W |                                                     |                                                           |                                     |                                           | PD                                                        | O3_V(             | OLTAG             | E_SETTIN                          | IG <sup>(7)</sup> (1                             | 5V defa            | ault)              |                               |                                           |                      |                                             |                            |

| 06           | PDO_I3       | R/W |                                                     |                                                           | RESER                               | VED                                       |                                                           |                   |                   |                                   | PDO3                                             | _CURF              | RENT_S             | SETTIN                        | G (7) (3A                                 | default)             |                                             |                            |

| 07           | PDO_<br>V4   | R/W |                                                     |                                                           |                                     |                                           | PD                                                        | 04_V              | OLTAG             | E_SETTIN                          | IG <sup>(7)</sup> (2                             | 0V defa            | ault)              |                               |                                           |                      |                                             |                            |

| 08           | PDO_I4       | R/W |                                                     |                                                           | RESER                               | VED                                       |                                                           |                   |                   |                                   | PDO4                                             | _CURF              | RENT_S             | SETTIN                        | G <sup>(7)</sup> (3A                      | default)             |                                             |                            |