# LM3488,LM3488Q

LM3488/LM3488Q High Efficiency Low-Side N-Channel Controller for Switching Regulators

Literature Number: SNVS089L

# LM3488/LM3488Q

# High Efficiency Low-Side N-Channel Controller for Switching Regulators

### **General Description**

The LM3488 is a versatile Low-Side N-FET high performance controller for switching regulators. It is suitable for use in topologies requiring low side FET, such as boost, flyback, SEPIC, etc. Moreover, the LM3488 can be operated at extremely high switching frequency in order to reduce the overall solution size. The switching frequency of LM3488 can be adjusted to any value between 100kHz and 1MHz by using a single external resistor or by synchronizing it to an external clock. Current mode control provides superior bandwidth and transient response, besides cycle-by-cycle current limiting. Output current can be programmed with a single external resistor.

The LM3488 has built in features such as thermal shutdown, short-circuit protection and over voltage protection. Power saving shutdown mode reduces the total supply current to 5µA and allows power supply sequencing. Internal soft-start limits the inrush current at start-up.

### **Key Specifications**

- Wide supply voltage range of 2.97V to 40V

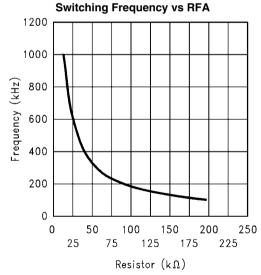

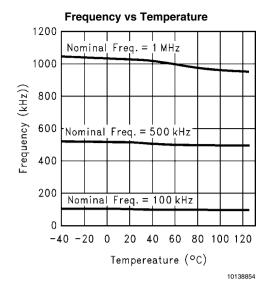

- 100kHz to 1MHz Adjustable and Synchronizable clock frequency

- ±1.5% (over temperature) internal reference

- 5µA shutdown current (over temperature)

### **Features**

- LM3488Q is AEC-Q100 qualified and manufactured on an Automotive Grade Flow

- 8-lead Mini-SO8 (MSOP-8) package

- Internal push-pull driver with 1A peak current capability

- Current limit and thermal shutdown

- Frequency compensation optimized with a capacitor and a resistor

- Internal softstart

- Current Mode Operation

- Undervoltage Lockout with hysteresis

### **Applications**

- Distributed Power Systems

- Notebook, PDA, Digital Camera, and other Portable Applications

- Offline Power Supplies

- Set-Top Boxes

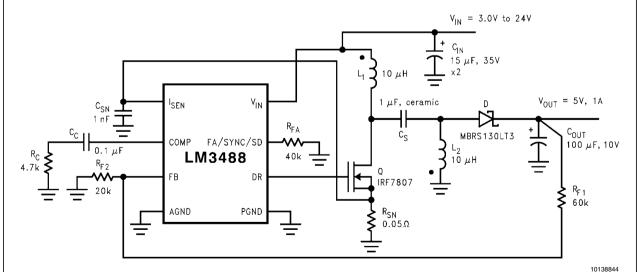

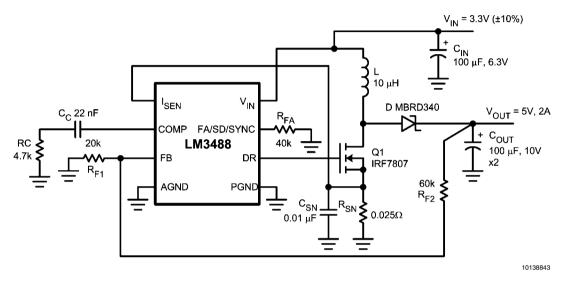

# **Typical Application Circuit**

**Typical SEPIC Converter**

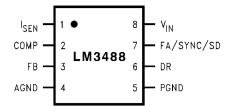

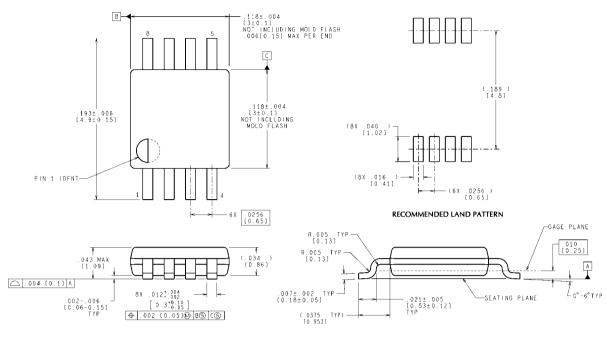

# **Connection Diagram**

8 Lead Mini SO8 Package (MSOP-8 Package)

# **Package Marking and Ordering Information**

| Order Number | Package Type | Package Marking | Supplied As                 | Feature                       |

|--------------|--------------|-----------------|-----------------------------|-------------------------------|

| LM3488MM     |              | S21B            | 1000 units on Tape and Reel |                               |

| LM3488MMX    |              | 5216            | 3500 units on Tape and Reel |                               |

| LM3488QMM    | MSOP-8       |                 | 1000 units on Tape and Reel | AEC-Q100 (Grade 1) qualified. |

| LM3488QMMX   |              | SSKB            | 3500 units on Tape and Reel | Automotive Grade Production   |

|              |              |                 |                             | Flow*                         |

<sup>\*</sup>Automotive Grade (Q) product incorporates enhanced manufacturing and support processes for the automotive market, including defect detection methodologies. Reliability qualification is compliant with the requirements and temperature grades defined in the AEC-Q100 standard. Automotive grade products are identified with the letter Q. For more information go to http://www.national.com/automotive.

# **Pin Descriptions**

| Pin Name         | Pin Number | Description                                                                                                                                                                                                                                                                                                                                      |  |

|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| I <sub>SEN</sub> | 1          | Current sense input pin. Voltage generated across an external sense resistor is fed into this pin.                                                                                                                                                                                                                                               |  |

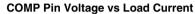

| COMP             | 2          | Compensation pin. A resistor, capacitor combination connected to this pin provides compensation for the control loop.                                                                                                                                                                                                                            |  |

| FB               | 3          | Feedback pin. The output voltage should be adjusted using a resistor divider to provide 1.26V at this pin.                                                                                                                                                                                                                                       |  |

| AGND             | 4          | Analog ground pin.                                                                                                                                                                                                                                                                                                                               |  |

| PGND             | 5          | Power ground pin.                                                                                                                                                                                                                                                                                                                                |  |

| DR               | 6          | Drive pin of the IC. The gate of the external MOSFET should be connected to this pin.                                                                                                                                                                                                                                                            |  |

| FA/SYNC/SD       | 7          | Frequency adjust, synchronization, and Shutdown pin. A resistor connected to this pin sets the oscillator frequency. An external clock signal at this pin will synchronize the controller to the frequency of the clock. A high level on this pin for ≥ 30µs will turn the device off. The device will then draw less than 10µA from the supply. |  |

| V <sub>IN</sub>  | 8          | Power supply input pin.                                                                                                                                                                                                                                                                                                                          |  |

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Susceptibilty

Human Body Model (*Note 2*)

Lead Temperature MM Package Vapor Phase (60 sec.) 215°C Infared (15 sec.) 260°C DR Pin Voltage -0.4V ≤ VDR ≤ 8V -0.4V -0.4V ≤ VDR ≤ 8V -0.4V -0.4

## **Operating Ratings** (Note 1)

Supply Voltage  $2.97V \le V_{IN} \le 40V$

Junction Temperature

Range  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le +125^{\circ}\text{C}$ Switching Frequency  $100\text{kHz} \le \text{F}_{\text{SW}} \le 1\text{MHz}$

### **Electrical Characteristics**

Specifications in Standard type face are for  $T_J$  = 25°C, and in **bold type face** apply over the full **Operating Temperature Range**. Unless otherwise specified,  $V_{IN}$  = 12V,  $R_{FA}$  = 40k $\Omega$

2kV

| Symbol                | Parameter                            | Conditions                                                        | Typical         | Limit               | Units     |

|-----------------------|--------------------------------------|-------------------------------------------------------------------|-----------------|---------------------|-----------|

| V <sub>FB</sub>       | Feedback Voltage                     | $V_{COMP} = 1.4V,$                                                | 1.26            |                     | V         |

|                       |                                      | 2.97 ≤ V <sub>IN</sub> ≤ 40V                                      |                 | 1.2507/ <b>1.24</b> | V(min)    |

|                       |                                      |                                                                   |                 | 1.2753/ <b>1.28</b> | V(max)    |

| $\Delta V_{LINE}$     | Feedback Voltage Line<br>Regulation  | 2.97 ≤ V <sub>IN</sub> ≤ 40V                                      | 0.001           |                     | %/V       |

| $\Delta V_{LOAD}$     | Output Voltage Load<br>Regulation    | I <sub>EAO</sub> Source/Sink                                      | ±0.5            |                     | %/V (max) |

| V <sub>UVLO</sub>     | Input Undervoltage Lock-out          |                                                                   | 2.85            |                     | V         |

| 0120                  |                                      |                                                                   |                 | 2.97                | V(max)    |

| V <sub>UV(HYS)</sub>  | Input Undervoltage Lock-out          |                                                                   | 170             |                     | mV        |

| o v ( o)              | Hysteresis                           |                                                                   |                 | 130                 | mV (min)  |

|                       |                                      |                                                                   |                 | 210                 | mV (max)  |

| F <sub>nom</sub>      | Nominal Switching Frequency          | $R_{EA} = 40K\Omega$                                              | 400             |                     | kHz       |

|                       |                                      | '^                                                                |                 | 360                 | kHz(min)  |

|                       |                                      |                                                                   |                 | 430                 | kHz(max)  |

| R <sub>DS1 (ON)</sub> | Driver Switch On Resistance (top)    | $I_{DR} = 0.2A, V_{IN} = 5V$                                      | 16              |                     | Ω         |

| R <sub>DS2 (ON)</sub> | Driver Switch On Resistance (bottom) | I <sub>DR</sub> = 0.2A                                            | 4.5             |                     | Ω         |

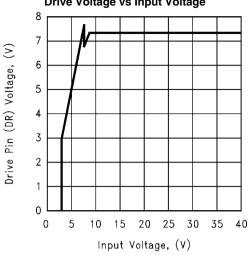

| V <sub>DR (max)</sub> | Maximum Drive Voltage                | V <sub>IN</sub> < 7.2V                                            | V <sub>IN</sub> |                     | V         |

| Swii                  | Swing( <i>Note 6</i> )               | V <sub>IN</sub> ≥ 7.2V                                            | 7.2             |                     | -         |

| D <sub>max</sub>      | Maximum Duty Cycle(Note 7)           | IIV.                                                              | 100             |                     | %         |

| T <sub>min</sub> (on) | Minimum On Time                      |                                                                   | 325             |                     | nsec      |

| · min (o)             |                                      |                                                                   | 0_0             | 230                 | nsec(min) |

|                       |                                      |                                                                   |                 | 550                 | nsec(max) |

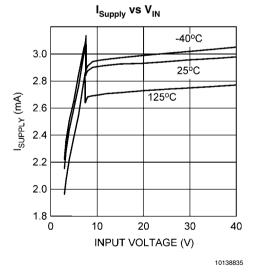

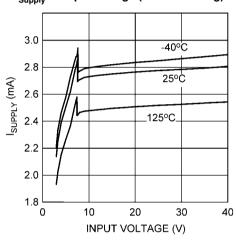

| I <sub>SUPPLY</sub>   | Supply Current (switching)           | (Note 9)                                                          |                 |                     | mA        |

| SUFFLI                | 3,                                   | ,                                                                 | 2.7             | 3.0                 | mA (max)  |

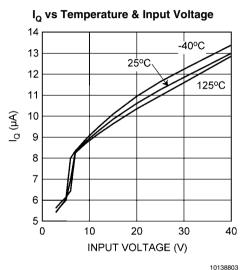

| I <sub>Q</sub>        | Quiescent Current in                 | V <sub>FA/SYNC/SD</sub> = 5V( <i>Note 10</i> ), V <sub>IN</sub> = | 5               |                     | μA        |

| Q                     | Shutdown Mode                        | 5V                                                                |                 | 7                   | μA (max)  |

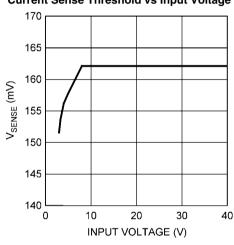

| V <sub>SENSE</sub>    | Current Sense Threshold              | V <sub>IN</sub> = 5V                                              | 156             |                     | mV        |

| SENSE                 | Voltage                              | -                                                                 |                 | 135/ <b>125</b>     | mV (min)  |

|                       | 195                                  |                                                                   |                 | 180/ <b>190</b>     | mV (max)  |

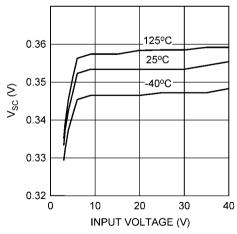

| V <sub>SC</sub>       | Short-Circuit Current Limit          | V <sub>IN</sub> = 5V                                              | 343             |                     | mV        |

| <b>V</b> SC           | Sense Voltage                        |                                                                   | 0.10            | 250                 | mV (min)  |

|                       | Comago                               |                                                                   |                 | 415                 | mV (max)  |

| Symbol              | Parameter                                     | Conditions                                             | Typical  | Limit             | Units                    |

|---------------------|-----------------------------------------------|--------------------------------------------------------|----------|-------------------|--------------------------|

| $\overline{V_{SL}}$ | Internal Compensation Ramp                    | V <sub>IN</sub> = 5V                                   | 92       |                   | mV                       |

|                     | Voltage                                       |                                                        |          | 52                | mV(min)                  |

|                     |                                               |                                                        |          | 132               | mV(max)                  |

| $V_{\rm SL}$ ratio  | V <sub>SL</sub> /V <sub>SENSE</sub>           |                                                        | 0.49     | 0.30              | (min)                    |

|                     |                                               |                                                        |          | 0.70              | (max)                    |

| $V_{OVP}$           | Output Over-voltage                           | $V_{COMP} = 1.4V$                                      | 50       |                   | mV                       |

|                     | Protection (with respect to                   |                                                        |          | 32/ <b>25</b>     | mV(min)                  |

|                     | feedback voltage) (Note 8)                    |                                                        |          | 78/ <b>85</b>     | mV(max)                  |

| $V_{OVP(HYS)}$      | Output Over-Voltage                           | $V_{COMP} = 1.4V$                                      | 60       | 00                | mV                       |

|                     | Protection Hysteresis( <i>Note 8</i> )        |                                                        |          | 20                | mV(min)                  |

| 0                   | F A. A if a                                   | )/ 4 4 V                                               | 000      | 110               | mV(max)                  |

| Gm                  | Error Ampifier                                | V <sub>COMP</sub> = 1.4V                               | 800      | 600/ <b>365</b>   | µmho                     |

|                     | Transconductance                              | I <sub>EAO</sub> = 100μA (Source/Sink)                 |          | 1000/ <b>1265</b> | μmho (min)<br>μmho (max) |

| A <sub>VOL</sub>    | Error Amplifier Voltage Gain                  | $V_{COMP} = 1.4V$                                      | 38       |                   | V/V                      |

| .02                 |                                               | I <sub>EAO</sub> = 100μA (Source/Sink)                 |          | 26                | V/V (min)                |

|                     |                                               |                                                        |          | 44                | V/V (max)                |

| I <sub>EAO</sub>    | Error Amplifier Output Current (Source/ Sink) | Source, V <sub>COMP</sub> = 1.4V, V <sub>FB</sub> = 0V | 110      |                   | μΑ                       |

|                     |                                               |                                                        |          | 80/ <b>50</b>     | μA (min)                 |

|                     |                                               |                                                        |          | 140/ <b>180</b>   | μA (max)                 |

|                     |                                               | Sink, $V_{COMP} = 1.4V$ , $V_{FB} = 1.4V$              | -140     |                   | μΑ                       |

|                     |                                               |                                                        |          | -100/ <b>-85</b>  | μA (min)                 |

|                     |                                               |                                                        |          | -180/ <b>-185</b> | μA (max)                 |

| $V_{EAO}$           | Error Amplifier Output Voltage                |                                                        | 2.2      |                   | V                        |

|                     | Swing                                         | V <sub>FB</sub> = 0V                                   |          | 1.8               | V(min)                   |

|                     |                                               | COMP Pin = Floating                                    | 2.50     | 2.4               | V(max)                   |

|                     |                                               | Lower Limit                                            | 0.56     |                   | V                        |

|                     |                                               | V <sub>FB</sub> = 1.4V                                 |          | 0.2<br>1.0        | V(min)<br>V(max)         |

| <del></del>         | Internal Soft Start Dalay                     | V - 1 2V V - Floating                                  | 4        | 1.0               |                          |

| T <sub>SS</sub>     | Internal Soft-Start Delay                     | $V_{FB} = 1.2V$ , $V_{COMP} = Floating$                |          |                   | msec                     |

| T <sub>r</sub>      | Drive Pin Rise Time                           | Cgs = 3000pf, V <sub>DR</sub> = 0 to 3V                | 25       |                   | ns                       |

| T <sub>f</sub>      | Drive Pin Fall Time                           | Cgs = 3000pf, V <sub>DR</sub> = 0 to 3V                | 25       |                   | ns                       |

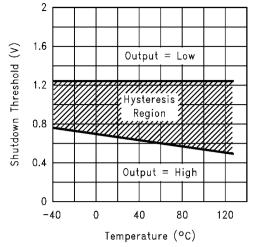

| VSD                 | Shutdown and                                  | Output = High                                          | 1.27     |                   | V                        |

|                     | Synchronization signal                        |                                                        |          | 1.4               | V (max)                  |

|                     | threshold (Note 5)                            | Output = Low                                           | 0.65     |                   | V                        |

|                     |                                               |                                                        | <u> </u> | 0.3               | V (min)                  |

| I <sub>SD</sub>     | Shutdown Pin Current                          | V <sub>SD</sub> = 5V                                   | -1       |                   | μΑ                       |

|                     |                                               | $V_{SD} = 0V$                                          | +1       |                   |                          |

| I <sub>FB</sub>     | Feedback Pin Current                          |                                                        | 15       |                   | nA                       |

| TSD                 | Thermal Shutdown                              |                                                        | 165      |                   | °C                       |

| T <sub>sh</sub>     | Thermal Shutdown Hysteresis                   |                                                        | 10       |                   | °C                       |

| $\theta_{JA}$       | Thermal Resistance                            | MM Package                                             | 200      |                   | °C/W                     |

Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: The human body model is a 100 pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin.

**Note 3:** All limits are guaranteed at room temperature (standard type face) and at **temperature extremes (bold type face)**. All room temperature limits are 100% tested. All limits at **temperature extremes** are guaranteed via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Note 4: Typical numbers are at 25°C and represent the most likely norm.

Note 5: The FA/SYNC/SD pin should be pulled to V<sub>IN</sub> through a resistor to turn the regulator off.

Note 6: The voltage on the drive pin, V<sub>DR</sub> is equal to the input voltage when input voltage is less than 7.2V. V<sub>DR</sub> is equal to 7.2V when the input voltage is greater than or equal to 7.2V.

Note 7: The limits for the maximum duty cycle can not be specified since the part does not permit less than 100% maximum duty cycle operation.

**Note 8:** The over-voltage protection is specified with respect to the feedback voltage. This is because the over-voltage protection tracks the feedback voltage. The over-voltage thresold can be calculated by adding the feedback voltage, V<sub>FB</sub> to the over-voltage protection specification.

Note 9: For this test, the FA/SYNC/SD Pin is pulled to ground using a 40K resistor .

Note 10: For this test, the FA/SYNC/SD Pin is pulled to 5V using a 40K resistor.

# Typical Performance Characteristics Unless otherwise specified, V<sub>IN</sub> = 12V, T<sub>J</sub> = 25°C.

### I<sub>Supply</sub> vs Input Voltage (Non-Switching)

10138834

10138804

**Current Sense Threshold vs Input Voltage**

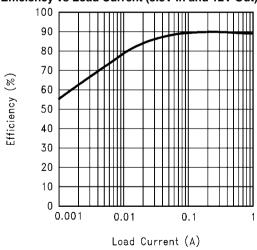

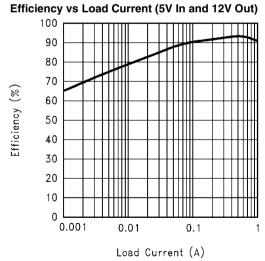

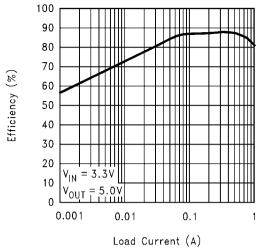

Efficiency vs Load Current (3.3V In and 12V Out)

10138845

10138859

**Drive Voltage vs Input Voltage**

10138805

10138858

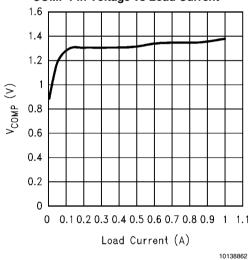

### Efficiency vs Load Current (9V In and 12V Out)

10138860

10138855

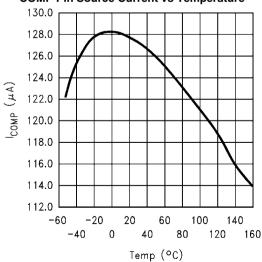

### **COMP Pin Source Current vs Temperature**

Frequency (kHz)

10138836

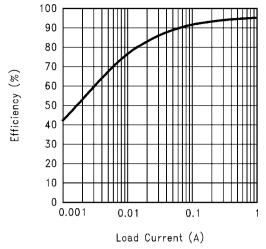

#### Efficiency vs Load Current (3.3V In and 5V Out)

10138853

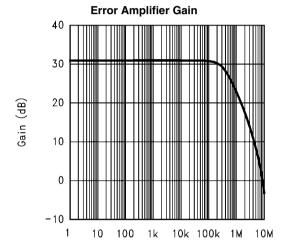

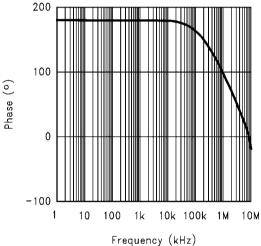

#### **Error Amplifier Phase**

riequency (Kiiz)

10138856

#### **Short Circuit Protection vs Input Voltage**

10138857

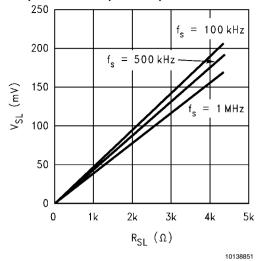

### **Compensation Ramp vs Compensation Resistor**

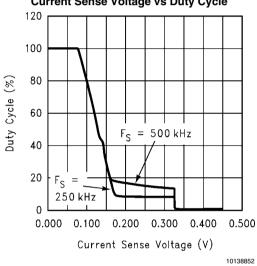

### **Current Sense Voltage vs Duty Cycle**

### **Shutdown Threshold Hysteresis vs Temperature**

10138846

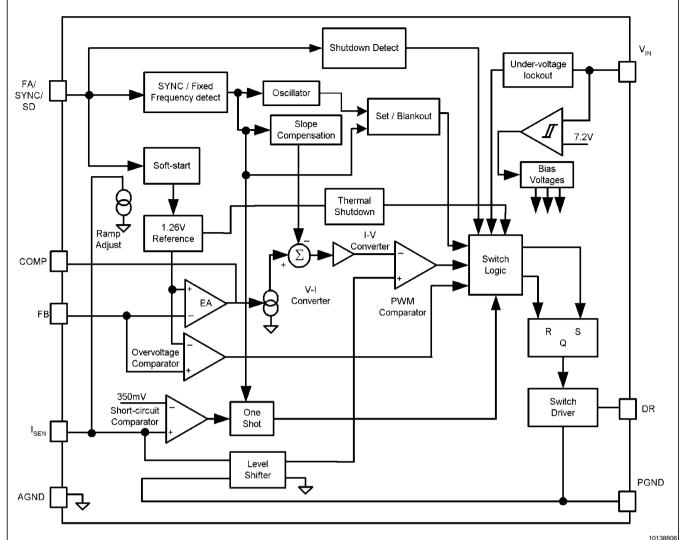

## **Functional Block Diagram**

## **Functional Description**

The LM3488 uses a fixed frequency, Pulse Width Modulated (PWM), current mode control architecture. In a typical application circuit, the peak current through the external MOSFET is sensed through an external sense resistor. The voltage across this resistor is fed into the I<sub>SEN</sub> pin. This voltage is then level shifted and fed into the positive input of the PWM comparator. The output voltage is also sensed through an external feedback resistor divider network and fed into the error amplifier negative input (feedback pin, FB). The output of the error amplifier (COMP pin) is added to the slope compensation ramp and fed into the negative input of the PWM comparator.

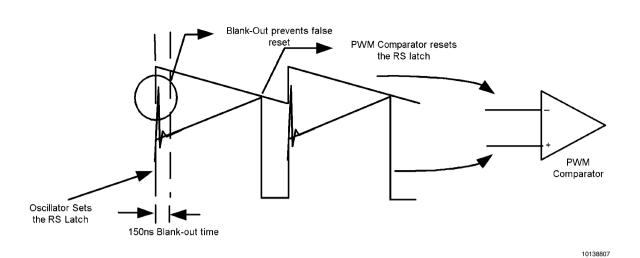

At the start of any switching cycle, the oscillator sets the RS latch using the SET/Blank-out and switch logic blocks. This forces a high signal on the DR pin (gate of the external MOSFET) and the external MOSFET turns on. When the voltage on the positive input of the PWM comparator exceeds the negative input, the RS latch is reset and the external MOSFET turns off.

The voltage sensed across the sense resistor generally contains spurious noise spikes, as shown in *Figure 1*. These spikes can force the PWM comparator to reset the RS latch prematurely. To prevent these spikes from resetting the latch, a blank-out circuit inside the IC prevents the PWM comparator from resetting the latch for a short duration after the latch is set. This duration is about 150ns and is called the blank-out time.

Under extremely light load or no-load conditions, the energy delivered to the output capacitor when the external MOSFET is on during the blank-out time is more than what is delivered to the load. An over-voltage comparator inside the LM3488 prevents the output voltage from rising under these conditions. The over-voltage comparator senses the feedback (FB pin) voltage and resets the RS latch under these conditions. The latch remains in reset state till the output decays to the nominal value.

FIGURE 1. Basic Operation of the PWM comparator

SLOPE COMPENSATION RAMP

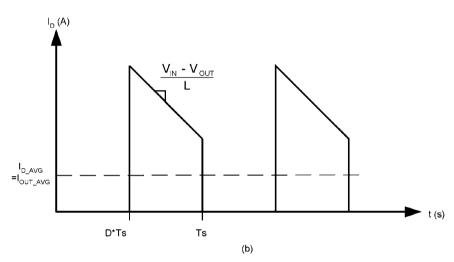

The LM3488 uses a current mode control scheme. The main advantages of current mode control are inherent cycle-by-cycle current limit for the switch, and simpler control loop characteristics. It is also easy to parallel power stages using current mode control since as current sharing is automatic.

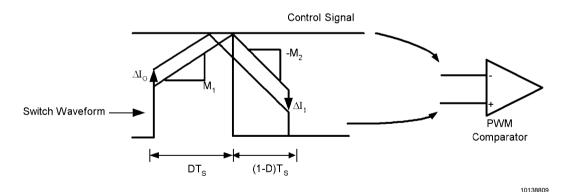

Current mode control has an inherent instability for duty cycles greater than 50%, as shown in *Figure 2*. In *Figure 2*, a small increase in the load current causes the switch current to increase by  $\Delta I_0$ . The effect of this load change,  $\Delta I_1$ , is:

$$\Delta I_1 = -\left(\frac{M_2}{M_1}\right) \Delta I_0 = -\left(\frac{D}{1-D}\right) \Delta I_0$$

From the above equation, when D > 0.5,  $\Delta I_1$  will be greater than  $\Delta I_0$ . In other words, the disturbance is divergent. So a very small perturbation in the load will cause the disturbance to increase.

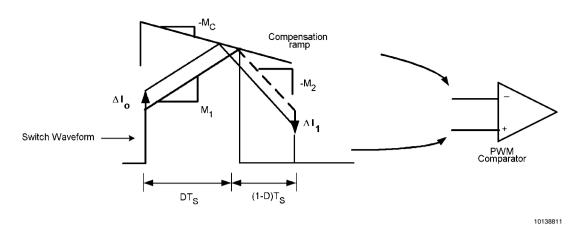

To prevent the sub-harmonic oscillations, a compensation ramp is added to the control signal, as shown in *Figure 3*. With the compensation ramp,

$$\Delta I_1 = -\left(\frac{M_2 - M_C}{M_1 + M_C}\right) \Delta I_O$$

FIGURE 2. Sub-Harmonic Oscillation for D>0.5

FIGURE 3. Compensation Ramp Avoids Sub-Harmonic Oscillation

The compensation ramp has been added internally in LM3488. The slope of this compensation ramp has been selected to satisfy most of the applications. The slope of the internal compensation ramp depends on the frequency. This slope can be calculated using the formula:

$$M_C = V_{SL}.F_S$$

Volts/second

In the above equation,  $V_{SL}$  is the amplitude of the internal compensation ramp. Limits for  $V_{SL}$  have been specified in the electrical characteristics.

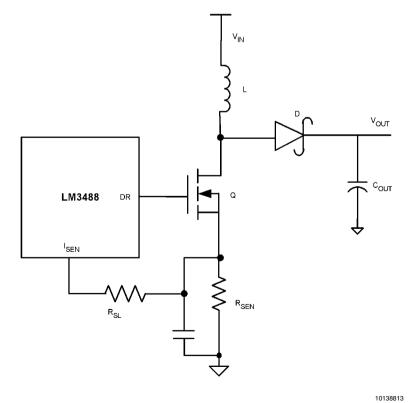

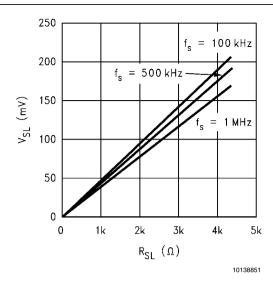

In order to provide the user additional flexibility, a patented scheme has been implemented inside the IC to increase the slope of the compensation ramp externally, if the need arises. Adding a single external resistor,  $R_{SL}(as\ shown\ in\ \mbox{\it Figure\ 4})$  increases the slope of the compensation ramp,  $M_C$  by :

$$\Delta M_C = \frac{40 \times 10^{-6} \cdot R_{SL} \cdot F_S}{R_{SEN}} \frac{Amps}{second}$$

In this equation,  $\Delta V_{SL}$  is equal to 40.10-6R  $_{SL}.$  Hence,

$$\Delta M_{\rm C} = \frac{\Delta V_{\rm SL}.F_{\rm S}}{R_{\rm SEN}} \frac{\rm Amps}{\rm second}$$

$\Delta V_{SL}$  versus  $R_{SL}$  has been plotted in  $\emph{Figure 5}$  for different frequencies.

FIGURE 4. Increasing the Slope of the Compensation Ramp

11

FIGURE 5.  $\Delta V_{SL}$  vs R<sub>SL</sub>

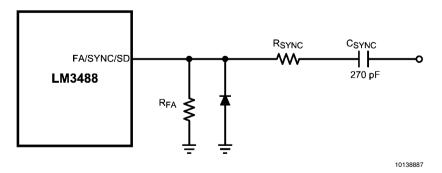

#### FREQUENCY ADJUST/SYNCHRONIZATION/SHUTDOWN

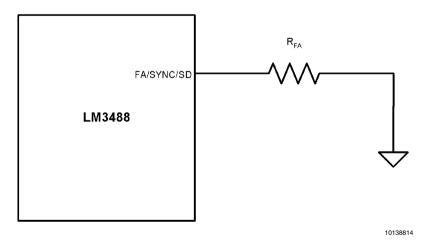

The switching frequency of LM3488 can be adjusted between 100kHz and 1MHz using a single external resistor. This resistor must be connected between FA/SYNC/SD pin and ground, as shown in *Figure 6*. Please refer to the typical performance characteristics to determine the value of the resistor required for a desired switching frequency.

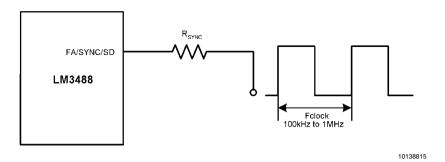

The LM3488 can be synchronized to an external clock. The external clock must be connected to the FA/SYNC/SD pin through a resistor,  $R_{\rm SYNC}$  as shown in Figure 7. The value of this resistor is dependent on the off time of the synchronization pulse,  $T_{\rm OFF(SYNC)}$ . Table 1 shows the range of resistors to be used for a given  $T_{\rm OFF(SYNC)}$ .

TABLE 1.

| T <sub>OFF(SYNC)</sub> (μsec) | R <sub>SYNC</sub> range (kΩ) |  |

|-------------------------------|------------------------------|--|

| 1                             | 5 to 13                      |  |

| 2                             | 20 to 40                     |  |

| 3                             | 40 to 65                     |  |

| 4                             | 55 to 90                     |  |

| 5                             | 70 to 110                    |  |

| 6                             | 85 to 140                    |  |

| 7                             | 100 to 160                   |  |

| 8                             | 120 to 190                   |  |

| 9                             | 135 to 215                   |  |

| 10                            | 150 to 240                   |  |

It is also necessary to have the width of the synchronization pulse wider than the duty cycle of the converter (when DR pin is high and the switching point is low). It is also necessary to have the synchronization pulse width  $\geq$  300nsecs.

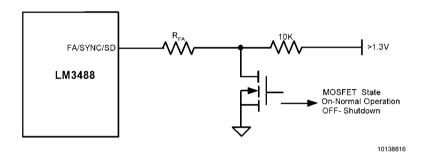

The FA/SYNC/SD pin also functions as a shutdown pin. If a high signal (refer to the electrical characteristics for definition of high signal) appears on the FA/SYNC/SD pin, the LM3488 stops switching and goes into a low current mode. The total supply current of the IC reduces to less than  $10\mu\text{A}$  under these conditions.

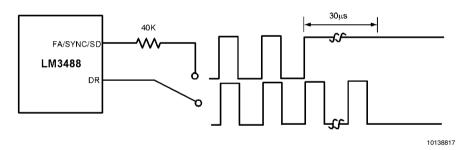

Figure 8 and Figure 9 show implementation of shutdown function when operating in Frequency adjust mode and synchronization mode respectively. In frequency adjust mode, connecting the FA/SYNC/SD pin to ground forces the clock to run at a certain frequency. Pulling this pin high shuts down the IC. In frequency adjust or synchronization mode, a high signal for more than 30µs shuts down the IC.

Figure 10 shows implementation of both frequency adjust with  $\rm R_{FA}$  resistor and frequency synchronization with  $\rm R_{SYNC}$ . The switching frequency is defined by  $\rm R_{FA}$  when a synchronization signal is not applied. When sync is applied it overrides the  $\rm R_{FA}$  setting.

**FIGURE 6. Frequency Adjust**

FIGURE 7. Frequency Synchronization

FIGURE 8. Shutdown Operation in Frequency Adjust Mode

FIGURE 9. Shutdown Operation in Synchronization Mode

FIGURE 10. Frequency Adjust or Frequency Synchronization

#### **SHORT-CIRCUIT PROTECTION**

When the voltage across the sense resistor (measured on  $I_{\rm SEN}$  Pin) exceeds 350mV, short-circuit current limit gets acti-

vated. A comparator inside LM3488 reduces the switching frequency by a factor of 5 and maintains this condition till the short is removed.

# **Typical Applications**

The LM3488 may be operated in either continuous or discontinuous conduction mode. The following applications are designed for continuous conduction operation. This mode of operation has higher efficiency and lower EMI characteristics than the discontinuous mode.

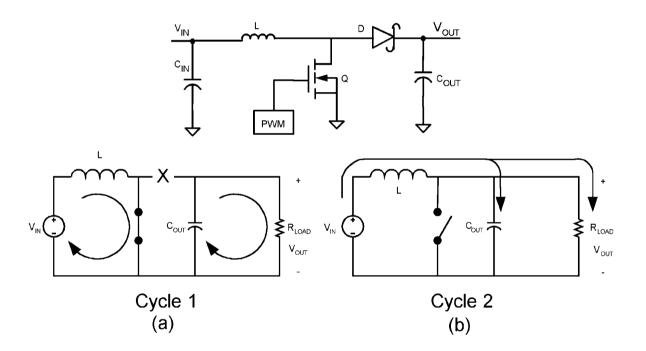

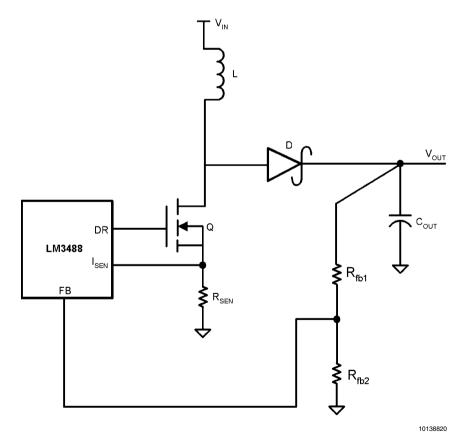

#### **BOOST CONVERTER**

The most common topology for LM3488 is the boost or step-up topology. The boost converter converts a low input voltage into a higher output voltage. The basic configuration for a boost regulator is shown in *Figure 11*. In continuous conduction mode (when the inductor current never reaches zero at steady state), the boost regulator operates in two cycles. In the first cycle of operation, MOSFET Q is turned on and energy is stored in the inductor. During this cycle, diode D is reverse biased and load current is supplied by the output capacitor,  $\mathbf{C}_{\text{OUT}}$ .

In the second cycle, MOSFET Q is off and the diode is forward biased. The energy stored in the inductor is transferred to the

load and output capacitor. The ratio of these two cycles determines the output voltage. The output voltage is defined as:

$$V_{OUT} = \frac{V_{IN}}{1-D}$$

(ignoring the drop across the MOSFET and the diode), or

$$V_{OUT} + V_D = \frac{V_{IN} - V_Q}{1 - D}$$

where D is the duty cycle of the switch,  $V_D$  is the forward voltage drop of the diode, and  $V_Q$  is the drop across the MOSFET when it is on. The following sections describe selection of components for a boost converter.

FIGURE 11. Simplified Boost Converter Diagram (a) First cycle of operation. (b) Second cycle of operation

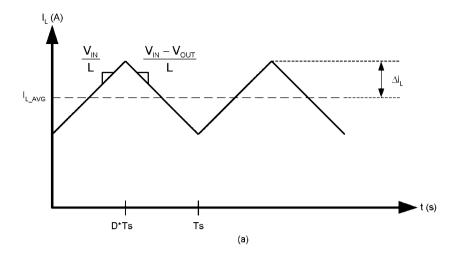

#### **POWER INDUCTOR SELECTION**

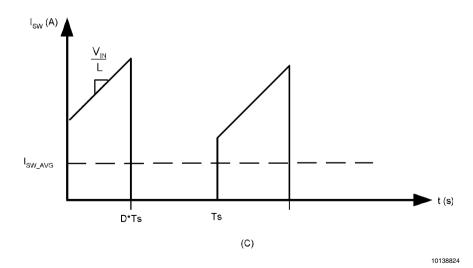

The inductor is one of the two energy storage elements in a boost converter. *Figure 12* shows how the inductor current varies during a switching cycle. The current through an inductor is quantified as:

$$V_L(t) = L \frac{di_L(t)}{dt}$$

FIGURE 12. A. Inductor Current B. Diode Current

If  $V_L(t)$  is constant,  $di_L(t)/dt$  must be constant. Hence, for a given input voltage and output voltage, the current in the inductor changes at a constant rate.

The important quantities in determining a proper inductance value are  $\overline{l}_L$  (the average inductor current) and  $\Delta i_L$  (the inductor current ripple). If  $\Delta i_L$  is larger than  $\overline{l}_L$ , the inductor current will drop to zero for a portion of the cycle and the converter

will operate in discontinuous conduction mode. If  $\Delta i_L$  is smaller than  $\bar{l}_L$ , the inductor current will stay above zero and the converter will operate in continuous conduction mode. All the analysis in this datasheet assumes operation in continuous conduction mode. To operate in continuous conduction mode, the following conditions must be met:

$$\bar{l}_1 > \Delta i_1$$

$$\frac{I_{OUT}}{1-D} > \frac{DV_{IN}}{2f_{c}L}$$

$$L > \frac{D(1-D)V_{\parallel}}{2I_{\text{out}}f_{\text{s}}}$$

Choose the minimum  $I_{OUT}$  to determine the minimum L. A common choice is to set  $\Delta i_L$  to 30% of  $\overline{l}_L$ . Choosing an appropriate core size for the inductor involves calculating the average and peak currents expected through the inductor. In a boost converter,

$$\bar{I}_L = \frac{I_{OUT}}{1-D}$$

and

$$I_{L_peak} = \bar{I}_L(max) + \Delta i_L(max)$$

, where

$$\Delta i_L = \frac{DV_{IN}}{2f_SL}$$

A core size with ratings higher than these values should be chosen. If the core is not properly rated, saturation will dramatically reduce overall efficiency.

The LM3488 can be set to switch at very high frequencies. When the switching frequency is high, the converter can be operated with very small inductor values. With a small inductor value, the peak inductor current can be extremely higher than the output currents, especially under light load conditions.

The LM3488 senses the peak current through the switch. The peak current through the switch is the same as the peak current calculated above.

#### PROGRAMMING THE OUTPUT VOLTAGE

The output voltage can be programmed using a resistor divider between the output and the feedback pins, as shown in *Figure 13*. The resistors are selected such that the voltage at the feedback pin is 1.26V.  $R_{\rm F1}$  and  $R_{\rm F2}$  can be selected using the equation,

$$V_{OUT} = 1.26 \left(1 + \frac{R_{F1}}{R_{F2}}\right)$$

A 100pF capacitor may be connected between the feedback and ground pins to reduce noise.

FIGURE 13. Adjusting the Output Voltage

#### SETTING THE CURRENT LIMIT

The maximum amount of current that can be delivered to the load is set by the sense resistor,  $R_{\rm SEN}.$  Current limit occurs when the voltage that is generated across the sense resistor equals the current sense threshold voltage,  $V_{\rm SENSE}.$  When this threshold is reached, the switch will be turned off until the next cycle. Limits for  $V_{\rm SENSE}$  are specified in the electrical characteristics section.  $V_{\rm SENSE}$  represents the maximum value of the internal control signal  $V_{\rm CS}.$  This control signal, however, is not a constant value and changes over the course of a period as a result of the internal compensation ramp (See Figure 3). Therefore the current limit threshold will also change. The actual current limit threshold is a function of the sense voltage ( $V_{\rm SENSE}$ ) and the internal compensation ramp:

$$R_{SEN} x ISW_{LIMIT} = VCS_{MAX} = V_{SENSE} - (D x V_{SL})$$

Where ISW<sub>LIMIT</sub> is the peak switch current limit, defined by the equation below. As duty cycle increases, the control voltage is reduced as  $V_{SL}$  ramps up. Since current limit threshold varies with duty cycle, the following equation should be used to select  $R_{SEN}$  and set the desired current limit threshold:

$$R_{SEN} = \frac{V_{SENSE} - (D \times V_{SL})}{ISW_{LIMIT}}$$

The numerator of the above equation is  $V_{CS}$ , and ISW<sub>LIMIT</sub> is calculated as:

$$ISW_{LIMIT} = \left[ \frac{I_{OUT}}{(1-D)} + \frac{(D \times V_{IN})}{(2 \times f_S \times L)} \right]$$

To avoid false triggering, the current limit value should have some margin above the maximum operating value, typically 120%. Values for both  $\rm V_{SENSE}$  and  $\rm V_{SL}$  are specified in the characteristic table. However, calculating with the limits of these two specs could result in an unrealistically wide current limit or  $\rm R_{SEN}$  range. Therefore, the following equation is recommended, using the  $\rm V_{SL}$  ratio value given in the EC table:

$$R_{SEN} = \frac{V_{SENSE} - (D \times V_{SENSE} \times V_{SL} ratio)}{ISW_{LIMIT}}$$

$R_{SEN}$  is part of the current mode control loop and has some influence on control loop stability. Therefore, once the current limit threshold is set, loop stability must be verified. To verify stability, use the following equation:

$$R_{SEN} < \frac{2 \times V_{SL} \times f_{S} \times L}{V_{O} - (2 \times V_{IN})}$$

If the selected  $R_{\text{SEN}}$  is greater than this value, additional slope compensation must be added to ensure stability, as described in the section below.

# CURRENT LIMIT WITH EXTERNAL SLOPE COMPENSATION

$R_{SL}$  is used to add additional slope compensation when required. It is not necessary in most designs and  $R_{SL}$  should be no larger than necessary. Select  $R_{SL}$  according to the following equation:

$$R_{SL} > \frac{R_{SEN} \ x \ (Vo - 2V_{IN})}{2 \ x \ f_S \ x \ L} - V_{SL}}{40 \ \mu A}$$

Where  $R_{SEN}$  is the selected value based on current limit. With  $R_{SL}$  installed, the control signal includes additional external slope to stabilize the loop, which will also have an effect on the current limit threshold. Therefore, the current limit threshold must be re-verified, as illustrated in the equations below :

$$V_{CS} = V_{SENSE} - (D \times (V_{SL} + \Delta V_{SL}))$$

Where  $\Delta V_{SL}$  is the additional slope compensation generated and calculated as:

$$\Delta V_{SL}$$

= 40  $\mu A$  x  $R_{SL}$

This changes the equation for current limit (or R<sub>SEN</sub>) to:

$$ISW_{LIMIT} = \frac{V_{SENSE} - (D x(V_{SL} + \Delta V_{SL}))}{R_{SEN}}$$

The  $R_{SEN}$  and  $R_{SL}$  values may have to be calculated iteratively in order to achieve both the desired current limit and stable operation. In some designs  $R_{SL}$  can also help to filter noise on the ISEN pin.

If the inductor is selected such that ripple current is the recommended 30% value, and the current limit threshold is 120% of the maximum peak, a simpler method can be used to determine  $R_{\text{SEN}}.$  The equation below will provide optimum stability without RSL, provided that the above 2 conditions are met:

$$R_{SEN} = \frac{V_{SENSE}}{ISW_{LIMIT} + \left(\frac{Vo - Vi}{L \times f_S}\right) \times D}$$

### POWER DIODE SELECTION

Observation of the boost converter circuit shows that the average current through the diode is the average load current, and the peak current through the diode is the peak current through the inductor. The diode should be rated to handle more than its peak current. The peak diode current can be calculated using the formula:

$$I_{D(Peak)} = I_{OUT} / (1-D) + \Delta I_{L}$$

In the above equation,  $I_{OUT}$  is the output current and  $\Delta I_L$  has been defined in Figure 12

The peak reverse voltage for boost converter is equal to the regulator output voltage. The diode must be capable of handling this voltage. To improve efficiency, a low forward drop schottky diode is recommended.

#### **POWER MOSFET SELECTION**

The drive pin of LM3488 must be connected to the gate of an external MOSFET. In a boost topology, the drain of the external N-Channel MOSFET is connected to the inductor and the source is connected to the ground. The drive pin (DR) voltage depends on the input voltage (see typical performance characteristics). In most applications, a logic level MOSFET can be used. For very low input voltages, a sublogic level MOSFET should be used.

The selected MOSFET directly controls the efficiency. The critical parameters for selection of a MOSFET are:

www.national.com

1. Minimum threshold voltage, V<sub>TH</sub>(MIN)

- 2. On-resistance, R<sub>DS</sub>(ON)

- 3. Total gate charge, Q<sub>q</sub>

- Reverse transfer capacitance, C<sub>RSS</sub>

- 5. Maximum drain to source voltage, V<sub>DS(MAX)</sub>

The off-state voltage of the MOSFET is approximately equal to the output voltage.  $V_{\rm DS(MAX)}$  of the MOSFET must be greater than the output voltage. The power losses in the MOSFET can be categorized into conduction losses and ac switching or transition losses.  $R_{\rm DS(ON)}$  is needed to estimate the conduction losses. The conduction loss,  $P_{\rm COND}$ , is the I²R loss across the MOSFET. The maximum conduction loss is given by:

$$P_{\text{COND(MAX)}} = \left[ \left( \frac{I_{\text{OUT}}}{1 - D_{\text{MAX}}} \right)^2 + \left( \frac{\Delta I}{3} \right) \right] D_{\text{MAX}} R_{\text{DS(ON)}}$$

where D<sub>MAX</sub> is the maximum duty cycle.

$$D_{MAX} = \left(1 - \frac{V_{IN}(MIN)}{V_{OUT}}\right)$$

The turn-on and turn-off transitions of a MOSFET require times of tens of nano-seconds.  $C_{\text{RSS}}$  and  $Q_g$  are needed to estimate the large instantaneous power loss that occurs during these transitions.

The amount of gate current required to turn the MOSFET on can be calculated using the formula:

$$I_G = Q_a \cdot F_S$$

The required gate drive power to turn the MOSFET on is equal to the switching frequency times the energy required to deliver the charge to bring the gate charge voltage to  $V_{DR}$  (see electrical characteristics and typical performance characteristics for the drive voltage specification).

$$P_{Drive} = F_S.Q_q.V_{DR}$$

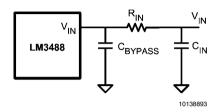

### **INPUT CAPACITOR SELECTION**

Due to the presence of an inductor at the input of a boost converter, the input current waveform is continuous and triangular, as shown in *Figure 12*. The inductor ensures that the input capacitor sees fairly low ripple currents. However, as the input capacitor gets smaller, the input ripple goes up. The rms current in the input capacitor is given by:

$$I_{\text{CIN(RMS)}} = \Delta i_{\text{L}} / \sqrt{3} = \frac{1}{2\sqrt{3}} \left( \frac{V_{\text{OUT}} - V_{\text{IN}}}{V_{\text{OUT}} L f_{\text{S}}} \right)$$

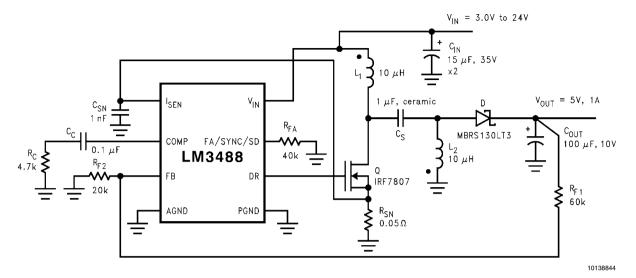

# **Designing SEPIC Using LM3488**

Since the LM3488 controls a low-side N-Channel MOSFET, it can also be used in SEPIC (Single Ended Primary Inductance Converter) applications. An example of SEPIC using LM3488 is shown in *Figure 15*. As shown in *Figure 15*, the output voltage can be higher or lower than the input voltage. The SEPIC uses two inductors to step-up or step-down the input voltage. The inductors L1 and L2 can be two discrete inductors or two windings of a coupled transformer since equal voltages are applied across the inductor throughout the switching cycle. Using two discrete inductors allows use of catalog magnetics, as opposed to a custom transformer. The input ripple can be reduced along with size by using the coupled windings of transformer for L1 and L2.

The input capacitor should be capable of handling the rms current. Although the input capacitor is not as critical in a boost application, low values can cause impedance interactions. Therefore a good quality capacitor should be chosen in the range of  $10\mu F$  to  $20\mu F$ . If a value lower than  $10\mu F$  is used, then problems with impedance interactions or switching noise can affect the LM3478. To improve performance, especially with  $V_{IN}$  below 8 volts, it is recommended to use a  $20\Omega$  resistor at the input to provide a RC filter. The resistor is placed in series with the  $V_{IN}$  pin with only a bypass capacitor attached to the  $V_{IN}$  pin directly (see Figure 14). A  $0.1\mu F$  or  $1\mu F$  ceramic capacitor is necessary in this configuration. The bulk input capacitor and inductor will connect on the other side of the resistor with the input power supply.

FIGURE 14. Reducing IC Input Noise

#### **OUTPUT CAPACITOR SELECTION**

The output capacitor in a boost converter provides all the output current when the inductor is charging. As a result it sees very large ripple currents. The output capacitor should be capable of handling the maximum rms current. The rms current in the output capacitor is:

$$I_{\text{COUT(RMS)}} = \sqrt{\text{(1-D)}\left[I_{\text{OUT}}^2 \frac{D}{(1-D)^2} + \frac{\Delta i_L^2}{3}\right]}$$

Where

$$\Delta i_{L} = \frac{DV_{IN}}{2Lf_{S}}$$

and D, the duty cycle is equal to  $(V_{OUT} - V_{IN})/V_{OUT}$ .

The ESR and ESL of the output capacitor directly control the output ripple. Use capacitors with low ESR and ESL at the output for high efficiency and low ripple voltage. Surface Mount tantalums, surface mount polymer electrolytic and polymer tantalum, Sanyo-OSCON, or multi-layer ceramic capacitors are recommended at the output.

Due to the presence of the inductor L1 at the input, the SEPIC inherits all the benefits of a boost converter. One main advantage of SEPIC over boost converter is the inherent input to output isolation. The capacitor CS isolates the input from the output and provides protection against shorted or malfunctioning load. Hence, the A SEPIC is useful for replacing boost circuits when true shutdown is required. This means that the output voltage falls to 0V when the switch is turned off. In a boost converter, the output can only fall to the input voltage minus a diode drop.

The duty cycle of a SEPIC is given by:

$$D = \frac{V_{\text{OUT}} + V_{\text{DIODE}}}{V_{\text{OUT}} + V_{\text{IN}} - V_{\text{Q}} + V_{\text{DIODE}}}$$

In the above equation,  $V_Q$  is the on-state voltage of the MOSFET, Q, and  $V_{DIODE}$  is the forward voltage drop of the diode.

FIGURE 15. Typical SEPIC Converter

#### **POWER MOSFET SELECTION**

As in boost converter, the parameters governing the selection of the MOSFET are the minimum threshold voltage,  $V_{TH}$   $_{(MIN)}$ , the on-resistance,  $R_{DS(ON)}$ , the total gate charge,  $Q_g$ , the reverse transfer capacitance,  $C_{RSS}$ , and the maximum drain to source voltage,  $V_{DS(MAX)}$ . The peak switch voltage in a SEPIC is given by:

$$V_{SW(PEAK)} = V_{IN} + V_{OUT} + V_{DIODE}$$

The selected MOSFET should satisfy the condition:

$$V_{DS(MAX)} > V_{SW(PEAK)}$$

The peak switch current is given by:

$$I_{SW(PEAK)} = I_{L1(AVG)} + I_{OUT} + \frac{\Delta I_{L1} + \Delta I_{L2}}{2}$$

The rms current through the switch is given by:

$$I_{\text{SWRMS}} = \sqrt{\left[I_{\text{SWPEAK}}^2 - I_{\text{SWPEAK}} \left(\Delta I_{\text{L1}} + \Delta I_{\text{L2}}\right) + \frac{\left(\Delta I_{\text{L1}} + \Delta I_{\text{L2}}\right)^2}{3}\right]} D$$

#### **POWER DIODE SELECTION**

The Power diode must be selected to handle the peak current and the peak reverse voltage. In a SEPIC, the diode peak current is the same as the switch peak current. The off-state voltage or peak reverse voltage of the diode is  $V_{\text{IN}} + V_{\text{OUT}}$ . Similar to the boost converter, the average diode current is equal to the output current. Schottky diodes are recommended.

#### **SELECTION OF INDUCTORS L1 AND L2**

Proper selection of the inductors L1 and L2 to maintain constant current mode requires calculations of the following parameters.

Average current in the inductors:

$$I_{L1AVE} = \frac{DI_{OUT}}{1-D}$$

$$I_{L2AVE} = I_{OUT}$$

Peak to peak ripple current, to calculate core loss if necessary:

$$\Delta I_{L1} = \frac{(V_{IN} - V_{Q}) D}{(L1)f_{e}}$$

$$\Delta I_{L2} = \frac{(V_{IN} - V_{Q}) D}{(L2) f_{S}}$$

maintains the condition  $I_{L}$  >  $\Delta i_{L}/2$  to ensure constant current mode.

$$L1 > \frac{(V_{IN} - V_{Q})(1-D)}{2I_{OUT}f_{S}}$$

$$L2 > \frac{(V_{IN} - V_{Q})D}{2I_{OUT}f_{S}}$$

Peak current in the inductor, to ensure the inductor does not saturate:

$$I_{L1PK} = \frac{DI_{OUT}}{1-D} + \frac{\Delta I_{L1}}{2}$$

$$I_{L2PK} = I_{OUT} + \frac{\Delta I_{L2}}{2}$$

${\rm I}_{\rm L1PK}$  must be lower than the maximum current rating set by the current sense resistor.

The value of L1 can be increased above the minimum recommended to reduce input ripple and output ripple. However, once  $D_{IL1}$  is less than 20% of  $I_{L1AVE}$ , the benefit to output ripple is minimal.

By increasing the value of L2 above the minimum recommended,  $\Delta_{\text{IL2}}$  can be reduced, which in turn will reduce the output ripple voltage:

$$\Delta V_{OUT} = \left(\frac{I_{OUT}}{1-D} + \frac{\Delta I_{L2}}{2}\right) ESR$$

where ESR is the effective series resistance of the output capacitor.

If L1 and L2 are wound on the same core, then L1 = L2 = L. All the equations above will hold true if the inductance is replaced by 2L. A good choice for transformer with equal turns is Coiltronics CTX series Octopack.

#### SENSE RESISTOR SELECTION

The peak current through the switch,  $I_{SW(PEAK)}$  can be adjusted using the current sense resistor,  $R_{SEN}$ , to provide a certain output current. Resistor  $R_{SEN}$  can be selected using the formula:

$$R_{SEN} = \frac{V_{SENSE} - D(V_{SL} + \Delta V_{SL})}{I_{SWPEAK}}$$

# **Sepic Capacitor Selection**

The selection of SEPIC capacitor, CS, depends on the rms current. The rms current of the SEPIC capacitor is given by:

$$||_{\text{CSRMS}} = \sqrt{||_{\text{SWRMS}}|^2 + (||_{\text{L1PK}}|^2 - ||_{\text{L1PK}}\Delta ||_{\text{L1}} + \Delta ||_{\text{L1}}|^2)(1-D)}$$

The SEPIC capacitor must be rated for a large ACrms current relative to the output power. This property makes the SEPIC much better suited to lower power applications where the rms current through the capacitor is relatively small (relative to capacitor technology). The voltage rating of the SEPIC capacitor must be greater than the maximum input voltage. Tantalum capacitors are the best choice for SMT, having high rms current ratings relative to size. Ceramic capacitors could be used, but the low C values will tend to cause larger changes in voltage across the capacitor due to the large currents. High C value ceramics are expensive. Electrolytics work well for through hole applications where the size required to meet the rms current rating can be accommodated.

There is an energy balance between CS and L1, which can be used to determine the value of the capacitor. The basic energy balance equation is:

$$\frac{1}{2}C_{S}\Delta V_{S}^{2} = \frac{1}{2}L_{1}\Delta I_{L1}^{2}$$

Where

$$\Delta V_{S} = \left( \frac{V_{OUT}}{V_{OUT} + V_{IN} - V_{Q} + V_{DIODE}} \right) \frac{I_{OUT}}{f_{S}C_{S}}$$

is the ripple voltage across the SEPIC capacitor, and

$$\Delta I_{L1} = \frac{(V_{IN} - V_{Q}) D}{L_{1}f_{S}}$$

is the ripple current through the inductor L1. The energy balance equation can be solved to provide a minimum value for  $C_S$ :

$$C_{s} \ge L_{1} \frac{{I_{OUT}}^{2}}{(V_{IN} - V_{O})^{2}}$$

### **Input Capacitor Selection**

Similar to a boost converter, the SEPIC has an inductor at the input. Hence, the input current waveform is continuous and triangular. The inductor ensures that the input capacitor sees fairly low ripple currents. However, as the input capacitor gets smaller, the input ripple goes up. The rms current in the input capacitor is given by:

$$I_{\text{CIN(RMS)}} = \Delta I_{L1} / \sqrt{12} = \frac{D}{2\sqrt{3}} \left( \frac{V_{\text{IN}} - V_{\text{Q}}}{L_{1} f_{\text{S}}} \right)$$

The input capacitor should be capable of handling the rms current. Although the input capacitor is not as critical in a boost application, low values can cause impedance interactions. Therefore a good quality capacitor should be chosen in the range of  $10\mu F$  to  $20\mu F$ . If a value lower than  $10\mu F$  is used, then problems with impedance interactions or switching noise can affect the LM3478. To improve performance, especially with  $V_{IN}$  below 8 volts, it is recommended to use a  $20\Omega$  resistor at the input to provide a RC filter. The resistor is placed in series with the  $V_{IN}$  pin with only a bypass capacitor attached to the  $V_{IN}$  pin directly (see Figure 14). A  $0.1\mu F$  or  $1\mu F$  ceramic capacitor is necessary in this configuration. The bulk input capacitor and inductor will connect on the other side of the resistor with the input power supply.

## **Output Capacitor Selection**

The ESR and ESL of the output capacitor directly control the output ripple. Use low capacitors with low ESR and ESL at the output for high efficiency and low ripple voltage. Surface mount tantalums, surface mount polymer electrolytic and polymer tantalum, Sanyo-OSCON, or multi-layer ceramic capacitors are recommended at the output.

The output capacitor of the SEPIC sees very large ripple currents (similar to the output capacitor of a boost converter. The rms current through the output capacitor is given by:

$$I_{\text{RMS}} = \sqrt{\left[I_{\text{SWPK}}^2 - I_{\text{SWPK}} \left(\Delta I_{L1} + \Delta I_{L2}\right) + \left(\Delta I_{L1} + \Delta I_{L2}\right)^2\right] (1-D) - I_{\text{OUT}}^2}$$

The ESR and ESL of the output capacitor directly control the output ripple. Use low capacitors with low ESR and ESL at the output for high efficiency and low ripple voltage. Surface mount tantalums, surface mount polymer electrolytic and polymer tantalum, Sanyo-OSCON, or multi-layer ceramic capacitors are recommended at the output for low ripple.

# **Other Application Circuits**

FIGURE 16. Typical High Efficiency Step-Up (Boost) Converter

# Physical Dimensions inches (millimeters) unless otherwise noted

CONTROLLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS

MUA08A (Rev F)

### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pr                             | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2011 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

### Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Interface interface.ti.com Security www.ti.com/security

Logic Space, Avionics and Defense <u>www.ti.com/space-avionics-defense</u>

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

TI E2E Community Home Page <u>e2e.ti.com</u>

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated