## **Product Change Notification: SYST-01SSSS214**

Date:

02-May-2025

## **Product Category:**

8-Bit Microcontrollers

## **Notification Subject:**

PIC16(L)F1934/1936/1937 Family Silicon Errata and Data Sheet Clarifications

## **Affected CPNs:**

SYST-01SSSS214\_Affected\_CPN\_05022025.pdf SYST-01SSSS214\_Affected\_CPN\_05022025.csv

## **Notification Text:**

### SYST-01SSSS214

Microchip has released a new Document for the PIC16(L)F1934/1936/1937 Family Silicon Errata and Data Sheet Clarifications of devices. If you are using one of these devices please read the document located at PIC16(L)F1934/1936/1937 Family Silicon Errata and Data Sheet Clarifications.

**Notification Status:** Final

## **Description of Change:**

Updated the document format to the current Microchip publication standard; module numbers under silicon errata have been renumbered accordingly.

Added silicon issue 1.6.3; added data sheet clarification 2.1.

Minor typographic corrections to existing issues.

**Impacts to Data Sheet:** None

Reason for Change: To Improve Productivity.

Change Implementation Status: Complete

**Date Document Changes Effective:** 02 May 2025

**NOTE:** Please be advised that this is a change to the document only the product has not been

changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

## **Attachments:**

PIC16(L)F1934/1936/1937 Family Silicon Errata and Data Sheet Clarifications

Please contact your local Microchip sales office with questions or concerns regarding this notification.

## **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN</u> <u>home page</u> select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section.

If you wish to <u>change your PCN profile</u>, <u>including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from

## SYST-01SSSS214 - PIC16(L)F1934/1936/1937 Family Silicon Errata and Data Sheet Clarifications

| Affected Catalog Part Numbers (CPN) |  |

|-------------------------------------|--|

| PIC16F1934-E/ML                     |  |

| PIC16F1934-E/PT                     |  |

| PIC16F1934-I/P                      |  |

| PIC16F1934-I/MV                     |  |

| PIC16F1934-I/ML                     |  |

| PIC16F1934-I/PT020                  |  |

| PIC16F1934-I/PT024                  |  |

| PIC16F1934-I/PT027                  |  |

| PIC16F1934-I/PT028                  |  |

| PIC16F1934-I/PT                     |  |

| PIC16F1934-I/PTV03                  |  |

| PIC16F1934-I/PTVAO                  |  |

| PIC16F1934T-I/MV                    |  |

| PIC16F1934T-I/ML                    |  |

| PIC16F1934T-I/PT020                 |  |

| PIC16F1934T-I/PT024                 |  |

| PIC16F1934T-I/PT027                 |  |

| PIC16F1934T-I/PT028                 |  |

| PIC16F1934T-I/PT029                 |  |

| PIC16F1934T-I/PT                    |  |

| PIC16F1934T-I/PT024-GM              |  |

| PIC16F1934T-I/PT027-GM              |  |

| PIC16F1934T-I/PT028-GM              |  |

| PIC16F1934T-I/PT029-GM              |  |

| PIC16F1934T-I/PTVAO                 |  |

| PIC16F1934T-E/MLV01                 |  |

| PIC16LF1934-I/P                     |  |

| PIC16LF1934-I/ML                    |  |

| PIC16LF1934-I/PT025                 |  |

Date: Thursday, May 1, 2025

| SYST-01SSSS214 - PIC16(L)F1934/1936/1937 Family Silicon Errata and Data Sheet Clarifications |

|----------------------------------------------------------------------------------------------|

| PIC16LF1934-I/PT                                                                             |

| PIC16LF1934-I/PTVAO                                                                          |

| PIC16LF1934T-I/ML                                                                            |

| PIC16LF1934T-I/PT                                                                            |

| PIC16LF1934T-I/PTVAO                                                                         |

| PIC16F1936-E/SP                                                                              |

| PIC16F1936-E/ML                                                                              |

| PIC16F1936-E/MLVAO                                                                           |

| PIC16F1936-E/SS                                                                              |

| PIC16F1936-E/SSVAO                                                                           |

| PIC16F1936-E/SO                                                                              |

| PIC16F1936-E/SOVAO                                                                           |

| PIC16F1936-E/MV                                                                              |

| PIC16F1936-I/SP036                                                                           |

| PIC16F1936-I/SP041                                                                           |

| PIC16F1936-I/SP042                                                                           |

| PIC16F1936-I/SP                                                                              |

| PIC16F1936-I/ML                                                                              |

| PIC16F1936-I/MLV03                                                                           |

| PIC16F1936-I/MLV03-BW                                                                        |

| PIC16F1936-I/SS                                                                              |

| PIC16F1936-I/SSC03                                                                           |

| PIC16F1936-I/SSV01                                                                           |

| PIC16F1936-I/SSV08                                                                           |

| PIC16F1936-I/SSVAO                                                                           |

| PIC16F1936-I/SO                                                                              |

| PIC16F1936-I/SOC04                                                                           |

| PIC16F1936-I/MV                                                                              |

| PIC16F1936-I/MVVAO                                                                           |

| PIC16F1936T-I/ML                                                                             |

| PIC16F1936T-I/MLV03                                                                          |

| PIC16F1936T-I/MLV03-BW                                                                       |

| Date: Thursday, May 1, 2025                                                                  |

| SYST-01SSSS214 - PIC16(L)F1934/1936/1937 Family Silicon Errata and Data Sheet Clarifications |

|----------------------------------------------------------------------------------------------|

| PIC16F1936T-I/SS025                                                                          |

| PIC16F1936T-I/SS026                                                                          |

| PIC16F1936T-I/SS027                                                                          |

| PIC16F1936T-I/SS028                                                                          |

| PIC16F1936T-I/SS033                                                                          |

| PIC16F1936T-I/SS                                                                             |

| PIC16F1936T-I/SSC03                                                                          |

| PIC16F1936T-I/SSV05                                                                          |

| PIC16F1936T-I/SSV09                                                                          |

| PIC16F1936T-I/SSV10                                                                          |

| PIC16F1936T-I/SSVAO                                                                          |

| PIC16F1936T-I/SO022                                                                          |

| PIC16F1936T-I/SO023                                                                          |

| PIC16F1936T-I/SO031                                                                          |

| PIC16F1936T-I/SO032                                                                          |

| PIC16F1936T-I/SO040                                                                          |

| PIC16F1936T-I/SO043                                                                          |

| PIC16F1936T-I/SO                                                                             |

| PIC16F1936T-I/SOC04                                                                          |

| PIC16F1936T-I/MV                                                                             |

| PIC16F1936T-I/MVVAO                                                                          |

| PIC16F1936T-E/SS030                                                                          |

| PIC16F1936T-E/SSV02                                                                          |

| PIC16F1936T-E/SSV03                                                                          |

| PIC16F1936T-E/SSV06                                                                          |

| PIC16F1936T-E/SSV07                                                                          |

| PIC16F1936T-E/SSV11                                                                          |

| PIC16F1936T-E/SSVAO                                                                          |

| PIC16F1936T-E/SSVAO-GM                                                                       |

| PIC16F1936T-E/SO                                                                             |

| PIC16F1936T-E/SOVAO                                                                          |

| PIC16LF1936-E/SP                                                                             |

| Date: Thursday, May 1, 2025                                                                  |

## SYST-01SSSS214 - PIC16(L)F1934/1936/1937 Family Silicon Errata and Data Sheet Clarifications PIC16LF1936-E/ML PIC16LF1936-E/MLVAO PIC16LF1936-E/SS PIC16LF1936-E/SSVAO PIC16LF1936-I/SP PIC16LF1936-I/ML PIC16LF1936-I/SS PIC16LF1936-I/SSVAO PIC16LF1936-I/SO PIC16LF1936-I/MV PIC16LF1936T-I/ML020 PIC16LF1936T-I/ML PIC16LF1936T-I/SS023 PIC16LF1936T-I/SS PIC16LF1936T-I/SSV04 PIC16LF1936T-I/SSVAO PIC16LF1936T-I/SSV04-BW PIC16LF1936T-I/SO PIC16LF1936T-I/MV PIC16LF1936T-E/MLVAO PIC16LF1936T-E/SSV02 PIC16LF1936T-E/SSV02-BW PIC16F1937-E/P PIC16F1937-E/MV PIC16F1937-E/ML PIC16F1937-E/PT PIC16F1937-E/PTVAO PIC16F1937-I/MP PIC16F1937-I/P PIC16F1937-I/MV PIC16F1937-I/ML PIC16F1937-I/PT025 Date: Thursday, May 1, 2025

# PIC16F1937-I/PT PIC16F1937-I/PTC02 PIC16F1937-I/PTVAO PIC16F1937T-I/MP PIC16F1937T-I/MV PIC16F1937T-I/ML PIC16F1937T-I/PT PIC16F1937T-I/PTVAO PIC16F1937T-E/PT PIC16F1937T-E/PTVAO PIC16LF1937/SD02 PIC16LF1937/WMD01 PIC16LF1937-E/P PIC16LF1937-E/ML PIC16LF1937-I/P PIC16LF1937-I/MV PIC16LF1937-I/ML PIC16LF1937-I/PT PIC16LF1937-I/PTVAO PIC16LF1937T-I/MV PIC16LF1937T-I/ML PIC16LF1937T-I/PT PIC16LF1937T-I/PTVAO

SYST-01SSSS214 - PIC16(L)F1934/1936/1937 Family Silicon Errata and Data Sheet Clarifications

Date: Thursday, May 1, 2025

# PIC16(L)F1934/1936/1937 Family Silicon Errata and Data Sheet Clarifications

PIC16(L)F1934/1936/1937

## Introduction

The PIC16(L)F1934/1936/1937 devices that you have received conform functionally to the current device data sheet (DS41364**E**), except for the anomalies described in this document.

The silicon issues discussed in the following pages are for silicon revisions with the Device and Revision IDs listed in the table below.

The errata described in this document will be addressed in future revisions of the PIC16(L)F1934/1936/1937 silicon.

**Note:** This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current.

Table 1. Silicon Device Identification

|             |             |          |        | DEVICE ID[1 | 3:0]   |        |        |        |  |  |

|-------------|-------------|----------|--------|-------------|--------|--------|--------|--------|--|--|

| Part Number | DEV[8:0]    | REV[4:0] |        |             |        |        |        |        |  |  |

|             |             | A2       | A3     | A5          | A6     | A7     | A8     | A9     |  |  |

| PIC16F1934  | 10 0011 010 | 0 0010   | 0 0011 | 0 0101      | 0 0110 | 0 0111 | 0 1000 | 0 1001 |  |  |

| PIC16LF1934 | 10 0100 010 | 0 0010   | 0 0011 | 0 0101      | 0 0110 | 0 0111 | 0 1000 | 0 1001 |  |  |

| PIC16F1936  | 10 0011 011 | 0 0010   | 0 0011 | 0 0101      | 0 0110 | 0 0111 | 0 1000 | 0 1001 |  |  |

| PIC16LF1936 | 10 0100 011 | 0 0010   | 0 0011 | 0 0101      | 0 0110 | 0 0111 | 0 1000 | 0 1001 |  |  |

| PIC16F1937  | 10 0011 100 | 0 0010   | 0 0011 | 0 0101      | 0 0110 | 0 0111 | 0 1000 | 0 1001 |  |  |

| PIC16LF1937 | 10 0100 100 | 0 0010   | 0 0011 | 0 0101      | 0 0110 | 0 0111 | 0 1000 | 0 1001 |  |  |

**Important:** Refer to the **Device/Revision ID** section in the device data sheet for more detailed information on Device Identification and Revision IDs for your specific device.

## **Silicon Issue Summary**

Table 2. Silicon Issue Summary

| Module                                      | Feature                                       | Item  | Issue Summary                                                                             |    |    | Affe | cted Revi | sions |    |    |

|---------------------------------------------|-----------------------------------------------|-------|-------------------------------------------------------------------------------------------|----|----|------|-----------|-------|----|----|

| Module                                      | reature                                       | No.   | issue Summary                                                                             | A2 | A3 | A5   | A6        | Α7    | A8 | A9 |

| Data EE<br>Memory                           | Memory<br>Endurance                           | 1.1.1 | Erase/Write Endurance Limited                                                             | Х  | Х  | Χ    |           |       |    |    |

|                                             | Writes                                        | 1.1.2 | Minimum V <sub>DD</sub> for Writes                                                        | Χ  | Х  | Х    | X         | Χ     | X  | Х  |

| Program Flash<br>Memory (PFM)               | Memory<br>Endurance                           | 1.2.1 | Erase/Write Endurance Limited                                                             | Χ  | X  | Χ    |           |       |    |    |

|                                             | Writes                                        | 1.2.2 | Minimum V <sub>DD</sub> for Writes                                                        | Χ  | X  | Χ    | Χ         | Χ     | X  | Χ  |

| Capture<br>Compare<br>PWM (CCP)             | PWM Dead-<br>Band Delay                       | 1.3.1 | Dead-Band Delay Results in<br>Unpredictable Waveforms                                     | Χ  | Х  | Χ    | Х         | Х     | Х  | Χ  |

|                                             | ECCP2<br>Switching                            | 1.3.2 | ECCP2 Switching Between Single,<br>Half-Bridge, and Full-Bridge PWM<br>Modes              | Х  | X  | X    | Х         | Χ     | X  | Х  |

|                                             | ECCP2<br>Changing<br>Direction                | 1.3.3 | ECCP2 PWM Outputs Will<br>Improperly Go Active                                            | Х  | X  | X    | Х         | Χ     | X  | Х  |

|                                             | Capture<br>Mode                               | 1.3.4 | Capture Triggered While CCPx<br>Pin is Held High                                          | Χ  | X  | Χ    | X         | Х     | X  | Х  |

|                                             | ECCPx Dead-<br>Band Delay                     | 1.3.5 | ECCPx Dead-Band Delay in Half-<br>Bridge Mode                                             | Х  | X  | Χ    | X         | Х     | X  | Х  |

|                                             | PWM with<br>Pulse<br>Steering                 | 1.3.6 | Disabling a PWM Output During<br>a PWM Cycle May Stop the<br>Output Earlier than Expected | X  | X  | Х    | X         | Χ     | X  | Х  |

|                                             | Capture<br>Mode                               | 1.3.7 | Capture Triggered While CCPx<br>Pin is Held Low                                           | Χ  | X  | Χ    | X         | Х     | X  | Х  |

| Brown-Out<br>Reset (BOR)                    | Threshold                                     | 1.4.1 | BOR Threshold Voltage Level                                                               | Χ  |    |      |           |       |    |    |

| Analog-to-<br>Digital<br>Converter<br>(ADC) | ADC<br>Conversion                             | 1.5.1 | ADC Conversion May Not<br>Complete                                                        | Х  | Х  | Х    |           |       |    |    |

| Oscillator                                  | HS Oscillator                                 | 1.6.1 | HS Oscillator Minimum V <sub>DD</sub>                                                     | Χ  | Х  | Χ    |           |       |    |    |

| (OSC)                                       | Oscillator<br>Start-Up<br>Timer (OSTS)<br>Bit | 1.6.2 | OSTS Bit Remains Set                                                                      | Х  | Х  | Х    | Х         | X     | X  |    |

|                                             | MFINTOSC                                      | 1.6.3 | The Device May not Wake from Sleep when Using the MF Internal Oscillator                  | Х  | Х  | Х    | Х         | Χ     | X  | Х  |

| Enhanced<br>Capture                         | Enhanced<br>PWM                               | 1.7.1 | PWM 0% Duty Cycle Direction<br>Change                                                     | Χ  | X  | Χ    | Χ         | Х     | X  | Χ  |

| Compare<br>PWM (ECCP)                       | Enhanced<br>PWM                               | 1.7.2 | PWM 0% Duty Cycle Port<br>Steering                                                        | Χ  | X  | Χ    | Χ         | Х     | Х  | Х  |

| Timer1                                      | Timer0 Gate<br>Source                         | 1.8.1 | Gate Toggle Mode Works<br>Improperly                                                      | Χ  | X  | Χ    | Χ         | Х     | Х  | Х  |

|                                             | Timer1 Gate<br>Toggle Mode                    | 1.8.2 | T1 Gate Flip-Flop Does Not Clear                                                          | Х  | X  | Х    | Χ         | Х     | X  | Х  |

| LDO                                         | Minimum V <sub>DD</sub> above 85°C            | 1.9.1 | Minimum Operating V <sub>DD</sub> for the PIC16F193x devices at T <sub>A</sub> > 85°C     | Χ  | Х  | Х    | Х         | Х     | Х  | Χ  |

Table 2. Silicon Issue Summary (continued)

| Module                                                                                      | Feature              | Item   | Issue Summary                                                                                              |    |    | Affe | cted Revi | sions |    |    |

|---------------------------------------------------------------------------------------------|----------------------|--------|------------------------------------------------------------------------------------------------------------|----|----|------|-----------|-------|----|----|

| Wodule                                                                                      | No.                  |        | Issue Summary                                                                                              | A2 | A3 | A5   | A6        | A7    | A8 | A9 |

| Enhanced<br>Universal<br>Synchronous<br>Asynchronous<br>Receiver<br>Transmitter<br>(EUSART) | Auto-Baud<br>Detect  | 1.10.1 | Auto-Baud Detect May Store<br>Incorrect Count Value in the<br>SPBRG Registers                              | X  | X  | X    | X         | X     |    |    |

| Resets                                                                                      | RESET<br>Instruction | 1.11.1 | Extended Reset if Clock is MFINTOSC or HFINTOSC                                                            | Х  | Х  | Χ    | Х         | Х     | X  |    |

| Master<br>Synchronous<br>Serial Port<br>(MSSP)                                              | SPI Master<br>Mode   | 1.12.1 | The Buffer Full (BF) Bit or<br>MSSP Interrupt Flag (SSPIF) Bit<br>Becomes Set Half of a SCK Cycle<br>Early | Х  | Х  | Х    | Х         | Х     | Х  | Х  |

**Note:** Only those issues indicated in the last column apply to the current silicon revision.

## 1. Silicon Errata Issues

This document summarizes all silicon errata issues from all revisions of silicon, previous and current. Only the issues indicated by the bold font in the following tables apply to the current silicon revision.

## 1.1. Module: Data EE Memory

## 1.1.1. Erase/Write Endurance Limited

The typical write/erase endurance of the Data EE Memory is limited to 10k cycles.

#### Work around

Use an error correction method that stores data in multiple locations.

#### **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | А9 |  |

|----|----|----|----|----|----|----|--|

| X  | Χ  | Χ  |    |    |    |    |  |

## 1.1.2. Minimum V<sub>DD</sub> for Writes

The minimum voltage required for a Data EE write operation is 2.0 volts.

## Work around

None.

## **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | А9 |  |

|----|----|----|----|----|----|----|--|

| Χ  | X  | Χ  | Χ  | Χ  | Χ  | X  |  |

## 1.2. Module: Program Flash Memory (PFM)

## 1.2.1. Erase/Write Endurance Limited

The typical write/erase endurance of the PFM is limited to 1k cycles when  $V_{DD}$  is above 3.0 volts. Endurance degrades when  $V_{DD}$  is below 3.0 volts.

### Work around

Use an error correction method that stores data in multiple locations.

## **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  |    |    |    |    |  |

## 1.2.2. Minimum V<sub>DD</sub> for Writes

The minimum voltage required for a PFM write operation is 2.0 volts.

#### Work around

None.

## **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | <b>A9</b> |  |

|----|----|----|----|----|----|-----------|--|

| X  | X  | X  | Χ  | Χ  | X  | Х         |  |

## 1.3. Module: Capture Compare PWM (CCP)

## 1.3.1. Dead-Band Delay Results in Unpredictable Waveforms

When the ECCP is configured for PWM Half-Bridge mode with a dead-band delay greater than or equal to the PWM duty cycle, unpredictable waveforms may result.

#### Work around

Make sure the dead-band delay is always less than the PWM duty cycle.

#### Affected Silicon Revisions

| A2 | А3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | X  | X  | X  | Х  |  |

## 1.3.2. ECCP2 Switching Between Single, Half-Bridge, and Full-Bridge PWM Modes

Switching PWM modes during the current PWM cycle by modifying the P2M[1:0] bits in the CCP2CON register will cause the PWM outputs to switch immediately and not on the start of the next PWM cycle.

## Work around

None.

#### Affected Silicon Revisions

| A2 | А3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | X  | X  | X  | Х  |  |

## 1.3.3. ECCP2 PWM Outputs Will Improperly Go Active

When changing directions in Full-Bridge PWM mode, the active and modulated outputs will improperly go active at the same time, and the dead-band delay does not occur, which can lead to large shoot-through currents.

## Work around

None.

## **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | X  | X  | X  | Х  |  |

## 1.3.4. Capture Triggered While CCPx Pin is Held High

If the module is configured to capture on the first rising edge and the CCPx pin is high at this time, a capture will be triggered.

#### Work around

Clear the CCP Interrupt Flag (CCPxIF = 0) immediately after configuring the module for a capture event.

## **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| Χ  | X  | X  | X  | X  | X  | X  |  |

## 1.3.5. ECCPx Dead-Band Delay in Half-Bridge Mode

In Half-Bridge mode, the dead-band delay is 1  $T_{OSC}$  longer than calculated for the first PWM cycle and 1.5  $T_{OSC}$  for the following cycles.

#### Work around

None.

## **Affected Silicon Revisions**

| A2 | А3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| Χ  | Χ  | Х  | Χ  | Х  | X  | х  |  |

## 1.3.6. Disabling a PWM Output During a PWM Cycle May Stop the Output Earlier Than Expected

When the PWM is in Steering mode, disabling a PWM output during a PWM cycle will cause the output to end 1 T<sub>OSC</sub> earlier than expected.

#### Work around

None.

## **Affected Silicon Revisions**

| A2 | А3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | X  | X  | X  | Х  |  |

## 1.3.7. Capture Triggered While CCPx Pin is Held Low

If the module is configured to capture on the first falling edge and the CCPx pin is low at this time, a capture will be triggered.

## Work around

Clear the CCP Interrupt Flag (CCPxIF = 0) immediately after configuring the module for a capture event.

#### **Affected Silicon Revisions**

| A2 | А3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | X  | X  | X  | Х  |  |

## 1.4. Module: Brown-Out Reset (BOR)

## 1.4.1. BOR Threshold Voltage Level

When the BOR is configured for 2.5 volt operation, the BOR Reset will typically occur at 2.7 volts.

### Work around

None.

## **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  |    |    |    |    |    |    |  |

## 1.5. Module: Analog-to-Digital Converter (ADC)

## 1.5.1. ADC Conversion May Not Complete

An ADC conversion may not complete under these conditions:

- 1. When  $F_{OSC}$  is greater than 8 MHz and it is the clock source used for the ADC converter.

- The ADC is operating from its dedicated ADCRC oscillator and the device is not in Sleep mode (at any F<sub>OSC</sub> frequency). When this occurs, the ADC Interrupt Flag (ADIF) does not get set, the GO/ DONE bit does not get cleared, and the conversion result does not get loaded into the ADRESH and ADRESL result registers.

## Work around

#### Method 1:

Select the system clock, F<sub>OSC</sub>, as the ADC clock source and reduce the F<sub>OSC</sub> frequency to 8 MHz or less when performing ADC conversions.

#### Method 2:

Select the dedicated ADCRC oscillator as the ADC conversion clock source and perform all conversions with the device in Sleep.

#### Method 3:

This method is provided if the application cannot use Sleep mode and requires continuous operation at frequencies above 8 MHz. This method requires early termination of an ADC conversion. Provide a fixed time delay in software to stop the ADC conversion manually, after all 10 bits are converted, but before the conversion would complete automatically. The conversion is stopped by clearing the  $GO/\overline{DONE}$  bit in software, and must be cleared during the last ½  $T_{AD}$  cycle, before the conversion would have completed automatically.

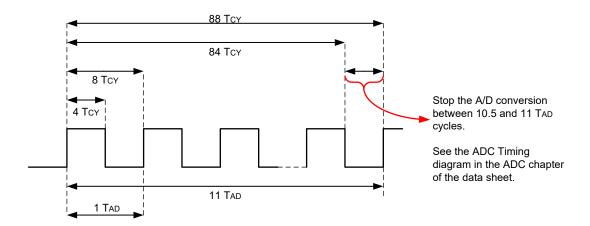

In Figure 1-1, 88 instruction cycles will be required to complete the full conversion. Each  $T_{AD}$  cycle consists of 8  $T_{CY}$  periods. A fixed delay is provided to stop the A/D conversion after 86 instruction cycles and terminate the conversion at the correct time.

**Note:** The exact delay time will depend on the  $T_{AD}$  divisor (ADCS) selection. The  $T_{CY}$  counts shown in Figure 1-1 apply to this example only. Refer to Table 1-1 for examples of the required delay counts for other configurations.

Figure 1-1. Instruction Cycle Delay Calculation Example

Fosc = 32 MHz Tcy = 4/32 MHz = 125 ns TaD = 1 µs, ADCS = Fosc/32

See the 'ADC Clock Period (TAD) vs Device Operating Frequency' table in the ADC section of the data sheet.

Table 1-1. Instruction Cycle Delay Counts by T<sub>AD</sub> Selection

| T <sub>AD</sub>      | Instruction Cycle Delay Counts by T <sub>AD</sub> Selection |

|----------------------|-------------------------------------------------------------|

| F <sub>OSC</sub> /64 | 172                                                         |

| F <sub>OSC</sub> /32 | 86                                                          |

| F <sub>osc</sub> /16 | 43                                                          |

# Example 1-1. Code Example of Instruction Cycle Delay BSF ADCONO, ADGO ; Start ADC Conversion

; Provide 86 instruction cycle delay here BCF ADCONO, ADGO ; Terminate the conversion manually

MOVF ADRESH, W ; Read the conversion result

#### **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  |    |    |    |    |  |

## 1.6. Module: Oscillator (OSC)

## 1.6.1. HS Oscillator Minimum V<sub>DD</sub>

The HS oscillator requires a minimum voltage of 3.0 volts (at 65°C or less) to operate at 20 MHz.

### Work around

None.

### **Affected Silicon Revisions**

| A2 | А3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | Х  |    |    |    |    |  |

#### 1.6.2. OSTS Bit Remains Set

During the Two-Speed Start-up sequence, the Oscillator Start-up Timer (OST) is enabled to count 1024 clock cycles. After the count is reached, the OSTS bit is set, the system clock is held low until the next falling edge of the external crystal (LP, XT, or HS mode), before switching to the external clock source.

When an external oscillator is configured as the primary clock and Fail-Safe Clock mode is enabled (FCMEN = 1), any of the following conditions will result in the OST failing to restart:

- MCLR Reset

- Wake from Sleep

- Clock change from INTOSC to Primary Clock

This anomaly will manifest itself as a clock failure condition for external oscillators which take longer than the clock failure time-out period to start.

#### Work around

None.

#### Affected Silicon Revisions

| A2 | A3 | A5 | A6 | A7 | A8 | А9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | X  | X  | X  |    |  |

## 1.6.3. The Device May Not Wake From Sleep When Using the MF Internal Oscillator

The device may not wake up from Sleep mode when using the Medium-Frequency Internal Oscillator (MFINTOSC) as the system clock.

#### Work around

To ensure the device wakes up from Sleep, Use one of the following work arounds:

- Use the Low-Frequency Internal Oscillator (LFINTOSC) instead of the MFINTOSC.

- 2. If the MFINTOSC must be used as the system clock:

- a. Switch to the LFINTOSC before executing the SLEEP command

- b. Upon wake-up, switch to the 500 kHz MFINTOSC

- c. Wait for the oscillator start-up time to expire (approximately 2 µs)

- d. Check the MFIOFR status bit to ensure the MFINTOSC started up

- e. If the MFIOFR bit is clear, switch to the 500 kHz HFINTOSC

- f. Wait for the oscillator start-up time to expire (approximately 2 µs)

- g. When the HFIOFR bit is set, switch back to the 500 kHz MFINTOSC

```

OSCCONbits.IRCF = 0x0;

// Select the LFINTOSC

SLEEP();

NOP();

NOP();

OSCCONbits.IRCF = 0x7;

// Select the 500 kHz MFINTOSC

// Oscillator start-up delay

_delay_us(2);

if (OSCSTATbits.MFIOFR == 0)

OSCCONbits.IRCF = 0xA;

// Switch to the 500 kHz HFINTOSC

delay us(2);

// Oscillator start-up delay

if (OSCSTATbits.HFIOFR == 1)

OSCCONbits.IRCF = 0x7;

// Switch back to the 500 kHz MFINTOSC

```

## **Affected Silicon Revisions**

| A2 | А3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | Х  | X  | Х  | X  |  |

## 1.7. Module: Enhanced Capture Compare PWM (ECCP)

## 1.7.1. PWM 0% Duty Cycle Direction Change

When the PWM is configured for Full-Bridge mode and the duty cycle is set to 0%, writing the PxM[1:0] bits to change the direction has no effect on PxA and PxC outputs.

## Work around

Increase the duty cycle to a value greater than 0% before changing directions.

## **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | А9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | X  | X  | X  | X  |  |

## 1.7.2. PWM 0% Duty Cycle Port Steering

In PWM mode, when the duty cycle is set to 0% and the STRxSYNC bit is set, writing the STRxA, STRxB, STRxC, and the STRxD bits to enable/disable steering to port pins has no effect on the outputs.

### Work around

Increase the duty cycle to a value greater than 0% before enabling/disabling steering to port pins.

#### Affected Silicon Revisions

| A2 | A3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | X  | X  | X  | X  |  |

## 1.8. Module: Timer1

## 1.8.1. Gate Toggle Mode Works Improperly

Timer1 Gate Toggle mode provides unexpected results when Timer0 overflow is selected as the Timer1 Gate source. We do not recommend using Timer0 overflow as the Timer1 Gate source while in Timer1 Gate Toggle mode or when Toggle mode is used in conjunction with Timer1 Gate Single-Pulse mode.

### Work around

None.

### **Affected Silicon Revisions**

| A2 | А3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | X  | X  | X  | Х  |  |

## 1.8.2. T1 Gate Flip-Flop Does Not Clear

When Timer1 Gate Toggle mode is enabled, clearing the TMR1ON bit does not clear the output value of the flip-flop and hold it clear.

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal. To perform this function, the Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the gate signal. Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When working properly, clearing either the T1GTM bit or the TMR1ON bit would also clear the output value of this flip-flop, and hold it clear. This is done in order to control which edge is being measured.

#### Work around

Clear the T1GTM bit in the T1GCON register to clear, and hold, clear the output value of the flip-flop.

## **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| Χ  | X  | X  | X  | X  | X  | х  |  |

## 1.9. Module: Low Dropout (LDO) Voltage Regulator

## 1.9.1. Minimum Operating V<sub>DD</sub> for the PIC16F193x Devices at TA > 85°C

The minimum voltage required for the PIC16F193x devices is 3.5 volts for temperatures above 85°C. **Note:** This issue only applies to the PIC16F193x devices operating in the Extended temperature range. The PIC16F193x devices are not affected.

## Work around

None.

## **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | X  | X  | X  | х  |  |

# 1.10. Module: Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)

## 1.10.1. Auto-Baud Detect May Store Incorrect Count Value in the SPBRG Registers

When using automatic baud detection (ABDEN), on occasion, an incorrect count value can be stored at the end of the auto-baud detection in the SPBRGH:SPBRGL (SPBRG) registers. The SPBRG value may be off by several counts. This condition happens sporadically when the device clock frequency drifts to a frequency where the SPBRG value oscillates between two different values. The issue is present regardless of the baud rate Configuration bit settings.

#### Work around

When using auto-baud, it is good practice to always verify the obtained value of SPBRG, to ensure it remains within the application specifications. Two recommended methods are shown below.

For additional auto-baud information, see Technical Brief TB3069, "Use of Auto-Baud for Reception of LIN Serial Communications Devices: Mid-Range and Enhanced Mid-Range".

## Example 1-2. Method 1 - EUSART Auto-Baud Detect Work Around

**Note:** In firmware, define default, minimum, and maximum auto-baud (SPBRG) values according to the application requirements. For example, if the application runs at 9600 baud at 16 MHz, then the default SPBRG value would be (assuming 16-bit Asynchronous mode)  $0 \times 67$ . The minimum and maximum allowed values can be calculated based on the application. In this example, a  $\pm 5\%$  tolerance is required, so tolerance is  $0 \times 67 * 5\% = 0 \times 05$ .

#### Example 1-3. Method 2 - EUSART Auto-Baud Detect Work Around

```

#define SPBRG 16BIT *((*int)&SPBRG; // Define location for 16-bit SPBRG value

// Default Auto-Baud value

const int DEFAULT BAUD = 0x0067;

const int TOL = 0 \times 05;

// Baud rate % tolerance

const int MIN BAUD = DEFAULT BAUD - TOL; // Minimum Auto-Baud limit

const int MAX BAUD = DEFAULT BAUD + TOL; // Maximum Auto-Baud limit

int Average Baud; // Define Average Baud variable

int Integrator; // Define Integrator variable

Average_Baud = DEFAULT_BAUD; // Set initial average baud rate

Integrator = DEFAULT_BAUD * 15; // The running 16 count average

ABDEN = 1;

// Start Auto-Baud

while(ABDEN);

// Wait until Auto-Baud completes

Integrator+ = SPGRB 16BIT;

Average Baud = Integrator/16;

if((SPBRG 16BIT > MAX BAUD) || (SPBRG 16BIT < MIN BAUD))</pre>

// Check if value is within limits

// If out of spec, use previous average

{

SPBRG_16BIT = Average Baud;

else

// If in spec, calculate the running

// average but continue using the

{

Integrator+ = SPBRG 16BIT;

// Auto-Baud value in SPBRG

Average Baud = Integrator/16;

```

```

Integrator- = Average_Baud;

}

```

**Note:** Similar to Method 1, define default, minimum, and maximum auto-baud (SPBRG) values. In firmware, compute a running average of SPBRG. If the new SPBRG value falls outside the minimum or maximum limits, then use the current running average. For example, if the application runs at 9600 baud at 16 MHz, then the default SPBRG value would be (assuming 16-bit Asynchronous mode) 0x67. The minimum and maximum allowed values can be calculated based on the application. In this example, a  $\pm 5\%$  tolerance is required, so tolerance is 0x67 \* 5% = 0x05.

## **Affected Silicon Revisions**

| A2 | А3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| Χ  | X  | X  | X  | X  |    |    |  |

## 1.11. Module: Resets

## 1.11.1. Extended Reset if Clock Selection is MFINTOSC or HFINTOSC

When using either the MFINTOSC or HFINTOSC as the primary clock source, and after executing a RESET instruction or when the device executes a Stack Overflow/Underflow Reset, the device may remain in Reset.

## Work around

**Method 1:** Use the Watchdog Timer (WDT) to recover from this issue.

Method 2: In place of the RESET instruction, use GOTO 0x0000.

### **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| Χ  | X  | X  | X  | X  | X  |    |  |

## 1.12. Module: Master Synchronous Serial Port (MSSP)

## 1.12.1. The Buffer Full (BF) Bit or MSSP Interrupt Flag (SSPIF) Bit Becomes Set Half of a SCK Cycle Early

When the MSSP is used in SPI Master mode and the CKE bit is clear (CKE = 0), the Buffer Full (BF) bit and the MSSP Interrupt Flag (SSPIF) bit becomes set half an SCK cycle early. If the user software immediately reacts to either of the bits being set, a write collision may occur as indicated by the WCOL bit being set.

### Work around

To avoid a write collision, one of the following methods should be used:

#### Method 1:

Add a software delay of one SCK period after detecting the completed transfer (the BF bit or SSPIF bit becomes set) and prior to writing to the SSPBUF register. Verify the WCOL bit is clear after writing to SSPBUF. If the WCOL bit is set, clear the bit in software and rewrite the SSPBUF register.

#### Method 2:

As part of the MSSP initialization procedure, set the CKE bit (CKE = 1).

## **Affected Silicon Revisions**

| A2 | A3 | A5 | A6 | A7 | A8 | A9 |  |

|----|----|----|----|----|----|----|--|

| X  | X  | X  | Χ  | X  | X  | X  |  |

## 2. Data Sheet Clarifications

The following typographic corrections and clarifications are to be noted for the latest version of the device data sheet (DS41364 $\mathbf{E}$ ):

#### Note:

Corrections are shown in **bold**. Where possible, the original bold text formatting has been removed for clarity.

## 2.1. V<sub>OL</sub>/V<sub>OH</sub> Note 4 Correction

In **Section 30.4: "DC Characteristics: PIC16(L)F1934/6/7-I/E"**, Note 4 has been corrected as shown in the table below (in **bold**):

| Param No. | Sym.            | Characteristic<br>s | Min.                  | Тур† | Max. | Units | Conditions                                             |

|-----------|-----------------|---------------------|-----------------------|------|------|-------|--------------------------------------------------------|

| D080      | V <sub>OL</sub> | Output Low Vo       | ltage <sup>(4)</sup>  | •    |      |       |                                                        |

|           |                 |                     |                       |      |      |       | $I_{OL} = 8.0 \text{ mA},$<br>$V_{DD} = 5.0 \text{V}$  |

|           | А               | All I/O Pins        | _                     | _    | 0.6  | V     | $I_{OL} = 6.0 \text{ mA},$<br>$V_{DD} = 3.3 \text{V}$  |

|           |                 |                     |                       |      |      |       | $I_{OL} = 1.8 \text{ mA},$<br>$V_{DD} = 1.8 \text{ V}$ |

| D090      | V <sub>OH</sub> | Output High Vo      | oltage <sup>(4)</sup> |      |      |       |                                                        |

|           |                 |                     |                       |      |      |       | $I_{OH} = 3.5 \text{ mA},$<br>$V_{DD} = 5.0 \text{V}$  |

|           |                 | All I/O Pins        | V <sub>DD</sub> - 0.7 | _    | _    | V     | $I_{OH} = 3.0 \text{ mA},$<br>$V_{DD} = 3.3 \text{V}$  |

|           |                 |                     |                       |      |      |       | $I_{OH} = 1.0 \text{ mA},$<br>$V_{DD} = 1.8$           |

<sup>\*</sup> These parameters are characterized but not tested.

### Notes:

- 1. In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

- 2. Negative current is defined as current sourced by the pin.

- 3. The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 4. Including the OSC2 pin with CLKOUT mode disabled.

<sup>†</sup> Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## 3. Appendix A: Revision History

| Doc. Rev. | Date    | Comments                                                                                                                                                                                                                                                            |

|-----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N         |         | Updated the document format to the current Microchip publication standard; module numbers under silicon errata have been renumbered accordingly.  Added silicon issue 1.6.3; added data sheet clarification 2.1.  Minor typographic corrections to existing issues. |

| М         | 11/2014 | Added silicon issue 1.12.1; other minor corrections.                                                                                                                                                                                                                |

| L         | 11/2013 | Added silicon revision A9; added silicon issues 1.6.2 and 1.11.1; other minor corrections.                                                                                                                                                                          |

| K         | 07/2012 | Added silicon revision A8; removed errata issues 1.6.2, 1.6.3, and 1.6.4.                                                                                                                                                                                           |

| J         | 07/2012 | Removed DS Clarifications module 1.                                                                                                                                                                                                                                 |

| Н         | 02/2012 | Added silicon issues 1.6.2, 1.6.3, 1.6.4, and 1.10.1; added DS Clarifications module 1; other minor corrections.                                                                                                                                                    |

| G         | 09/2011 | Added silicon revision A7; Removed DS Clarifications 1 and 2.                                                                                                                                                                                                       |

| F         | 09/2010 | Added silicon issue 1.9.1.                                                                                                                                                                                                                                          |

| Е         | 07/2010 | Revised item 1.5.1; added issue 1.8.2; other minor corrections.                                                                                                                                                                                                     |

| D         | 06/2010 | Added silicon revision A6.                                                                                                                                                                                                                                          |

| С         | 05/2010 | Added errata issues 1.5.1, 1.6.1, 1.6.2, 1.7.1, 1.7.2, 1.8.1; added DS Clarifications modules 1 and 2.                                                                                                                                                              |

| В         | 01/2010 | Added silicon revision A5.                                                                                                                                                                                                                                          |

| Α         | 09/2009 | Initial release of this document.                                                                                                                                                                                                                                   |

## **Microchip Information**

## **Trademarks**

The "Microchip" name and logo, the "M" logo, and other names, logos, and brands are registered and unregistered trademarks of Microchip Technology Incorporated or its affiliates and/or subsidiaries in the United States and/or other countries ("Microchip Trademarks"). Information regarding Microchip Trademarks can be found at https://www.microchip.com/en-us/about/legal-information/microchip-trademarks.

ISBN: 979-8-3371-1051-6

## **Legal Notice**

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip products are strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable".

Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

## **Product Page Links**

PIC16F1934, PIC16F1936, PIC16F1937