# Smart LED Driver & Controller

# INLC10AQ

#### **Product description:**

The INLC10AQ is a LED driver and controller chip. It is a mixed signal device in a 16 lead WETQFN package.

LED chains can be built up by daisy-chaining several INLC10AQ devices or other ISELED products via a differential bidirectional serial bus. For that purpose, the INLC10AQ device can also act as a converter of single ended to differential bus signals only. The chip provides three independent constant current sinks, each controlled via PWM.

In an LED chain, each device is individually addressable via the serial bus. A proprietary bus protocol is used, optimized for this particular application.

#### Applications:

- Ambient lighting

- Roof lighting

- Display backlight

- Functional lighting

- Converting of single ended to differential bus signals

#### Features:

- 488Hz, 12-bit PWM

- Temperature compensation for red channel

- 8-bit brightness resolution for red, green, and blue LED

- Additional dimming function for accurate low light colors

- Maximum of 4079 devices in one LED chain

- Bidirectional, half-duplex, 2Mbps, CRC protected serial communication

- Support for 16 multicast address groups

- Eight times serial line oversampling for communication robustness

- On-die oscillator

- Built-in diagnostic functions

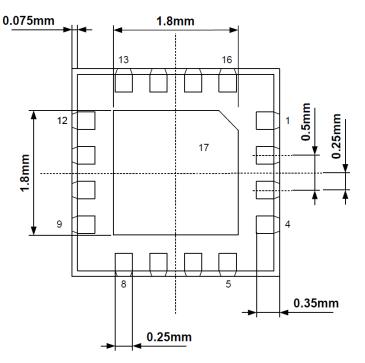

#### 16 lead WETQFN package:

- Exposed pad

- 3mm x 3mm x 0.9mm

- 0.5 pitch

#### **Temperature Range:**

-40°C to +105°C

#### **Qualification:**

• AEC-Q100

# I. List of abbreviations and acronyms

| ADC | Analog Digital Converter |

|-----|--------------------------|

| BG  | Bandgap                  |

| CRC | Cyclic Redundancy Check  |

| DAC | Digital Analog Converter |

| DRV | Driver                   |

| ESD | Electrostatic Discharge  |

| LDO | Low Drop Out             |

| OTP | One Time Programmable    |

| POR | Power On Reset           |

| PWM | Pulse Width Modulation   |

| SIO | Serial Input Output      |

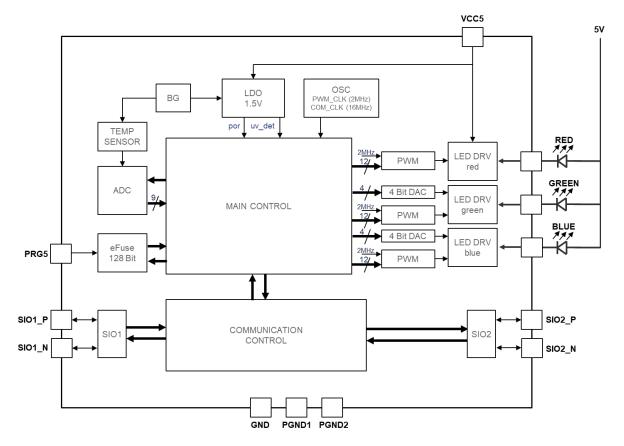

# 1.0 Block Diagram

Figure 1: INLC10AQ block diagram

The device implements a communication for the reception of control commands and for providing device status and configuration data.

Low side, configurable constant current sinks are provided for controlling 3 LEDs (i.g. RGB). The main unit computes the PWM duty cycles from the incoming commands and applies the corresponding control values to the three PWM units.

The main unit is also in charge of a periodic temperature measurement and an appropriate duty cycle adjustment for the red PWM channel.

The actual device temperature is obtained via an integrated analog-digital converter (ADC). Besides the temperature the ADC can also measure various other analog values. These measurements are always triggered by a command from the host. The result of the corresponding A/D conversion is also retrieved by a host command. As each device is individually calibrated to compensate for production variations, the corresponding parameters can be stored in an on-die non-volatile memory.

This one-time-programmable memory (OTP) is read at hardware reset and the parameters are copied from the OTP to directly accessible registers.

Datasheet

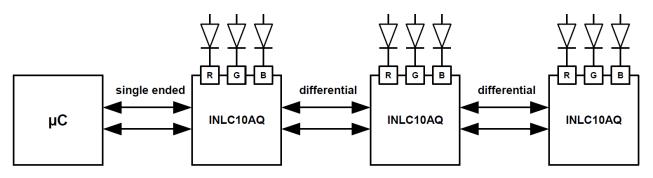

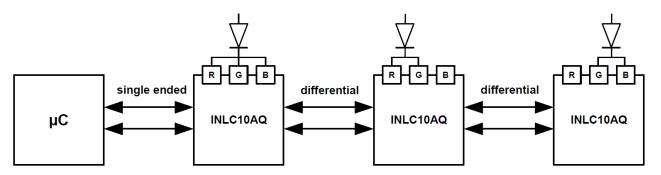

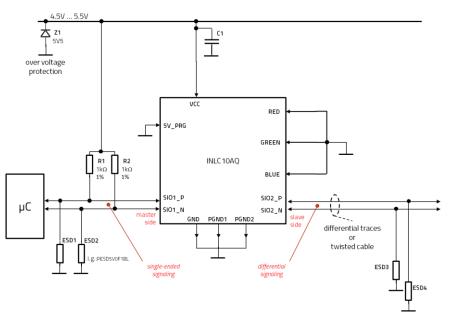

# 2.0 Application

# 2.1 Example For Chain With External LEDs

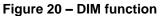

Several INLC10AQ devices can be daisy-chained via  $200\Omega$  differential impedance lines to build up a chain of external LED triplets. The communication between the  $\mu$ C and the first device is single ended.

The capacitive load that correlates with the cable or trace length of the connection between the first device and the  $\mu$ C has to be minimized.

By switching off the phase shift, LEDs can be operated in parallel with two or three of the PWM outputs to achieve higher output currents.

If the phase shift is switched off, all three channels are controlled symmetrically via the red PWM channel (s. Figure 17). The phase shift can only be switched off for the complete daisy-chain. Therefore, a mixture of RGB and single LEDs is not recommended.

Figure 2 - Application example for chain with external RGB LEDs

Figure 3 - Application example for chain with external single-color LEDs

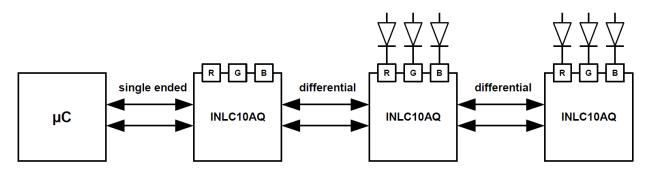

# 2.2 Example For Signal Converter

If it is not possible to locate the  $\mu$ C closely to the first LED, the INLC10AQ can also be used as a converter that is placed near to the  $\mu$ C. The device converts the single ended signal to a differential signal which can be transmitted over longer distances.

Figure 4 - Application example for converter and chain with external LEDs

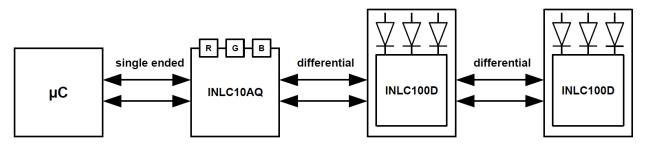

## 2.3 Example For Combination With Other ISELED Products

The converter device can also be combined with other authenticated ISELED products that contain the INLC100 controller and RGB LEDs in one single package.

Figure 5 - Application example for converter and other ISELED products

# 3.0 Electrical Characteristics

#### 3.1 Absolute Maximum Ratings

The absolute maximum ratings define values beyond which damage to the device may occur. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. The functional operation of the device at these or any other conditions beyond the recommended operating ratings is not guaranteed.

| Parameter                                | Description         | Min.  | Max.  | Units |

|------------------------------------------|---------------------|-------|-------|-------|

| V <sub>CC5</sub>                         | DC supply voltage   | -0.25 | 7     | V     |

| Vsio1_p<br>Vsio1_n<br>Vsio2_p<br>Vsio2_n | Serial IO voltage   | -0.48 | 7     | V     |

| Vred<br>Vgreen<br>Vblue                  | RGB voltage         | -0.28 | 7     | V     |

| V <sub>PRG5</sub>                        | Programming voltage | -0.2  | 7     | V     |

| Vsclk<br>Vse<br>Vvdd1v5                  | Test pin voltage    | -0.19 | 1.5   | V     |

| T <sub>stg</sub>                         | Storage temperature | -40°C | 150°C | °C    |

#### Table 1 - Absolute maximum ratings

| Parameter                             | Value | Units |

|---------------------------------------|-------|-------|

| ESD protection HBM<br>AEC-Q100-002-E  | ±2500 | V     |

| ESD protection CDM<br>AEC-Q100-011-C1 | ±500  | V     |

#### Table 2 – ESD protection levels

# 3.2 Recommended Operation Conditions

| Parameter          | Description         | Min.  | Тур. | Max. | Units |

|--------------------|---------------------|-------|------|------|-------|

| V <sub>CC5</sub>   | DC supply voltage   | 4.5   | 5    | 5.5  | V     |

| Vsio1_p<br>Vsio1_n | Serial IO voltage   | 4.5   | 5    | 5.5  | V     |

| Vred               | Red voltage         | 1.05* | -    | 5.5  | V     |

| Vgreen             | Green voltage       | 0.76* | -    | 5.5  | V     |

| V <sub>BLUE</sub>  | Blue voltage        | 0.76* | -    | 5.5  | V     |

| V <sub>PRG5</sub>  | Programming Voltage | -     | 0    | -    | V     |

| T <sub>A</sub>     | Ambient temperature | -40   | -    | 105  | °C    |

#### Table 3 - Recommended operation conditions

\*Only required if the device is used to power LEDs.

# 3.2.1 Interface Characteristics

| Parameter              | Description                     | Min. | Тур. | Max. | Units |

|------------------------|---------------------------------|------|------|------|-------|

| fSIO1_P,single ended   | Single ended data rate SIO1_P   | 1.4  | 2    | 2.6  | MHz   |

| fSIO1_N,single ended   | Single ended clock rate SIO1_N  | 2.8  | 4    | 5.2  | MHz   |

| V <sub>IH</sub> ,se    | Single ended input high voltage | 1.20 | -    | -    | V     |

| V <sub>IL,se</sub>     | Single ended input low voltage  | -    | -    | 1.14 | V     |

| VIAmp,diff             | Differential input amplitude    | 150  | 250  | 325  | mV    |

| V <sub>OAmp,diff</sub> | Differential output amplitude   | 175  | 250  | 325  | mV    |

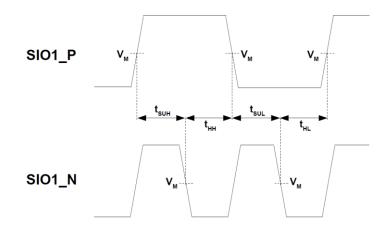

| tsuн                   | Setup time, data high           | 189  | 257  | 285  | ns    |

| tнн                    | Hold time, data high            | 218  | 247  | 275  | ns    |

| tsul                   | Setup time, data low            | 149  | 227  | 293  | ns    |

| thL                    | Hold time, data low             | 156  | 228  | 279  | ns    |

Table 4 – Serial interface parameters

# 3.3 Supply Currents

| Parameter         | Description           | Min. | Тур. | Max. | Units |

|-------------------|-----------------------|------|------|------|-------|

| I <sub>RED</sub>  | Peak current RED      | 23.1 | 24.9 | 26.7 | mA    |

| Igreen            | Peak current GREEN    | 19.4 | 23.1 | 26.8 | mA    |

| IBLUE             | Peak current BLUE     | 19.2 | 23.0 | 26.8 | mA    |

| I <sub>VCC5</sub> | VCC5 stand by current | 0.9  | 1.2  | 1.5  | mA    |

Table 5 – Supply currents

## 3.4 RGB Peak Current Temperature Drift

| Parameter                  | Temperature | Min. | Тур. | Max. | Units |

|----------------------------|-------------|------|------|------|-------|

| $\Delta I_{RED}^{*}$       | -40°C       | -1.5 | 0.3  | 2.2  | %     |

| ΔIRED                      | 105°C       | -7.8 | 0.3  | 7.8  | %     |

| A1 *                       | -40°C       | -4.5 | 0.5  | 5.4  | %     |

| $\Delta I_{GREEN}^{\star}$ | 105°C       | -5.5 | -0,1 | 5.5  | %     |

| AL *                       | -40°C       | -4.7 | 0.5  | 4.7  | %     |

| ∆I <sub>BLUE</sub> *       | 105°C       | -5.2 | -0.6 | 5.2  | %     |

#### Table 6 – RGB peak current temperature drift

\*  $\Delta I_i = (I_{25^{\circ}C, 2V} - I_{Temperature}) / I_{25^{\circ}C, 2V}$

# 3.5 Power-On-Reset (POR)

| Parameter | Min. | Тур. | Max. | Units |

|-----------|------|------|------|-------|

| Vpor      | 4.0  | 4.2  | 4.4  | V     |

Table 7 – Power-on-reset

## 3.6 Undervoltage-lockout

| Parameter | Min. | Тур. | Max. | Units |

|-----------|------|------|------|-------|

| Vuvlo     | 3.2  | 3.3  | 3.4  | V     |

#### Table 8 – Undervoltage-lockout

#### 3.7 Undervoltage Detection

| Parameter          | Min. | Тур. | Max. | Units |

|--------------------|------|------|------|-------|

| V <sub>uvset</sub> | 4.1  | 4.2  | 4.3  | V     |

| Vuvclear           | 4.2  | 4.3  | 4.5  | V     |

#### Table 9 – Undervoltage detection

# 3.8 Analog Digital Converter

| Voltage Source | Voltage Range | ADC Value                                         | Min.  | Тур.  | Max.  |

|----------------|---------------|---------------------------------------------------|-------|-------|-------|

| PRG5           | 0V 1.2V       | Vprg5 x <b>&amp;</b> prg5                         | 0x0   | -     | 0x1ff |

| LDO            | -             | Vldo                                              | 0x168 | 0x17c | 0x190 |

| RED            | 0V 5.5V       | $V_{RED} \mathbf{x}  \boldsymbol{\epsilon}_{RED}$ | 0x0   | -     | 0x1ff |

| GREEN          | 0V 5.5V       | $V_{\text{GREEN}} x \epsilon_{\text{GREEN}}$      | 0x0   | -     | 0x1ff |

| BLUE           | 0V 5.5V       | VBLUE X <b>E</b> BLUE                             | 0x0   | -     | 0x1ff |

| BG             | -             | V <sub>BG</sub>                                   | 0x11c | 0x12d | 0x13e |

#### Table 10 – Analog digital converter

Datasheet

| Parameter               | Min. | Тур. | Max. | Unit      |

|-------------------------|------|------|------|-----------|

| <b>E</b> PRG5           | 0.48 | 0.51 | 0.53 | digits/mV |

| <b>ε</b> <sub>red</sub> | 89   | 93   | 97   | digits/V  |

| ε <sub>green</sub>      | 89   | 93   | 97   | digits/V  |

| <b>E</b> BLUE           | 89   | 93   | 97   | digits/V  |

Table 11 – Voltage detection sensitivities

# 4.0 Functional Description

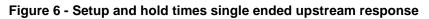

#### 4.1 Serial Communication

Figure 7 – Serial communication

The attachment to the adjacent devices in the chain is made up by two bidirectional differential serial communication lines. The direction towards the controlling microcontroller device is referred to as the "upstream" connection. The opposite direction towards the end of the chain is the "downstream" link. Both links are controlled by the communication unit. Incoming command frames from upstream and responses from downstream are passed to the main unit which is responsible for command processing and overall device control. Commands always originate from the controlling microcontroller. The microcontroller is referred to as the "host" in this document.

The gross data rate on the serial line is 2Mbit/s, i.e. each bit has a nominal duration of 500 ns. As the ondie oscillator has a very limited accuracy, the actual bit time may vary significantly. The whole system is designed for a maximum oscillator variance of  $\pm 30\%$ . With the nominal oscillator frequency being 16 MHz, the actual frequency range is 11.2-20.8MHz.

The device directly attached to the host does not use the differential line mode on the upstream side. Instead a single-ended line mode is used. The single-ended mode is intended to allow for an easy attachment to industry standard microcontrollers. Both single-ended lines require an external pull-up at the microcontroller to 5V.

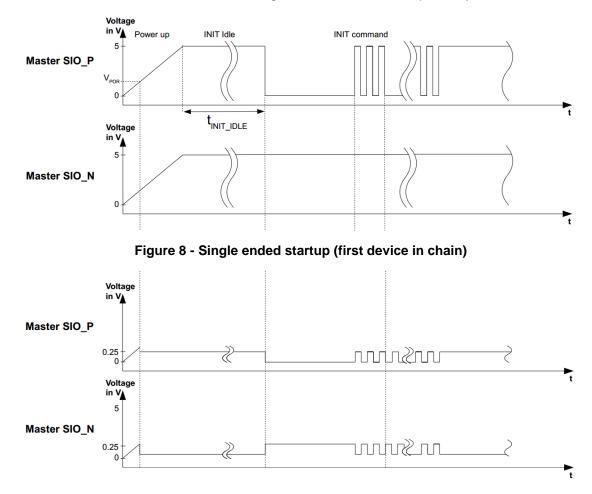

# 4.1.1 Automatic Detection of The Serial Line Mode

During start-up, the devices automatically detect the mode of the upstream and the downstream link. The upstream link may be either single-ended or differential. If a device detects the upstream to be single-ended, it is the first in the chain of LEDs. The downstream link may be either differential or unconnected, i.e. the device is the last in the chain of LEDs. After power-up, an idle of  $t_{INIT Idle} = 150\mu s$  is recommended before the initialization. If during the initialization, while receiving the enumeration command, the master SIO\_N pin is single ended high (5V), the device is switched into single ended communication mode for this port. The detected mode is stored and used for all following communications until a power cycle or a reset command.

| Parameter  | Description              | Min. | Units |

|------------|--------------------------|------|-------|

| tinit idle | Init idle after power up | 150  | μs    |

#### Table 12 – Recommended init idle

## 4.1.2 Half-Duplex Communication

The communication operates in a strict master slave manner. I.e. the microcontroller as the master always initiates the communication. Depending on the type of command the LED devices may send a response (read access) or just silently execute the command (write access). There are three basic types of commands which are described in the following.

## 4.1.3 Basic Frame Format

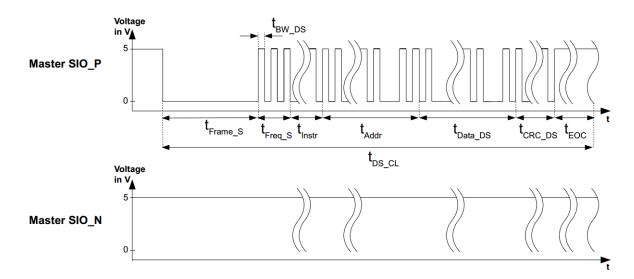

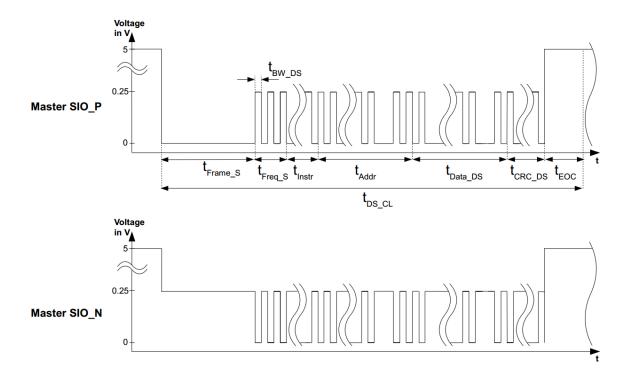

Commands and the response to commands are transmitted with serial frames. A serial frame always consists of a frame\_sync section, followed by a frequency\_sync section, followed by a run length coded command section and finally terminated with an optional CRC section. The command and the CRC sections differ in length between downstream and upstream frames.

The bit encoding ensures a maximum number of adjacent zeros of 4 and a maximum number of adjacent ones of 5 on the serial line. Some of the bit patterns which cannot occur during regular data transmission are used for special purposes. A pattern of 6 or more 1-bits is considered as the bus-idle condition. The bus is idle, when no communication is currently ongoing. A pattern of 15 0-bits is recognized as the so-called frame synchronization. This is the sequence to begin a new frame. The pattern "10101" is the so-called frequency synchronization pattern. It is used after the frame synchronization to determine the transmitter's gross data rate.

Downstream communication is defined as data inputs at SIO1 and outputs at SIO2. This is the data flow for write commands. Upstream respectively is defined as data inputs at SIO2 and outputs at SIO1. This is the data flow for the read response.

Figure 10 - Single ended downstream command frame

Figure 11 - Differential downstream command frame

| Parameter            | Description                                              | Min. | Тур.                                               | Max. | Units |

|----------------------|----------------------------------------------------------|------|----------------------------------------------------|------|-------|

| t <sub>BW_DS</sub>   | Downstream bit width                                     | 384  | 500                                                | 714  | ns    |

| tds_cl               | Downstream command length<br>CRC enabled<br>CRC disabled |      | 86 x t <sub>BW_DS</sub><br>76 x t <sub>BW_DS</sub> |      |       |

| t <sub>Frame_S</sub> | Frame sync                                               |      | 15 x t <sub>BW_DS</sub>                            |      |       |

| t <sub>Freq_</sub> s | Frequency sync                                           |      | 5 x t <sub>BW_DS</sub>                             |      |       |

| t <sub>Inst</sub>    | Instruction                                              |      | 5 x t <sub>BW_DS</sub>                             |      |       |

| t <sub>Addr</sub>    | Address                                                  |      | 15 х tвw_ds                                        |      |       |

| t <sub>Data_DS</sub> | Downstream data                                          |      | 30 x t <sub>BW_DS</sub>                            |      |       |

| tcrc_ds              | CRC downstream                                           |      | 10 x t <sub>BW_Ds</sub>                            |      |       |

| t <sub>EOC</sub>     | End of command idle                                      |      | 6 x t <sub>BW_Ds</sub>                             |      |       |

Table 13 – Downstream command frame parameters

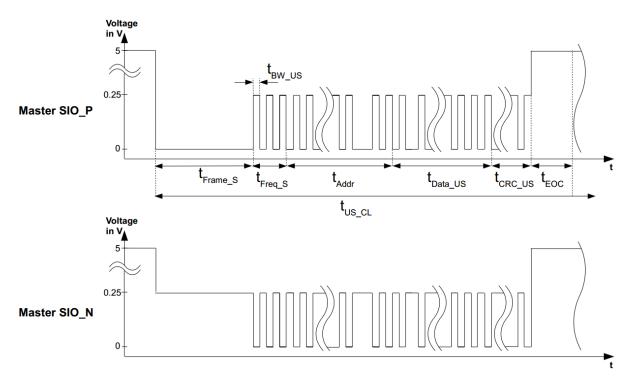

Figure 12 - Single ended upstream response frame

Figure 13 - Differential upstream response frame

| Parameter            | Description                                            | Min. | Тур.                                               | Max. | Units |

|----------------------|--------------------------------------------------------|------|----------------------------------------------------|------|-------|

| t <sub>BW_US</sub>   | Upstream bit width                                     | 384  | 500                                                | 714  | ns    |

| tus_cL               | Upstream command length<br>CRC enabled<br>CRC disabled |      | 61 x t <sub>BW_US</sub><br>56 x t <sub>BW_US</sub> |      |       |

| t <sub>Frame_S</sub> | Frame sync                                             |      | 15 x t <sub>BW_US</sub>                            |      |       |

| t <sub>Freq_S</sub>  | Frequency sync                                         |      | 5 x t <sub>BW_US</sub>                             |      |       |

| t <sub>Addr</sub>    | Address                                                |      | 15 x tвw_us                                        |      |       |

| t <sub>Data_US</sub> | Upstream data                                          |      | 15 x t <sub>BW_US</sub>                            |      |       |

| tcrc_us              | CRC upstream                                           |      | 5 x t <sub>BW_US</sub>                             |      |       |

| teoc                 | End of command idle                                    |      | 6 x t <sub>BW_US</sub>                             |      |       |

Table 14 - Upstream command frame parameters

# 4.1.4 Bit Retransmission

To ensure a correct bit-timing, the forwarded data is regenerated with the clock of the device. The retransmission starts with its own frame-sync when it can be guaranteed that a valid frame-sync timing can be created. A new frequency synchronization is only created after the freq-sync on the reception side has been received (the first four bits). Therefore, the minimum propagation delay  $t_{pd}$  introduced by the retransmission is four bit widths  $t_{BW}$ .

| Name            | Description       | Min. | Тур. | Max. | Unit |

|-----------------|-------------------|------|------|------|------|

| t <sub>pd</sub> | Propagation delay | 2    | 4    | 5.2  | μs   |

| Table | 15 - | Propagation delay   |

|-------|------|---------------------|

| Iabio |      | i i opugution dolay |

To guarantee a correct bit-timing the device uses its own clock as reference and will never transmit faster than its own bit-timing defines, but if the received freq-sync was slower, this timing is used for the retransmission.

The retransmission uses a FIFO to compensate for speed differences between reception and transmission.

Due to the variance in the oscillator clocks of different devices, after each transmission a pause of 43% of the nominal transmission time has to be introduced. If the transmission is created by a chip with  $\pm 30\%$  oscillator clock variation the time has to be increased to a total of 70% of the transmission duration.

#### 4.1.5 Initialization

The digLED\_Init\_Strip command initializes a particular ISELED chain by issuing the command on an associated ISELED communication channel.

This command is always the first command to be transmitted after power-up or reset. The command initializes a chain of devices by assigning the address of the device and by en- or disabling the phaseshift, the CRC and temperature compensation functions. The digLED\_Init\_Strip command is always executed with a CRC checksum. This is true for both, the command and the response frame.

If any command is received by a device before initialization, the command is always considered as illegal and the error status bit for an undefined command is set. This may happen in the chain's first device only, as a non-initialized device does not forward received messages.

If the first device in the chain receives a digLED\_Init\_Strip command, it takes the received address as its own device address and afterwards transmits another digLED\_Init\_Strip frame to the next device in the chain. It increments the address before the transmission. As the adjacent devices proceed in the same manner, the devices in the chain get enumerated with ascending addresses. When the final device in the chain recognizes there is no receiving device at its downstream link, it transmits a response frame upstream. The response frame to a digLED\_Init\_Strip command carries the configuration word read from the OTP. It also transmits the own devices address just initialized.

All upstream devices wait for the responses to be received and forward them towards the microcontroller.

If a frame with an address equal to the adjacent device address (own address plus one) is received, the own response to the digLED\_Init\_Strip command is transmitted thereafter. If the first device has transmitted its response frame, the chain is ready to process regular commands (non-Init frames).

As soon as a device is initialized, it unconditionally forwards incoming correct frames (Frame-Sync, Freq-Sync and the RLC coding as well as the frame length are checked) to the adjacent node in the chain.

Frames received from upstream are forwarded downstream and vice versa. If an error is detected, the forwarding is stopped for this frame.

| Name  | Description             | Equation                                       |

|-------|-------------------------|------------------------------------------------|

| tinit | Initialization duration | $n x (t_{DS_{CL}} + t_{US_{CL}} + 2 x t_{PD})$ |

## 4.1.6 Write Access

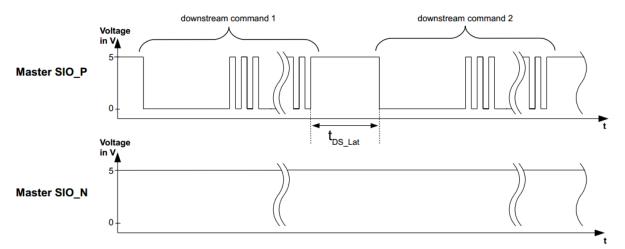

Most commands of the LED Controller are write-only commands. I.e. the devices receive a command frame and execute the appropriate actions without any further communication. A write access command may be directed to a single device (unicast), to all devices (broadcast), or to a defined group of devices (multicast). As every command frame is forwarded downstream irrespective of its destination address, all stations always receive all commands. Only its execution depends on the command's destination address. To avoid communication issues, it is recommended to wait 30% of the command length between two consecutive commands.

Figure 14 - Multiple single ended downstream commands

| Parameter           | Description                             | Min.                     |

|---------------------|-----------------------------------------|--------------------------|

| t <sub>DS_Lat</sub> | Latency between two downstream commands | 0.3 x t <sub>DS_CL</sub> |

#### Table 17 - Recommended latency between downstream commands

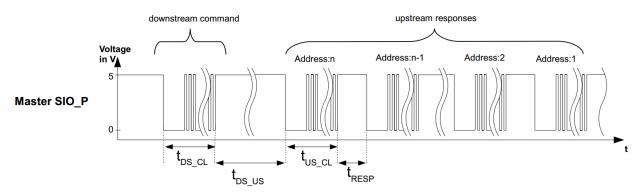

# 4.1.7 Read Access

A read access consists of two phases, the command and the response phase. The command phase uses downstream communication and the response phase uses upstream communication. Commands for read access do not use the command address, i.e. these commands may not be directed to a device based on the device address.

There are two commands for read access, digLED\_Read and digLED\_Ping. The digLED\_Read commands retrieve a status information from all devices and the digLED\_Ping command is used to check the device chain's integrity. Only the final node in the chain responds to a PING command.

A digLED\_Read command is first received by all devices via the frame in downstream direction. The last node in the chain then immediately transmits its response frame upstream. The response frame's data field depends on the actual digLED\_Read command. The response frame's address field is set according to the own device's address. All the nodes upstream forward all received response frames until a frame with the address of their adjacent node is received. Then the respective node transmits its own response frame. This procedure lasts until the chain's first node has transmitted its response frame.

A digLED\_Ping command is similar to a digLED\_Read command, but only the last device in the chain responds to a digLED\_Ping. Thus, the digLED\_Ping command is executed much faster than a regular digLED\_Read command.

| Name               | Description                                                                                                    | Equation                                                          |

|--------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| t <sub>DS_US</sub> | Delay between down- and upstream                                                                               | t <sub>DS_CL</sub> + t <sub>US_CL</sub> + 2 x n x t <sub>PD</sub> |

|                    | Delay between responses                                                                                        |                                                                   |

| tresp              | Oscillator variation of adjacent devices $< \pm 30\%$<br>Oscillator variation of adjacent devices $> \pm 30\%$ | 0.43 x t <sub>US_CL</sub><br>0.7 x t <sub>US_CL</sub>             |

#### Table 18 - Down- and upstream delay, delay between responses

## 4.1.8 Timeouts

The digLED\_Init\_Strip, all the digLED\_Read, and the digLED\_Ping commands initiate upstream data transmission. With the digLED\_Init\_Strip and the read commands all nodes are expected to send a response to the host. The digLED\_Ping requires only the last node in the LED chain to respond. However, in all cases each node needs to await all responses originating from the nodes downstream. Thereafter either the node's own response is transmitted or new commands are accepted. Only the last node in the LED chain may immediately transmit its response.

In case there is an error with the chain downstream, not all expected responses may arrive. Thus, each of the commands expecting a response waits for a certain time only and then returns to its previous state without having transmitted the node's response data.

The lengths of the timeouts depend on the respective command. They are calculated to account for the worst-case oscillator frequency tolerance. I.e. the waiting node has a high-speed clock and all the nodes waited for have a low speed clock. The hardware implementation uses an internally divided clock for the timeout counter:

$$f_{[timeout]} = f_{[osc]} / 2^{14}$$

| Command           | Max. counter value | Min. timeout | Nom. timeout | Max. timeout | Units |

|-------------------|--------------------|--------------|--------------|--------------|-------|

| digLED_Init_Strip | 992                | 780.6        | 1015.3       | 1451.2       | ms    |

| digLED_Read_xxx   | 427                | 335.6        | 436.7        | 624.6        | ms    |

| digLED_Ping       | 62                 | 48.0         | 63.0         | 90.7         | ms    |

With the nominal clock frequency of 16MHz the counter's resolution results to 1.024ms.

Table 19 - Timeouts

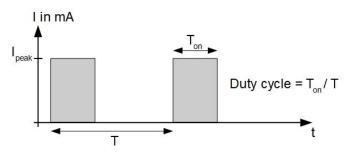

#### 4.2 PWM Units

#### 4.2.1 Basic Mode of Operation

The LED controller device incorporates three independent PWM channels, one for each LED.

Figure 16 – PWM signal

The resolution is 12 bit. The supported duty cycles are 0/4096 to 4095/4096. The nominal PWM output frequency is  $16MHz/2^{15} = 488.3Hz$ . The frequency is reduced to the half or the quarter of this frequency with low duty cycles. This ensures a minimum on-time of 2µs for the LEDs. The minimum output frequency is 122Hz. The output frequency is not derived from the actual PWM duty cycle but from the RGB value received from the host. As the DIM command also has impact to the LED intensity, it is accounted for as well. The actual relationship is given in the following table.

| DIM | RGB    | PWM Frequency |      |       | Unit |

|-----|--------|---------------|------|-------|------|

| DIW | KGB    | Min.          | Тур. | Max.  | Onit |

|     | 8 255  | 341.6         | 488  | 634.4 | Hz   |

| 0   | 4 7    | 170.8         | 244  | 317.2 | Hz   |

|     | 0 3    | 85.4          | 122  | 158.6 | Hz   |

|     | 16 255 | 341.6         | 488  | 634.4 | Hz   |

| 1   | 8 15   | 170.8         | 244  | 317.2 | Hz   |

|     | 0 7    | 85.4          | 122  | 158.6 | Hz   |

|     | 32 255 | 341.6         | 488  | 634.4 | Hz   |

| 2   | 16 31  | 170.8         | 244  | 317.2 | Hz   |

|     | 0 15   | 85.4          | 122  | 158.6 | Hz   |

|     | 64 255 | 341.6         | 488  | 634.4 | Hz   |

| 3   | 32 63  | 170.8         | 244  | 317.2 | Hz   |

|     | 0 31   | 85.4          | 122  | 158.6 | Hz   |

#### Table 20 – DIM parameter relationships between RGB parameters and PWM frequencies

The output frequency is determined independently for each of the PWM channels.

## 4.2.2 Update

When a new PWM duty cycle has to be applied, this is always done at the end of a PWM cycle. I.e. the PWM always completes an output cycle using the previously active duty cycle and starts the next output cycle using the updated duty cycle.

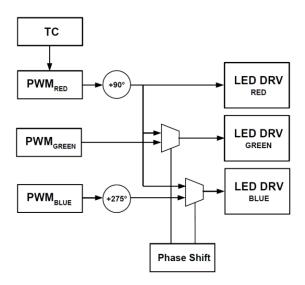

## 4.2.3 Phase Shift

In order to spread the current consumption of the LEDs over time, a phase shift can be set between the three PWM channels. This optional function can be enabled/disabled during device initialization.

If the phase shift is deactivated, the red channel controls all three outputs and thus provides the temperature compensation function for all three channels.

If the phase shift is enabled, it retains even if the output frequency of the channels is different. If a channel is operating at a lower frequency, it may be considered to leave out one or three full PWM cycles. When leaving power save mode, the channels are restarted appropriately to again obtain the correct phase shift.

The fixed phase shift is defined in the following table. Please note the absolute phase shift times are nominal values. I.e. they are subject to vary with the internal oscillator's frequency.

| PWM Channel | Rel. Phase Shift | Unit | Abs. Phase Shift     |

|-------------|------------------|------|----------------------|

| Green       | 0                | %    | 0                    |

| Red         | 25               | %    | 0.25 / PWM Frequency |

| Blue        | 75               | %    | 0.75 / PWM Frequency |

#### Table 21 – Phase shift

Figure 17 – Optional phase shift

## 4.2.4 Power Save Mode

When all LED channels are set to an intensity of 0, the device enters a power save mode for the current sources driving the LEDs. I.e. the digLED\_Set\_RGB command must be issued with an RGB value of 0x000000 to enter the power save mode.

Recovering from this mode does not require any particular measures. I.e. the host just needs to issue a digLED\_Set\_RGB command with the data field different from 0x000000 and the current sources are restarted again. There is a delay of approx. 1µs before the restart of the green PWM channel (no phase shift applies to the green channel).

This is due to an internal ramp-up required by the analog circuitry. The same procedure is applied after device power-up or a hardware reset, as the initial RGB value is 0x000000. I.e. the LEDs are all turned off after power-up or a hardware reset.

## 4.3 Blue and Green Brightness Control Scaler

In operation, the color brightness of each LED is controlled via an 8-bit RGB parameter. This provides a color space of 3 x 8 bit = 24 bit. The 8-bit RGB value is scaled to the 12-bit  $PWM_{max}$  value.

The PWM<sub>max</sub> values can be read out with the digLED\_Read\_Param command.

The scaling equations of the green and blue channel are given in Table 22.

| Color | Scaling                                     |

|-------|---------------------------------------------|

| Blue  | PWM = (PWM <sub>max</sub> x RGB + 128) >> 8 |

| Green | PWM = (PWM <sub>max</sub> x RGB + 128) >> 8 |

Table 22 – Scaling of blue and green LED channel

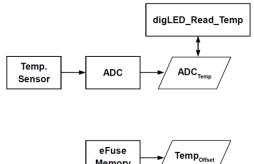

## 4.4 Temperature Detection

For temperature detection, the controller chip provides an analog temperature sensor. This can be read back via the ADC and the API command digLED\_Read\_Temp. The return value ADC<sub>Temp</sub> alone is not sufficient for detecting the temperature.

The Temp<sub>Offset</sub> parameter, which is used for the electrical calibration of the temperature sensor, must also be known for this purpose. The value is stored in the eFuse memory of the device and can be read out via the API command digLED\_Read\_Param.

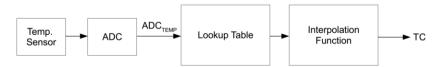

Figure 18 – Temperature detection

| Parameter              | Description                                                                                      | Diagnostic API command | Unit  |

|------------------------|--------------------------------------------------------------------------------------------------|------------------------|-------|

| ADCTemp                | ADC temperature value.<br>Varies vs. junction temperature.                                       | digLED_Read_Temp       | digit |

| Temp <sub>Offset</sub> | Temperature sensor offset value.<br>Constant calibration value.<br>Single readout is sufficient. | digLED_Read_Param      | digit |

|  | Table 23 – | Temperature | detection | parameters |

|--|------------|-------------|-----------|------------|

|--|------------|-------------|-----------|------------|

With ADC<sub>Temp</sub>, Temp<sub>Offset</sub> and the equation of Table 24, the junction temperature of the device can be determined.

| Parameter           | Description                   | Equation                                                  | Unit |

|---------------------|-------------------------------|-----------------------------------------------------------|------|

| T <sub>j, det</sub> | Detected junction temperature | $T_{j,det} = (Temp_{Offset} + 94.57 - ADC_{Temp}) / 0.87$ | °C   |

#### Table 24 – Temperature detection

| Ambient Temperature T <sub>A</sub> | Accuracy Tj, det | Unit |

|------------------------------------|------------------|------|

| -40                                | ±17.7            | °C   |

| 25                                 | ±8.8             | °C   |

| 105                                | ±4.8             | °C   |

Table 25 - Temperature detection accuracy

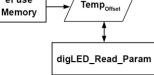

#### 4.5 Red LED Temperature Compensation Feature

The luminous intensity of typical red LEDs shows a significant temperature-dependency that is almost linear. The INLC10AQ provides a feature to compensate this effect. For that purpose, the on-chip sensor and ADC system detect the chip temperature ADC<sub>Temp</sub> that points to a lookup table (s. Figure 19). The interpolated lookup table output TC is a compensation factor which is considered in the PWM scaling process (s. Table 26). The lookup table and accordingly the factor TC can be linear or non-linear over temperature. The linear lookup table can be stored in the on-chip memory and is directly available after every hardware reset. A non-linear lookup table requires several downstream commands right after the initialization.

The compensation feature can be en-/disabled during the device initialization.

Figure 19 - Temperature compensation block diagram

| Temperate Compensation | Scaling                                                       |

|------------------------|---------------------------------------------------------------|

| Disabled               | PWM = (PWM <sub>max</sub> x RGB + 128) >> 8                   |

| Enabled                | PWM = ((PWM <sub>max</sub> x RGB + 128) >>8) x TC + 256) >> 9 |

#### Table 26 – Scaling of red LED channel

## 4.6 DIM Function for Accurate Low Light Colors

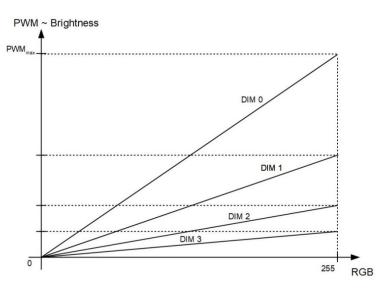

To extend the SET\_RGB command's resolution for accurate low light colors, the INLC10AQ provides the DIM command. The command divides the PWM duty cycles computed from the RGB setting. There are four divisors available. Details are shown in Figure 20 and Table 27.

In order to use the full RGB range at the highest dim level (DIM 3), the PWM<sub>max</sub> value must be at least 2048.

| Parameter                        | Size  | Description                                                        |

|----------------------------------|-------|--------------------------------------------------------------------|

| PWM <sub>Max</sub>               | 12bit | Brightness calibration value                                       |

| RGB                              | 8bit  | Color intensity value                                              |

| DIM                              | 2bit  | Dimming value                                                      |

| тс                               | 9bit  | Temperature compensation factor                                    |

| PWMGreen/Blue                    | 12bit | ((PWM <sub>Max</sub> x RGB + 128) >> 8) >> DIM                     |

| PWM <sub>Red</sub> (TC disabled) | 12bit | ((PWM <sub>Max</sub> x RGB + 128) >> 8) >> DIM                     |

| PWM <sub>Red</sub> (TC enabled)  | 12bit | ((((PWM <sub>Max</sub> x RGB + 128) >> 8) x TC + 256) >> 9) >> DIM |

#### Table 27 – DIM function

## 4.7 One Time Programmable Memory

The One Time Programmable Memory (OTP) is used to persistently store values determined during the device calibration.

# 4.7.1 Memory Layout

The size of the OTP memory is 128 bit. 32 bits are used for the cryptographic signature. All remaining 96 bits go into the data protected by the signature. The OTP memory layout is detailed in Table 28.

| Bit<br>Addr. | Bit<br>Size | Field      | Description                              | Value         |

|--------------|-------------|------------|------------------------------------------|---------------|

| 11:0         | 12          | config     | Manufacturing reserved bits              | 0x001-0xfff   |

| 23:12        | 12          | pwm_r_max  | Max. PWM value for red LED channel:      | Oxfff         |

| 35:24        | 12          | pwm_g_max  | Max. PWM value for green LED channel:    | Oxfff         |

| 47:36        | 12          | pwm_b_max  | Max. PWM value for blue LED channel:     | Oxfff         |

| 51:48        | 4           | peak_cur_g | Peak current value for green LED channel | 0x4           |

| 55:52        | 4           | peak_cur_b | Peak current value for blue LED channel  | 0x4           |

| 64:56        | 9           | temp_offs  | Temperature offset                       | 0x109 0x1dd   |

| 68:65        | 4           | adc_offs   | ADC offset calibration value             | 0x0 0xf       |

| 72:69        | 4           | adc_vref   | ADC reference voltage calibration value  | 0x0 0xf       |

| 76:73        | 4           | bias       | Bias reference value                     | 0x0 0xf       |

| 85:77        | 9           | tc_base    | Temperature compensation base value:     | 0x0           |

| 94:86        | 9           | tc_offs    | Temperature compensation offset value    | 0x0           |

| 95           | 1           | last_fuse  | Last fuse, OTP write protection          | 0x1           |

| 111:96       | 16          | sig0       | 16 lower signature bits                  | 0x0000-0xffff |

| 127:112      | 16          | sig1       | 16 upper signature bits                  | 0x0000-0xffff |

Table 28 – Memory layout

# 5.0 Recommended external circuits

Figure 21 - Implementation as controller and driver for external LEDs

Figure 22 - Implementation as signal converter

In order to prevent voltage drops, it is recommended to mount the capacitors C1 and C2 closely to the Vcc pin and to the anodes of the RGB diodes. The dimensioning of the capacitors depends on the PCB layout and the supply concept.

# 6.0 PIN Description

| Name   | Pin No.  | Туре  | Description                                                   |

|--------|----------|-------|---------------------------------------------------------------|

| BLUE   | 4        | I     | Blue LED cathode                                              |

| EXP    | 17       | GND   | Exposed pad                                                   |

| GREEN  | 2        | I     | Green LED cathode                                             |

| GND    | 6,16     | GND   | Ground                                                        |

| NC     | 10,11,12 | -     | Place pad for mechanical stability                            |

| PGND1  | 1        | GND   | Power ground green and red LED                                |

| PGND2  | 5        | GND   | Power ground blue LED                                         |

| PRG5   | 9        | GND   | Ground                                                        |

| RED    | 3        | I     | Red LED cathode                                               |

| SIO1_N | 8        | I/O   | Serial communication interface master side, negative polarity |

| SIO1_P | 7        | I/O   | Serial communication interface master side, positive polarity |

| SIO2_N | 14       | I/O   | Serial communication interface slave side, negative polarity  |

| SIO2_P | 15       | I/O   | Serial communication interface slave side, positive polarity  |

| VCC5   | 13       | Power | DC supply voltage                                             |

Table 29 – PIN description

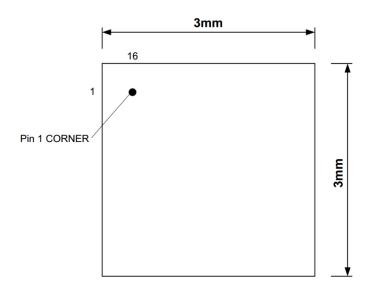

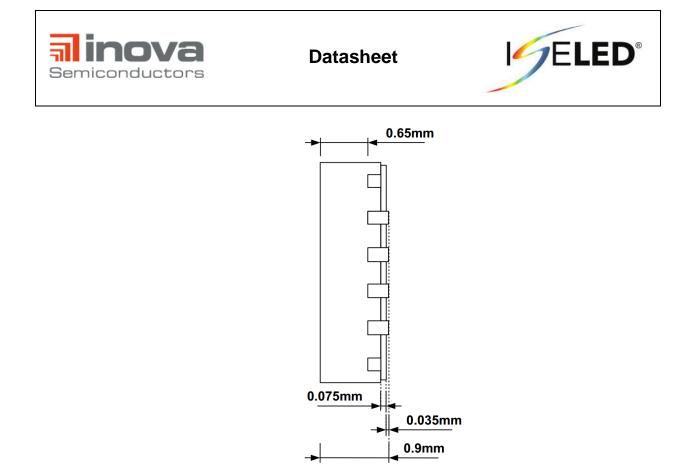

# 7.0 Package Dimensions

Figure 23 - Bottom view

Figure 24 - Top view

Figure 25 - Side view

# 8.0 Ordering information

| Device Ordering Code | Package   | Form of Delivery | Minimum Order<br>Quantity |

|----------------------|-----------|------------------|---------------------------|

| INLC10AQ-T           | WETQFN-16 | Tray             | 490                       |

| INLC10AQ-R4.5        | WETQFN-16 | Reel             | 4500                      |

Table 30 – Ordering information

# 9.0 Revision history

| Revision | Date          | Changes                                                                                                                                                                                                                                                                                                                      |

|----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1      | November 2017 | Initial release                                                                                                                                                                                                                                                                                                              |

| 0.2      | December 2017 | <ul><li>New chapter I.</li><li>New chapter 3.5</li></ul>                                                                                                                                                                                                                                                                     |

| 0.3      | January 2018  | <ul> <li>Changed storage temperature in Table 1</li> <li>Changed absolute maximum ratings Vcc in Table 1</li> <li>New Table 21</li> <li>New chapter 4.1.4, 4.3, 4.4, 4.5, 4.6, 8.0</li> <li>Updated Figures 6, 7, 8, 9,10, 11, 12,13</li> <li>Updated Tables 9, 10, 14</li> <li>Erased I<sub>avg</sub> in Table 5</li> </ul> |

| 0.4      | April 2018    | <ul><li>Updated Figure 10</li><li>Updated Chapter 4.5, 7.0</li></ul>                                                                                                                                                                                                                                                         |

| 0.5      | December 2018 | <ul> <li>Updated Table 1 – ESD protection</li> <li>Updated Table 22 – Exposed pad</li> <li>Updated Figure 23 – Exposed pad</li> </ul>                                                                                                                                                                                        |

| 0.6      | August 2019   | <ul> <li>New Product name INLC10AQ</li> <li>Update front page – erased "RGB" in title and product description</li> <li>Update Table 1, Table 2, Table 6, Table 7, Table 21, Table 23</li> <li>New Figure 16</li> <li>Update chapter 2.0, chapter 4.6</li> </ul>                                                              |

| 1.0      | May 2020      | <ul> <li>Qualified release</li> <li>Update Table 1-11, 20-21, 24, 28-29</li> <li>Update Figure 21-22</li> </ul>                                                                                                                                                                                                              |

Table 31 – Revision history

Inova Semiconductors GmbH Grafinger Str. 26 D-81671 Munich, Germany Phone: +49 (0)89 / 45 74 75 - 60 Fax: +49 (0)89 / 45 74 75 - 88 **E-mail:** info@inova-semiconductors.de URL: <u>http://www.inova-semiconductors.com</u>

is a registered trademark of Inova Semiconductors GmbH

All other trademarks or registered trademarks are the property of their respective holders.

Inova Semiconductors GmbH does not assume any liability arising out of the applications or use of the product described herein; nor does it convey any license under its patents, copyright or any rights of others.

Inova Semiconductors products are not designed, intended or authorized for use as components in systems to support or sustain life, or for any other application in which the failure of the product could create a situation where personal injury or death may occur. The Information contained in this document is believed to be current and accurate as of the publication date. Inova Semiconductors GmbH reserves the right to make changes at any time in order to improve reliability, function or performance to supply the best product possible.

Inova Semiconductors GmbH assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made.

© Inova Semiconductors GmbH 2020. All rights reserved