**Vishay Siliconix**

RoHS

COMPLIANT

HALOGEN

FREE

4.5 V to 55 V Input, 3 A, 5 A, 8 A, 12 A microBUCK® DC/DC Converter

#### LINKS TO ADDITIONAL RESOURCES

**PowerCAD** Design Tool

#### DESCRIPTION

The SiC47x is a family of wide input voltage, high efficiency synchronous buck regulators with integrated high side and low side power MOSFETs. Its power stage is capable of supplying high continuous current at up to 2 MHz switching frequency. This regulator produces an adjustable output voltage down to 0.8 V from 4.5 V to 55 V input rail to accommodate a variety of applications, including computing, consumer electronics, telecom, and industrial.

SiC47x's architecture allows for ultrafast transient response with minimum output capacitance and tight ripple regulation at very light load. The device enables loop stability regardless of the type of output capacitor used, including low ESR ceramic capacitors. The device also incorporates a power saving scheme that significantly increases light load efficiency. The regulator integrates a full protection feature set, including over current protection (OCP), output overvoltage protection (OVP), short circuit protection (SCP), output undervoltage protection (UVP) and over temperature protection (OTP). It also has UVLO for input rail and a user programmable soft start.

The SiC47x family is available in 3 A, 5 A, 8 A, 12 A pin compatible 5 mm by 5 mm lead (Pb)-free power enhanced MLP55-27L package.

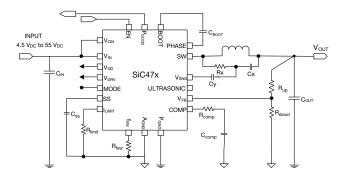

#### **TYPICAL APPLICATION CIRCUIT**

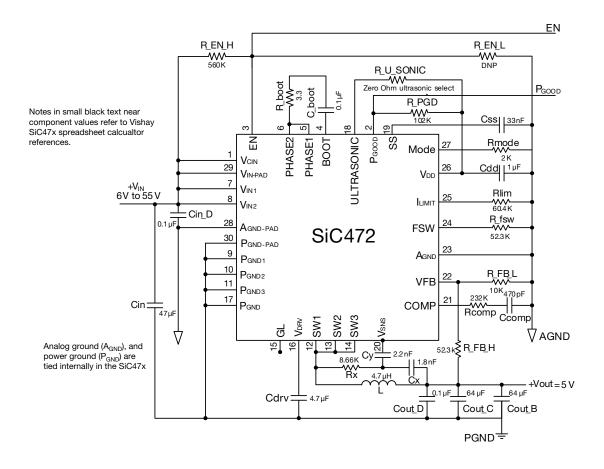

Fig. 1 - Typical Application Circuit for SiC47x

S21-1143-Rev. G, 29-Nov-2021

**FEATURES**

- Single supply operation from 4.5 V to 55 V input voltage

- Adjustable output voltage down to 0.8 V

- Scalable solution 3 A (SiC474), 5 A (SiC473), 8 A (SiC472), 12 A (SiC471)

- Output voltage tracking and sequencing with pre-bias start up

- ± 1 % output voltage accuracy at -40 °C to +125 °C

- Highly efficient

- 98 % peak efficiency

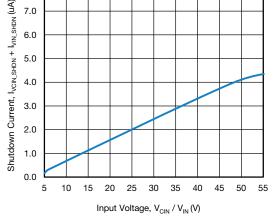

- 4 µA supply current at shutdown

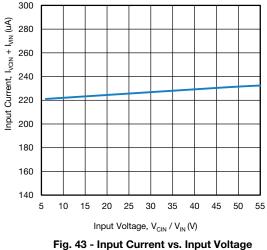

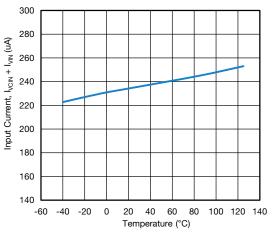

- 235 µA operating current, not switching

- · Highly configurable

- Adjustable switching frequency from 100 kHz to 2 MHz

- Adjustable soft start and adjustable current limit

- 3 modes of operation, forced continuous conduction, power save or ultrasonic

- Robust and reliable

- Output over voltage protection

- Output under voltage / short circuit protection with auto retry

- Power good flag and over temperature protection

- by Vishay PowerCAD online design - Supported simulation

- Material categorization: for definitions of compliance please see www.vishay.com/doc?99912

#### **APPLICATIONS**

- Industrial and automation

- Home automation

- · Industrial and server computing

- Networking, telecom, and base station power supplies

- Unregulated wall transformer

- Robotics

- High end hobby electronics: remote control cars, planes, and drones

- Battery management systems

- Power tools

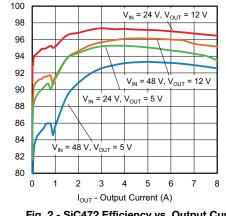

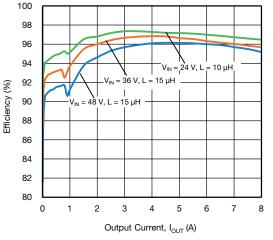

- Efficiency (%)

eff.

Vending, ATM, and slot machines

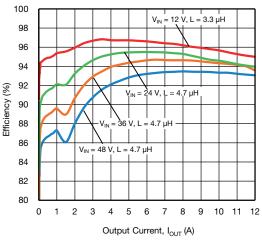

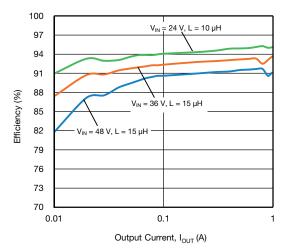

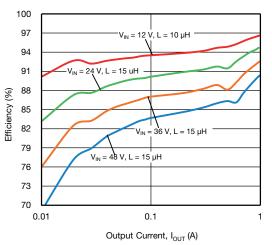

Fig. 2 - SiC472 Efficiency vs. Output Current

Document Number: 75786

For technical questions, contact: powerictechsupport@vishay.com THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

**Vishay Siliconix**

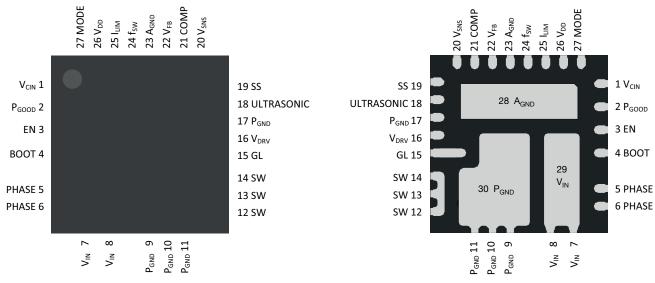

### **PIN CONFIGURATION**

Fig. 3 - SiC47x Pin Configuration

| PIN NUMBER        | SYMBOL             | DESCRIPTION                                                                                                                                                                                                                 |

|-------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | V <sub>CIN</sub>   | Supply voltage for internal regulators $V_{DD}$ and $V_{DRV}$ . This pin should be tied to $V_{IN}$ , but can also be connected to a lower supply voltage (> 5 V) to reduce losses in the internal linear regulators        |

| 2                 | P <sub>GOOD</sub>  | Open-drain power good indicator - high impedance indicates power is good. An external pull-up resistor is required                                                                                                          |

| 3                 | EN                 | Enable pin. Tie high/low to enable/disable the IC accordingly. This is a high voltage compatible pin, can be tied to $V_{\rm IN}$                                                                                           |

| 4                 | BOOT               | High side driver bootstrap voltage                                                                                                                                                                                          |

| 5, 6              | PHASE              | Return path of high side gate driver                                                                                                                                                                                        |

| 7, 8, 29          | V <sub>IN</sub>    | Power stage input voltage. Drain of high side MOSFET                                                                                                                                                                        |

| 9, 10, 11, 17, 30 | P <sub>GND</sub>   | Power ground                                                                                                                                                                                                                |

| 12, 13, 14        | SW                 | Power stage switch node                                                                                                                                                                                                     |

| 15                | GL                 | Low side MOSFET gate signal                                                                                                                                                                                                 |

| 16                | V <sub>DRV</sub>   | Supply voltage for internal gate driver. When using the internal LDO as a bias power supply, $V_{DRV}$ is the LDO output. Connect a 4.7 $\mu$ F decoupling capacitor to $P_{GND}$                                           |

| 18                | ULTRASONIC         | Float to disable ultrasonic mode, connect to V <sub>DD</sub> to enable. Depending on the operation mode set by the mode pin, power save mode or forced continuous mode will be enabled when the ultrasonic mode is disabled |

| 19                | SS                 | Set the soft start ramp by connecting a capacitor to A <sub>GND</sub> . An internal current source will charge the capacitor                                                                                                |

| 20                | V <sub>SNS</sub>   | Power inductor signal feedback pin for system stability compensation                                                                                                                                                        |

| 21                | COMP               | Output of the internal error amplifier. The feedback loop compensation network is connected from this pin to the A <sub>GND</sub> pin                                                                                       |

| 22                | V <sub>FB</sub>    | Feedback input for switching regulator used to program the output voltage - connect to an external resistor divider from $V_{OUT}$ to $A_{GND}$                                                                             |

| 23, 28            | A <sub>GND</sub>   | Analog ground                                                                                                                                                                                                               |

| 24                | f <sub>SW</sub>    | Set the on-time by connecting a resistor to A <sub>GND</sub>                                                                                                                                                                |

| 25                | I <sub>LIMIT</sub> | Set the current limit by connecting a resistor to A <sub>GND</sub>                                                                                                                                                          |

| 26                | V <sub>DD</sub>    | Bias supply for the IC. $V_{DD}$ is an LDO output, connect a 1 $\mu$ F decoupling capacitor to $A_{GND}$                                                                                                                    |

| 27                | MODE               | Set various operation modes by connecting a resistor to A <sub>GND</sub> . See specification table for details                                                                                                              |

**Vishay Siliconix**

| ORDERING INFORMATION |                                           |              |  |  |

|----------------------|-------------------------------------------|--------------|--|--|

| PART NUMBER          | PACKAGE                                   | MARKING CODE |  |  |

| SiC471ED-T1-GE3      | PowerPAK <sup>®</sup> MLP55-27L           | SiC471       |  |  |

| SiC471EVB            | Referenc                                  | e board      |  |  |

| SiC472ED-T1-GE3      | ED-T1-GE3 PowerPAK <sup>®</sup> MLP55-27L |              |  |  |

| SiC472EVB            | Referenc                                  | e board      |  |  |

| SiC473ED-T1-GE3      | PowerPAK <sup>®</sup> MLP55-27L           | SiC473       |  |  |

| SiC473EVB            | Referenc                                  | e board      |  |  |

| SiC474ED-T1-GE3      | PowerPAK <sup>®</sup> MLP55-27L SiC474    |              |  |  |

| SiC474EVB            | Referenc                                  | e board      |  |  |

#### PART MARKING INFORMATION

pin 1 indicator part number code P/N = A Siliconix logo = Δ ESD symbol = F assembly factory code = Y year code = WW = week code LL lot code =

| <b>ABSOLUTE MAXIMUM RATINGS</b> (T          | $_{A}$ = 25 °C, unless otherwise noted) |                                               |      |  |

|---------------------------------------------|-----------------------------------------|-----------------------------------------------|------|--|

| ELECTRICAL PARAMETER                        | CONDITIONS                              | LIMITS                                        | UNIT |  |

| EN, V <sub>CIN</sub> , V <sub>IN</sub>      | Reference to P <sub>GND</sub>           | -0.3 to +60                                   |      |  |

| SW / PHASE                                  | Reference to P <sub>GND</sub>           | -0.3 to +60                                   |      |  |

| V <sub>DRV</sub>                            | Reference to P <sub>GND</sub>           | -0.3 to +6                                    |      |  |

| V <sub>DD</sub>                             | Reference to A <sub>GND</sub>           | -0.3 to +6                                    | v    |  |

| SW / PHASE (AC)                             | Reference to P <sub>GND</sub> ; 100 ns  | -10 to +66                                    | v    |  |

| BOOT                                        |                                         | -0.3 to V <sub>PHASE</sub> + V <sub>DRV</sub> |      |  |

| A <sub>GND</sub> to P <sub>GND</sub>        |                                         | -0.3 to +0.3                                  |      |  |

| All other pins                              | Reference to A <sub>GND</sub>           | -0.3 to V <sub>DD</sub> + 0.3                 |      |  |

| Temperature                                 |                                         |                                               |      |  |

| Junction temperature                        | TJ                                      | -40 to +150                                   | ℃    |  |

| Storage temperature                         | T <sub>STG</sub>                        | -65 to +150                                   | C    |  |

| Power Dissipation                           |                                         |                                               |      |  |

| Thermal resistance from junction-to-ambient |                                         | 12                                            | °C/W |  |

| Thermal resistance from junction-to-case    |                                         | 2                                             | 0/10 |  |

| ESD Protection                              |                                         |                                               |      |  |

| Electrostatic discharge protection          | Human body model, JESD22-A114           | 2000                                          | V    |  |

| Lieurostalic discharge protection           | Charged device model, JESD22-A101       | 500                                           | v    |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating/conditions for extended periods may affect device reliability.

www.vishay.com

Vishay Siliconix

| <b>RECOMMENDED OPERATING CONDITIONS</b> (all voltages referenced to GND = 0 V) |      |             |                        |      |  |

|--------------------------------------------------------------------------------|------|-------------|------------------------|------|--|

| PARAMETER                                                                      | MIN. | TYP.        | MAX.                   | UNIT |  |

| Input voltage (V <sub>IN</sub> )                                               | 4.5  | -           | 55                     |      |  |

| Control input voltage (V <sub>CIN</sub> ) <sup>(1)</sup>                       | 4.5  | -           | 55                     |      |  |

| Enable (EN)                                                                    | 0    | -           | 55                     | v    |  |

| Bias supply (V <sub>DD</sub> )                                                 | 4.75 | 5           | 5.25                   | v    |  |

| Drive supply voltage (V <sub>DRV</sub> )                                       | 4.75 | 5.3         | 5.55                   |      |  |

| Output voltage (V <sub>OUT</sub> )                                             | 0.8  | -           | 0.92 x V <sub>IN</sub> |      |  |

| Temperature                                                                    |      |             |                        |      |  |

| Recommended ambient temperature -40 to +105                                    |      |             | °C                     |      |  |

| Operating junction temperature                                                 |      | -40 to +125 |                        |      |  |

Note

<sup>(1)</sup> For input voltages below 5 V, provide a separate supply to  $V_{CIN}$  of at least 5 V to prevent the internal  $V_{DD}$  rail UVLO from triggering

| PARAMETER SYMBOL                        |                            | TEST CONDITIONS                                                  | MIN. | TYP. | MAX. | UNIT     |  |

|-----------------------------------------|----------------------------|------------------------------------------------------------------|------|------|------|----------|--|

| Power Supplies                          |                            |                                                                  | •    |      | •    | <u> </u> |  |

|                                         | N/                         | $V_{IN} = V_{CIN} = 6 V$ to 55 V                                 | 4.75 | 5    | 5.25 | v        |  |

| V <sub>DD</sub> supply                  | V <sub>DD</sub>            | $V_{IN} = V_{CIN} = 5 V$                                         | 4.7  | 5    | -    |          |  |

| V <sub>DD</sub> dropout                 | V <sub>DD_DROPOUT</sub>    | $V_{IN} = V_{CIN} = 5 \text{ V}, \text{ I}_{VDD} = 1 \text{ mA}$ | -    | 70   | -    | mV       |  |

| V <sub>DD</sub> UVLO threshold, rising  | V <sub>DD_UVLO</sub>       |                                                                  | 4    | 4.25 | 4.5  | V        |  |

| V <sub>DD</sub> UVLO hysteresis         | V <sub>DD_UVLO_HYST</sub>  |                                                                  | -    | 225  | -    | mV       |  |

| Maximum V <sub>DD</sub> current         | I <sub>DD</sub>            | $V_{IN} = V_{CIN} = 6 V$ to 55 V                                 | 3    | -    | -    | mA       |  |

|                                         | V                          | $V_{IN} = V_{CIN} = 6 V$ to 55 V                                 | 4.75 | 5.3  | 5.55 | v        |  |

| V <sub>DRV</sub> supply                 | V <sub>DRV</sub>           | $V_{IN} = V_{CIN} = 5 V$                                         | 4.8  | 5    | 5.2  | V        |  |

| V <sub>DRV</sub> dropout                | V <sub>DRV_DROPOUT</sub>   | $V_{IN} = V_{CIN} = 5 \text{ V}, I_{VDD} = 10 \text{ mA}$        | -    | 160  | -    | mV       |  |

| Maximum V <sub>DRV</sub> current        | V <sub>DRV</sub>           | $V_{IN} = V_{CIN} = 6 V$ to 55 V                                 | 30   | -    | -    | mA       |  |

| V <sub>DRV</sub> UVLO threshold, rising | V <sub>DRV_UVLO</sub>      |                                                                  | 4    | 4.25 | 4.5  | V        |  |

| V <sub>DRV</sub> UVLO hysteresis        | V <sub>DRV_UVLO_HYST</sub> |                                                                  | -    | 295  | -    | mV       |  |

| Input current                           | I <sub>VCIN</sub>          | Non-switching, $V_{FB} > 0.8 V$                                  | -    | 235  | 325  |          |  |

| Shutdown current                        | I <sub>VCIN_SHDN</sub>     | V <sub>EN</sub> = 0 V                                            | -    | 4    | 8    | μA       |  |

| Controller and Timing                   |                            |                                                                  | •    | •    |      | •        |  |

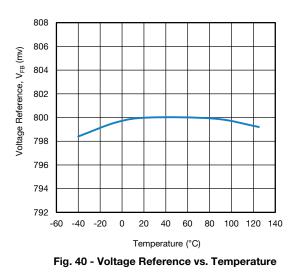

| Foodbook voltogo                        | V                          | T <sub>J</sub> = 25 °C                                           | 796  | 800  | 804  | m Δ/     |  |

| Feedback voltage                        | V <sub>FB</sub>            | $T_J = -40 \ ^{\circ}C \ to \ +125 \ ^{\circ}C \ ^{(1)}$         | 792  | 800  | 808  | m/V      |  |

| V <sub>FB</sub> input bias current      | I <sub>FB</sub>            |                                                                  | -    | 2    | -    | nA       |  |

| Transconductance                        | 9 <sub>m</sub>             |                                                                  | -    | 0.3  | -    | mS       |  |

| COMP source current                     | I <sub>COMP_SOURCE</sub>   |                                                                  | 15   | 20   | -    |          |  |

| COMP sink current                       | I <sub>COMP_SINK</sub>     |                                                                  | 15   | 20   | -    | μA       |  |

| Minimum on-time                         | t <sub>ON_MIN</sub> .      |                                                                  | -    | 90   | 110  | ns       |  |

| t <sub>ON</sub> accuracy                | t <sub>ON_ACCURACY</sub>   |                                                                  | -10  | -    | 10   | %        |  |

| On-time range                           | t <sub>ON_RANGE</sub>      |                                                                  | 110  | -    | 8000 | ns       |  |

|                                         |                            | Ultrasonic mode enabled                                          | 20   | -    | 2000 | kHz      |  |

| Frequency range                         | f <sub>sw</sub>            | Ultrasonic mode disabled                                         | 0    | -    | 2000 |          |  |

| Minimum off-time                        | t <sub>OFF_MIN</sub> .     |                                                                  | 190  | 250  | 310  | ns       |  |

| Soft start current                      | I <sub>SS</sub>            |                                                                  | 3    | 5    | 7    | μA       |  |

| Soft start voltage                      | V <sub>SS</sub>            | When V <sub>OUT</sub> reaches regulation                         | -    | 1.5  | -    | V        |  |

S21-1143-Rev. G, 29-Nov-2021

| PARAMETER                        | SYMBOL                                    | TEST CONDITIONS                                                                                  |      | TYP. | MAX. | UNI |

|----------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|-----|

| Fault Protections                |                                           |                                                                                                  |      |      |      |     |

|                                  |                                           | SiC471 (12 A),<br>R <sub>ILIM</sub> = 60 kΩ, T <sub>J</sub> = -10 °C to +125 °C                  |      | 15   | 18   |     |

| Valley current limit             | lass                                      | SiC472 (8 A),<br>R <sub>ILIM</sub> = 60 kΩ, T <sub>J</sub> = -10 °C to +125 °C                   | 8    | 10   | 12   | A   |

|                                  | I <sub>OCP</sub>                          | SiC473 (5 A), $R_{\rm ILIM}$ = 43 k $\Omega,T_{\rm J}$ = -10 °C to +125 °C $^{(2)}$              | 5.6  | 7    | 8.4  |     |

|                                  |                                           | SiC474 (3 A),<br>R <sub>ILIM</sub> = 60 kΩ, T <sub>J</sub> = -10 °C to +125 °C                   | 4    | 5    | 6    |     |

| Output OVP threshold             | V <sub>OVP</sub>                          | $V_{FB}$ with respect to 0.8 V reference                                                         | -    | 20   | -    | %   |

| Output UVP threshold             | V <sub>UVP</sub>                          | VFB with respect to 0.6 V reielence                                                              | -    | -80  | -    | 70  |

| Over temperature protection      | T <sub>OTP_RISING</sub>                   | Rising temperature                                                                               |      | 150  | -    | °C  |

| Over temperature protection      | T <sub>OTP_HYST</sub>                     | Hysteresis                                                                                       | -    | 35   | -    |     |

| Power Good                       |                                           |                                                                                                  |      |      |      |     |

| Power good output threshold      | V <sub>FB_RISING_VTH_OV</sub>             | DV V <sub>FB</sub> rising above 0.8 V reference                                                  |      | 20   | -    | - % |

| Tower good output threshold      | V <sub>FB_FALLING_VTH_UV</sub>            | V <sub>FB</sub> falling below 0.8 V reference                                                    | -    | -10  | -    | 70  |

| Power good hysteresis            | V <sub>FB_HYST</sub>                      |                                                                                                  | -    | 50   | -    | m\  |

| Power good on resistance         | R <sub>ON_PGOOD</sub>                     |                                                                                                  |      | 7.5  | 15   | Ω   |

| Power good delay time            | er good delay time t <sub>DLY_PGOOD</sub> |                                                                                                  | 15   | 25   | 35   | μs  |

| EN / MODE / Ultrasonic Threshold |                                           |                                                                                                  |      |      |      |     |

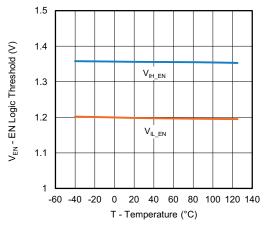

| EN logic high level              | V <sub>EN_H</sub>                         |                                                                                                  | -    | 1.35 | -    |     |

| EN logic low level               | V <sub>EN_L</sub>                         |                                                                                                  | -    | 1.2  | -    | V   |

| EN hysteresis                    | V <sub>HYST</sub>                         |                                                                                                  | -    | 0.15 | -    |     |

| EN pull down resistance          | R <sub>EN</sub>                           |                                                                                                  | -    | 5    | -    | M   |

| Ultrasonic mode high Level       | V <sub>ULTRASONIC_H</sub>                 |                                                                                                  | 2    | -    | -    | v   |

| Ultrasonic mode low level        | V <sub>ULTRASONIC_L</sub>                 |                                                                                                  | -    | -    | 0.8  | v   |

| Mode pull up current             | I <sub>MODE</sub>                         |                                                                                                  | 3.75 | 5    | 6.25 | μA  |

| Mode 1                           |                                           | Power save mode enabled, V <sub>DD</sub> , V <sub>DRV</sub><br>Pre-reg on                        | 0    | 2    | 100  |     |

| Mode 2                           | P                                         | Power save mode disabled, $V_{DD}$ , $V_{DRV}$<br>Pre-reg on                                     | 298  | 301  | 304  | kΩ  |

| Mode 3                           | R <sub>MODE</sub>                         | Power save mode disabled, $V_{DRV}$ Pre-reg off, $V_{DD}$ Pre-reg on, provide external $V_{DRV}$ | 494  | 499  | 504  | κ5. |

| Mode 4                           |                                           | Power save mode enabled, $V_{DRV}$ Pre-reg off, $V_{DD}$ Pre-reg on, provide external $V_{DRV}$  | 900  | 1000 | 1100 |     |

Notes

<sup>(1)</sup> Guaranteed by design

<sup>(2)</sup> Guaranteed by design for SiC473 OCP measurements

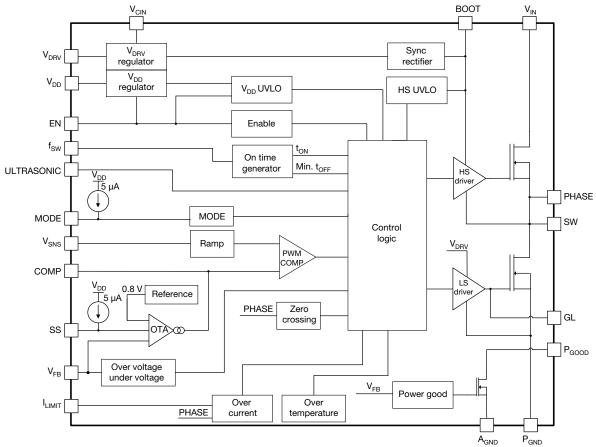

#### FUNCTIONAL BLOCK DIAGRAM

Fig. 4 - SiC47x Functional Block Diagram

**OPERATIONAL DESCRIPTION**

#### **Device Overview**

SiC47x is a high efficiency synchronous buck regulator family capable of delivering up to 12 A continuous current. The device has programmable switching frequency of 100 kHz to 2 MHz. The voltage mode, constant on time control scheme delivers fast transient response, minimizes the number of external components and enables loop stability regardless of the type of output capacitor used, including low ESR ceramic capacitors. The device also incorporates a power saving feature that enables diode emulation mode and frequency fold back as the load decreases.

SiC47x has a full set of protection and monitoring features:

- Over current protection in pulse-by-pulse mode

- Output overvoltage protection

- Output undervoltage protection with auto retry

- · Over temperature protection with hysteresis

- Dedicated enable pin for easy power sequencing

- Power good open drain output

- This device is available in MLP55-27L package to deliver high power density and minimize PCB area

#### **Power Stage**

SiC47x integrates a high performance power stage with a n-channel high side MOSFET and a n-channel low side MOSFET optimized to achieve up to 98 % efficiency.

The power input voltage (V\_{IN}) can go up to 55 V and down as low as 4.5 V for power conversion.

#### **Control Scheme**

SiC47x employs a voltage mode COT control mechanism in conjunction with adaptive zero current detection which allows for power saving in discontinuous conduction mode (DCM). The switching frequency,  $f_{SW}$ , is set by an external resistor to  $A_{GND},\ R_{fsw}.$  The SiC47x operates between 100 kHz to 2 MHz depending on  $V_{IN}$  and  $V_{OUT}$  conditions.

$$R_{fsw} = \frac{V_{OUT}}{f_{sw} \times 190 \times 10^{-12}}$$

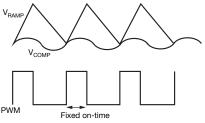

Note, as long as  $V_{\rm IN}$  and  $V_{\rm CIN}$  are connected together,  $f_{SW}$  has no dependency on  $V_{\rm IN}$  as the on time is adjusted as  $V_{\rm IN}$  varies. During steady-state operation, feedback voltage ( $V_{\rm FB}$ ) is compared with internal reference (0.8 V typ.) and the amplified error signal ( $V_{\rm COMP}$ ) is generated at the comp node by the external compensation components,  $R_{\rm COMP}$  and  $C_{\rm COMP}$ . An externally generated ramp signal and  $V_{\rm COMP}$  feed into a comparator. Once  $V_{\rm RAMP}$  crosses  $V_{\rm COMP}$ , an on-time

S21-1143-Rev. G, 29-Nov-2021

6 For technical questions, contact: <u>powerictechsupport@vishay.com</u> Document Number: 75786

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

pulse is generated for a fixed time. During the on-time pulse, the high side MOSFET will be turned on. Once the on-time pulse expires, the low side MOSFET will be turned on after a dead time period. The low side MOSFET will stay on for a minimum duration equal to the minimum off-time ( $t_{OFF\_MIN}$ ) and remains on until  $V_{RAMP}$  crosses  $V_{COMP}$ . The cycle is then repeated.

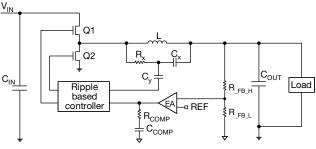

Fig. 6 illustrates the basic block diagram for voltage mode, constant on time architecture with external ripple injection,  $V_{\text{RAMP}}$ , while Fig. 5 illustrates the basic operational principle.

Fig. 5 - SiC47x Operational Principle

The need for ripple injection in this architecture is explained below. First, let us understand the basic principles of this control architecture:

- The reference of a basic voltage mode COT regulator is replaced with a high gain error amplifier loop. The loop ensures the DC component of the output voltage follows the internal accurate reference voltage, providing excellent regulation

- A second voltage feedback path via V<sub>SNS</sub> with a V<sub>RAMP</sub> scheme ensures rapid correction of the transient perturbation

- This establishes two voltage loops, one is the steady state voltage feedback path (via the FB pin) and the other is the feed forward path (via the V<sub>SNS</sub> pin). The scheme gives the user the fast transient response of a COT regulator and the stable, jitter free, line and load regulation performance of a PWM controller

#### **Choosing the Ripple Injection Component Values**

For stability purposes the SiC47x requires adequate ripple injection amplitude. Adequate ripple amplitude is required for two main reasons:

- 1. To reduce jitter due to noise coupled into the system

- 2. To provide stable operation. Sub harmonic oscillation can occur with constant on time ripple control if below condition is not met

$$\text{ESR} \times \text{C}_{\text{OUT}} > \frac{\text{t}_{\text{ON}}}{2}$$

Therefore, when the converter design uses an all ceramic output capacitor or other low ESR output capacitors, instability can occur. In order to avoid this, a  $V_{RAMP}$  network is used to increase the equivalent  $R_{ESR}$  in order to satisfy the above condition. The  $V_{RAMP}$  amplitude must be large enough to avoid instability or noise sensitivity but not too large that it degrades transient performance. To ensure stable operation under CCM, DCM and ultrasonic mode, minimum  $V_{RAMP}$  amplitude of 100 mV is recommended for the SiC47x family of regulators. A maximum  $V_{RAMP}$  of 900 mV is recommended so as not to degrade transient response.

Fig. 6 - SiC47x Control Block Diagram

Below is the equation for calculating the V<sub>RAMP</sub> amplitude.

$$V_{RAMP} = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{(V_{IN} \times f_{sw} \times C_x \times R_x)}$$

$V_{\text{RAMP}}$  amplitude is a function of  $V_{\text{IN}}, V_{\text{OUT}}$ , and switching frequency and should be adjusted whenever  $V_{\text{IN}}, V_{\text{OUT}},$  or switching frequency is changed.

For a given buck regulator design,  $V_{OUT}$  and switching frequency is typically fixed, while the converter may be expected to work for a wide  $V_{\rm IN}$  range. The  $V_{\rm RAMP}$  amplitude will increase as  $V_{\rm IN}$  is increased and increase the power dissipated by  $R_x$ . A proper selection of  $R_X$ , package size and value, should take into account the maximum power dissipation at the expected operating conditions.

In order to optimize the  $V_{\text{RAMP}}$  amplitude over a desired  $V_{\text{IN}}$  range use the following procedure to calculate  $R_x,\,C_x,$  and  $C_v.$

1. The equation below calculates  $R_X$  as a function of  $V_{IN}$ ,  $V_{OUT}$ , and maximum allowable power dissipated by  $R_X$ .

$$R_{x} = \frac{V_{IN\_MAX.} \times V_{OUT} \times (1 - D)}{P_{RX MAX.}}$$

where  $P_{RX\_MAX}$  is the maximum allowed power dissipation in  $R_x$ . Note, the maximum power dissipation of a 0603 sized resistor is typically 25 mW. Power dissipation derating must be taken into account for high ambient temperatures

2. The equation below calculates  $C_{X\_MIN}$  as a function of  $V_{IN}$  and maximum allowed  $V_{RAMP}$  amplitude.

$$C_{X\_MIN.} = \frac{P_{RX\_MAX.}}{V_{IN\_MAX.} \times f_{sw} \times V_{BAMP\_MAX.}}$$

where  $V_{RAMP_MAX.} = 900 \text{ mV}$

- 3. Using  $V_{RAMP}$  equation, calculate  $V_{RAMP\_MIN.}$  at minimum  $V_{IN}$  based on the  $R_x$  and the minimum  $C_x$  value calculated above

- 4. If  $V_{RAMP\_MIN.}$  is > 200 mV, set  $C_x$  to  $C_{X\_MIN.}$ , otherwise set  $C_x$  to  $(\bar{C}_{X\_MIN.} \times V_{RAMP\_MIN.}/200 \text{ mV})$ . If  $V_{RIPPLE\_MIN.}$  is < 100 mV, increase  $P_{RX\_MAX.}$  and recalculate  $R_X$  and  $C_X$

- 5.  $C_y$  should be large enough not to distort the V<sub>RAMP</sub> and small enough not to load excessively the V<sub>RAMP</sub> network (R<sub>x</sub> and C<sub>x</sub>). Please use the follow formula:  $C_y = 1/(820 \times f_{sw})$

This procedure allows for a maximum range of operation.

S21-1143-Rev. G, 29-Nov-2021

7 For technical questions, contact: <u>powerictechsupport@vishay.com</u>

www.vishay.com

### **Vishay Siliconix**

#### Error Amplifier Compensation Value Selection (for reference only)

$R_{COMP}$  and  $C_{COMP}$  in the Fig. 6 are the components used to compensate the control loop.

For optimal transient response, the crossover frequency should be:

- Set typically at 1/10<sup>th</sup> to 1/5<sup>th</sup> of the converter switching frequency (Vishay's component calculator tool uses 1/10<sup>th</sup> the converter switching frequency)

- Be above the LC filter resonance frequency which is 1/2  $\pi\sqrt{LC}$

The procedure to select the R<sub>COMP</sub> and C<sub>COMP</sub> such that the above conditions are met is as follows:

1. Plot the magnitude and phase of the control to output transfer function using the equation below. Control to output transfer function.

$$H(s) = A \times \frac{1 + sR_{c}C_{o} \times (1 + sR_{x}C_{x}) \times (1 + sR_{y}C_{y})}{\left(1 + \frac{sL}{R_{o}} + s^{2}LC_{o}\right) \times (1 + sR_{x}C_{x}) \times (1 + sR_{y}C_{y}) + AR_{y}C_{y}s \times \left[1 + s \times \left(R_{x}C_{x} + \frac{L}{R_{o}}\right) + s^{2} \times \left(R_{x}R_{c}C_{x}C_{o} + LC_{o}\right)\right]}$$

Where A =  $(2V_{IN} \times R_x \times C_x \times f)/V_{OUT}$ , R<sub>x</sub>, C<sub>x</sub>, C<sub>y</sub> are components for ripple injection as shown in Fig. 6 and R<sub>y</sub> is the internal impedance of the V<sub>SNS</sub> pin and is = 65 k $\Omega$ .

Co - output capacitance

R<sub>c</sub> - output capacitor ESR

- 2. From the plot of the control to output transfer function, determine the gain and phase at the crossover frequency

- 3. Calculate the  $R_{COMP}$  using the equation

$$R_{COMP} = \frac{1}{G_{H} \times gm \times r_{FB}}$$

where  $G_H$  is the gain of the transfer function at cross over frequency, " $g_m$ " is the transconductance of the error amplifier (300 µS) and  $r_{FB}$  is the ratio of the feedback divider,  $r_{FB} = R_FB_L/(R_FB_L + R_FB_H)$

4. Select C<sub>COMP</sub> based on the placement of the zero such that phase margin is sufficient at the cross over frequency. A phase margin of over 60° is sufficient for converter stability. A good starting point is to place the compensation zero at 1/5<sup>th</sup> of the LC pole

$$C_{COMP} = \frac{5\sqrt{LC}}{R_{COMP}}$$

Once the component values are calculated, it is now possible to calculate the total loop gain. The total loop gain is the product of the control to output transfer function and the error amplifier transfer function.

The transfer function of the error amplifier is given by the equation below.

$$G(s) = gmR_{o} \times \frac{(1 + sR_{COMP}C_{COMP}) \times r_{FB}}{(1 + s \times (R_{COMP}C_{COMP} + R_{o}C_{COMP}))}$$

Where  $R_o = 40 M\Omega$  is the output resistance of the transconductance amplifier. Total loop transfer function = H(s)G(s)

### Power-Save Mode, Mode Pin, and Ultrasonic Pin Operation

To improve efficiency at light-loads, SiC47x provides a set of innovative implementations to reduce low side re-circulating current and switching losses. The internal zero crossing detector monitors SW node voltage to determine when inductor current starts to flow negatively. In power saving mode, as soon as inductor current crosses zero, the device first deploys diode mode by turning off the low side MOSFET. If load further decreases, switching frequency is reduced proportional to the load condition to save switching losses while keeping output ripple within tolerance. If the ultrasonic pin is tied to  $V_{\text{DD}}$ , the minimum switching frequency in discontinuous mode is > 20 kHz to avoid switching frequencies in the audible range. If this feature is not required ultrasonic mode can be disabled by floating the ULTRASONIC pin. When ultrasonic mode is disabled, the regulator will operate in forced continuous mode or power save mode where there is no limit to the lower frequency limit. In this state, at zero load, switching frequency can go as low as hundreds of hertz.

#### **OUTPUT MONITORING AND PROTECTION FEATURES**

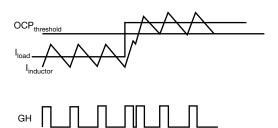

#### **Output Over-Current Protection (OCP)**

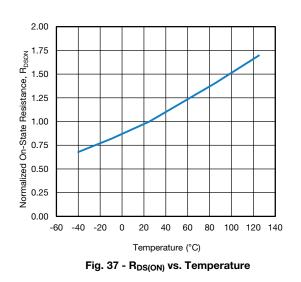

SiC47x has pulse-by-pulse over current limit control. The inductor current is monitored during low side MOSFET conduction time through  $R_{DS(on)}$  sensing. After a pre-defined blanking time, the inductor current is compared with an internal OCP threshold. If inductor current is higher than OCP threshold, high side MOSFET is kept off until the inductor current falls below OCP threshold.

OCP is enabled immediately after  $V_{DD}$  passes UVLO level. OCP is set by an external resistor,  $R_{LIM}$  to  $A_{GND}$ . (See table 2)

#### **Output Undervoltage Protection (UVP)**

UVP is implemented by monitoring the FB pin. If the voltage level at FB drops below 0.16 V for more than 25  $\mu$ s, a UVP event is recognized and both high side and low side MOSFETs are turned off. After a duration equivalent to 20 soft start periods, the IC attempts to re-start. If the fault condition still exists, the above cycle will be repeated.

UVP is only active after the completion of soft-start sequence.

#### **Output Over Voltage Protection (OVP)**

OVP is implemented by monitoring the FB pin. If the voltage level at FB rising above 0.96 V, a OVP event is recognized and both high side and low side MOSFETs are turned off. Normal operation is resumed once FB voltage drop below 0.91 V. To improve the converter efficiency, the user can choose to disable the internal  $V_{DRV}$  regulator by picking either mode 3 or mode 4 and connecting a 5 V supply to the  $V_{DRV}$  pin. This reduces power dissipation in the SiC47x by eliminating the  $V_{DRV}$  linear regulator losses.

The mode pin supports several modes of operation as shown in table 1. An internal current source is used to set the voltage on this pin using an external resistor:

| TABLE 1 - OPERATION MODES                                 |             |          |                    |  |  |

|-----------------------------------------------------------|-------------|----------|--------------------|--|--|

| MODE RANGE (kΩ) POWER SAVE<br>MODE INTERNAL V<br>REGULATO |             |          |                    |  |  |

| 1                                                         | 0 to 100    | Enabled  | ON                 |  |  |

| 2                                                         | 298 to 304  | Disabled | ON                 |  |  |

| 3                                                         | 494 to 504  | Disabled | OFF <sup>(1)</sup> |  |  |

| 4                                                         | 900 to 1100 | Enabled  | OFF <sup>(1)</sup> |  |  |

Note

$^{(1)}$  Connect a 5 V (± 5 %) supply to the V<sub>DRV</sub> pin The mode pin is not latched to any state and can be changed on the fly.

#### **Over Temperature Protection (OTP)**

OTP is implemented by monitoring the junction temperature. If the junction temperature rises above 150 °C, a OTP event is recognized and both high side and low MOSFETs are turned off. After the junction temperature falls below 115 °C (35 °C hysteresis), the device restarts by initiating a soft start sequence.

#### Sequencing of Input / Output Supplies

SiC47x has no sequencing requirements on its supplies or enables ( $V_{IN}$ ,  $V_{CIN}$ ,  $V_{DD}$ ,  $V_{DRV}$ , EN).

#### Enable

The SiC47x has an enable pin to turn the part on and off. Driving this pin above 1.4 V enables the device, while driving the pin below 0.4 V disables the device.

The EN pin is internally pulled to  $A_{GND}$  by a 5 M $\Omega$  resistor to prevent unwanted turn on due to a floating GPIO.

#### Soft-Start

During soft start time period, inrush current is limited and the output voltage is ramped gradually. The following control scheme is implemented:

Once the  $V_{DD}$  voltage reaches the UVLO trip point, an internal "Soft start Reference" (SR) begins to ramp up. The SR ramp rate is determined by the external soft start capacitor and an internal 5  $\mu$ A current source tied to the soft start pin.

The internal SR signal is used as a reference voltage to the error amplifier (see functional block diagram). The control scheme guarantees that the output voltage during the soft start interval will ramp up coincidently with the SR voltage. The soft-start time,  $t_{\rm SS}$ , is adjustable by calculating a capacitor value from the following equation.

$$t_{ss} = \frac{C_{ss} \times 0.8 \text{ V}}{5 \text{ }\mu\text{A}}$$

During soft-start period, OCP is activated. Short circuit protection is not active until soft-start is complete.

S21-1143-Rev. G, 29-Nov-2021

9

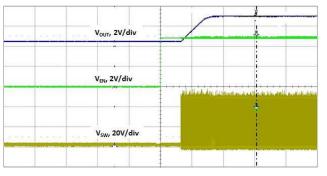

For technical questions, contact: <u>powerictechsupport@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

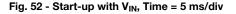

#### Pre-Bias Start-Up

In case of pre-bias startup, output is monitored through FB pin. If the sensed voltage on FB is higher than the internal reference ramp value, control logic prevents high side and low side MOSFETs from switching to avoid negative output voltage spike and excessive current sinking through low side MOSFET.

Fig. 8 - Pre-Bias Start-Up

#### **EXAMPLE SCHEMATIC OF SiC472**

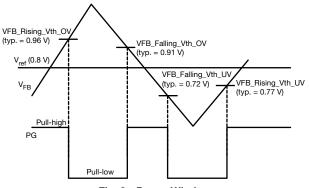

SiC47x's power good is an open-drain output. Pull  $P_{GOOD}$  pin high through a > 10K resistor to use this signal. Power good window is shown in Fig. 9. If voltage on FB pin is out of this window,  $P_{GOOD}$  signal is de-asserted by pulling down to  $A_{GND}$ . To prevent false triggering during transient events,  $P_{GOOD}$  has a 25  $\mu$ s blanking time.

## Fig. 10 - SiC472 Configured for 6 V to 55 V Input, 5 V Output at 6 A, 500 kHz Operation with Ultrasonic Power Save Mode Enabled all Ceramic Output Capacitance Design

www.vishay.com

#### **EXTERNAL COMPONENT SELECTION FOR THE SiC47x**

This section explains external component selection for the SiC47x family of regulators. Component reference designators in any equation refer to the schematic shown in Fig. 10.

The online simulation tool <u>PowerCAD</u> helps to make external component calculation simple. The user simply needs to enter required operating conditions.

#### **Output Voltage Adjustment**

If a different output voltage is needed, simply change the value of  $V_{\text{OUT}}$  and solve for  $R_{\mbox{FB}_{\mbox{H}}}$  based on the following formula:

$$\mathsf{R}_{\mathsf{FB}_{\mathsf{H}}} = \frac{\mathsf{R}_{\mathsf{FB}_{\mathsf{L}}}(\mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{FB}})}{\mathsf{V}_{\mathsf{FB}}}$$

where  $V_{FB}$  is 0.8 V.  $R_{FB\_L}$  should be a maximum of 10 k $\Omega$  to prevent  $V_{OUT}$  from drifting at no load.

#### **Switching Frequency Selection**

The following equation illustrates the relationship between frequency,  $V_{IN}$ ,  $V_{OUT}$ , and  $R_{fsw}$  value:

$$R_{fsw} = \frac{V_{OUT}}{f_{sw} \times (190 \times 10^{-12})}$$

#### Inductor Selection

In order to determine the inductance, the ripple current must first be defined. Low inductor values allow for the use of smaller package sizes but create higher ripple current which can reduce efficiency. Higher inductor values will reduce the ripple current and, for a given DC resistance, are more efficient. However, larger inductance translates directly into larger packages and higher cost. Cost, size, output ripple, and efficiency are all used in the selection process.

The ripple current will also set the boundary for power save operation. The SiC47x will typically enter power save mode when the load current decreases to 1/2 of the ripple current. For example, if ripple current is 1.8 A, power save operation will be active for loads less than 0.9 A. If ripple current is set at 30 % of maximum load current, power save will typically start at a load which is 15 % of maximum current.

The inductor value is typically selected to provide ripple current of 25 % to 50 % of the maximum load current. This provides an optimal trade-off between cost, efficiency, and transient performance. During the on-time, voltage across the inductor is ( $V_{IN}$  -  $V_{OUT}$ ). The equations for determining inductance are shown below.

$$t_{ON} = \frac{V_{OUT}}{V_{IN} x f_{sw}}$$

and

$$L = \frac{(V_{IN} - V_{OUT}) \times t_{ON}}{I_{OUT MAX.} \times K}$$

where, K is the maximum percentage of ripple current. The designer can quickly make a choice of inductor if the ripple percentage is decided, usually no more than 30 % however

higher or lower percentages of  $I_{\rm OUT}$  can be acceptable depending on application. This device allows choices larger than 30 %.

Other than the inductance the DCR and saturation current parameters are key values. The DCR causes an  $I^2R$  loss which will decrease the system efficiency and generate heat. The saturation current has to be higher than the maximum output current plus  $1/_2$  of the ripple current. In an over current condition the inductor current may be very high. All this needs to be considered when selecting the inductor.

#### **Output Capacitor Selection**

The SiC47x is stable with any type of output capacitors by choosing the appropriate  $V_{\text{RAMP}}$  components. This allows the user to choose the output capacitance based on the best trade off of board space, cost and application requirements.

The output capacitors are chosen based upon required ESR and capacitance. The maximum ESR requirement is controlled by the output ripple voltage requirement and the DC tolerance. The output voltage has a DC value that is equal to the valley of the output ripple plus half of the peak-to-peak ripple. A change in the output ripple voltage will lead to a change in DC voltage at the output. The relationship between output voltage ripple, output capacitance and ESR of the output capacitor is shown by the following equation:

$$V_{\text{RIPPLE}} = I_{\text{RIPPLE}(\text{MAX.})} \times \left(\frac{1}{8 \times C_{\text{o}} \times f_{\text{sw}}} + \text{ESR}\right)$$

(1)

Where  $V_{RIPPLE}$  is the maximum allowed output ripple voltage;  $I_{RIPPLE(MAX.)}$  is the maximum inductor ripple current;  $f_{sw}$  is the switching frequency of the converter;  $C_o$  is the total output capacitance; ESR is the equivalent series resistance of the total output capacitors.

In addition to the output ripple voltage requirement, the output capacitors need to meet transient requirements. A worst case load release condition (from maximum load to no load at the exact moment when inductor current is at the peak) determines the required capacitance. If the load release is instantaneous (load changes from maximum to zero within 1  $\mu$ s), the output capacitor must absorb all the energy stored in the inductor. The peak voltage on the capacitor, V<sub>PK</sub>, under this worst case condition can be calculated by following equation:

$$C_{OUT\_MIN.} = \frac{L x \left( I_{OUT} + \frac{1}{2} x I_{RIPPLE(MAX.)} \right)^{2}}{\left( V_{PK} \right)^{2} - \left( V_{OUT} \right)^{2}}$$

(2)

During the load release time, the voltage across the inductor is approximately -V<sub>OUT</sub>. This causes a down-slope or falling di/dt in the inductor. If the load di/dt is not much faster than the di/dt of the inductor, then the inductor current will tend to track the falling load current. This will reduce the excess inductive energy that must be absorbed by the output capacitor; therefore a smaller capacitance can be used. The following can be used to calculate the required capacitance for a given di<sub>LOAD</sub>/dt.

S21-1143-Rev. G, 29-Nov-2021

www.vishay.com

$I_{O} \propto \sqrt{D \times (1-D) + \frac{1}{12} \times \left(\frac{V_{OUT}}{L \times f_{sw} \times I_{OUT}}\right)^{2} \times (1-D)^{2} \times D}$

$C_{VIN\_MIN.} = I_{OUT} \times \frac{D \times (1 - D)}{V_{IN PK-PK} \times f_{sw}}$

If high ESR capacitors are used, it is good practice to also add low ESR ceramic capacitance. A 4.7 µF ceramic input

Note, account for voltage derating of capacitance when

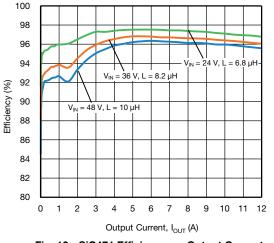

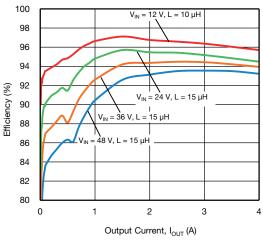

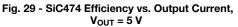

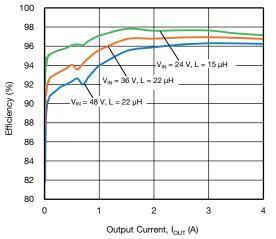

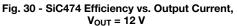

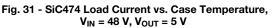

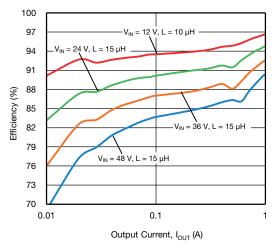

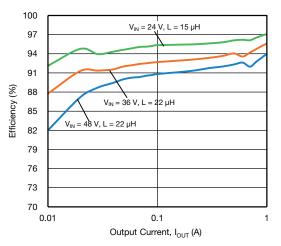

Fig. 11 to 39 in the following pages are the efficiency data

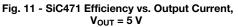

The measurements are taken based on the Vishay 6 layers,

The inductors used in the measurement are tabulated

INDUCTOR PART

NUMBER

IHLP6767GZER3R3M11

IHLP6767GZER4R7M11

IHLP6767GZER6R8M11

IHLP6767GZER8R2M11

IHLP6767GZER100M11

IHLP5050FDER5R6M51

IHLP5050FDER6R8M51

IHLP5050FDER8R2M51

IHLP5050FDER100M51

IHLP5050FDER150M51

IHLP5050FDER100M51

IHLP5050FDER150M51

IHLP5050FDER220M51

IHLP5050FDER100M51

IHLP5050FDER150M51

IHLP5050FDER220M51

DCR

(mΩ)

2.79

3.98

5.86

7.71

8.89

8.51

11.30

13.20

16.60

24.00

16.60

24.00

31.30

16.60

24.00

31.30

The minimum input capacitance can then be found,

capacitance is a suitable starting point.

for the SiC471, SiC472, SiC473, and SiC474.

**TABLE 3 - INDUCTOR VALUES**

INDUCTANCE

(µH)

3.3

4.7

6.8

8.2 10

5.6

6.8

8.2

10

15

10

15

22

10

15

22

using all ceramic input capacitors.

2 ounce copper evaluation board.

Efficiency Measurement

below.

DEVICE

PART

SiC471

SiC472

SiC473

SiC474

$I_{VCIN(RMS)} =$

**Vishay Siliconix**

Peak inductor current, I<sub>LPK</sub>, is shown by the next equation:

$$I_{LPK} = I_{MAX.} + \frac{1}{2} \times I_{RIPPLE(MAX.)}$$

The slew rate of load current =  $\frac{di_{LOAD}}{dt}$

$$C_{OUT\_MIN.} = I_{LPK} \times \frac{L \times \frac{I_{LPK}}{V_{OUT}} - \frac{I_{MAX.}}{dI_{LOAD}} \times dt}{2(V_{PK} - V_{OUT})}$$

(3)

Based on application requirement, either equation (2) or equation (3) can be used to calculate the ideal output capacitance to meet transition requirement. Compare this calculated capacitance with the result from equation (1) and choose the larger value to meet both ripple and transition requirement.

#### **Enable Pin Voltage**

The EN pin has an internal 5 M $\Omega$  pull down resistor connected to AGND. In order to enable the device, an external signal greater than 1.4 V is required. The enable can also be used to set the minimum V<sub>CIN</sub>, V<sub>IN</sub> startup voltage by connecting a voltage divider between VIN, EN, and PGND. An automated calculator is available to assist in component selection.

#### **Current Limit Resistor**

The current limit is set by placing a resistor between  $\mathsf{I}_{\mathsf{LIM}}$  and A<sub>GND</sub>. The values can be found using the following equation:

$$\mathsf{R}_{\mathsf{LIM}}(\mathsf{k}\Omega) = \frac{\mathsf{K}_{\mathsf{LIM}}}{\mathsf{I}_{\mathsf{OUT}\_\mathsf{MAX}} - \frac{(\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}) \times \mathsf{V}_{\mathsf{OUT}}}{2 \times \mathsf{f}_{\mathsf{sw}} \times \mathsf{V}_{\mathsf{IN}} \times \mathsf{L}}}$$

Where

- I<sub>OUT MAX</sub>, is desired DC current limit level

- K<sub>LIM</sub> is determined by Table 2

| TABLE 2 - K <sub>LIM</sub> VALUE AND R <sub>LIM</sub> RANGE |                  |                                       |  |  |  |

|-------------------------------------------------------------|------------------|---------------------------------------|--|--|--|

| PART NUMBER                                                 | K <sub>LIM</sub> | R <sub>LIM</sub> MIN. / MAX.<br>VALUE |  |  |  |

| SiC471                                                      | 900K             | 30K / 900K                            |  |  |  |

| SiC472                                                      | 600K             | 30K / 600K                            |  |  |  |

| SiC473                                                      | 300K             | 30K / 420K                            |  |  |  |

| SiC474                                                      | 300K             | 30K / 300K                            |  |  |  |

#### Note

It is suggested that the current limit setting not be higher than 2 times the rated current of the part. Be sure max. current limit is within the saturation current of the inductor

#### Input Capacitance

In order to determine the minimum capacitance the input voltage ripple needs to be specified;  $V_{IN PK-PK} \le 500 \text{ mV}$  is a suitable starting point. This magnitude is determined by the final application specification. The input current needs to be determined for the lowest operating input voltage,

S21-1143-Rev. G, 29-Nov-2021

### **Vishay Siliconix**

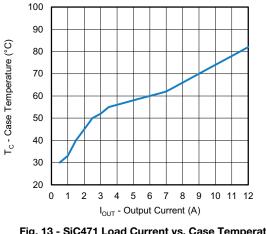

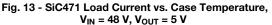

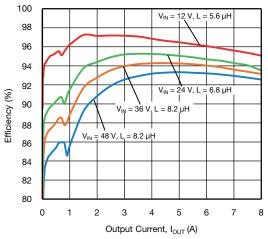

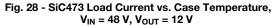

ELECTRICAL CHARACTERISTICS (V<sub>IN</sub> = 48 V, V<sub>OUT</sub> = 5 V, f<sub>sw</sub> = 300 kHz, SiC471 (12 A), unless otherwise noted)

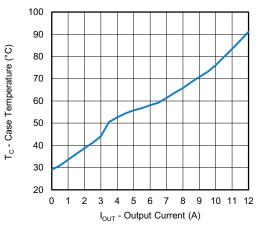

Fig. 12 - SiC471 Efficiency vs. Output Current,  $V_{OUT}$  = 12 V

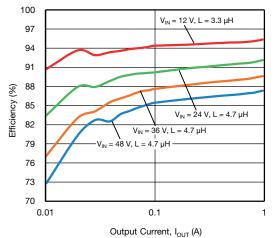

Fig. 14 - SiC471 Efficiency vs. Output Current - Light Load,  $V_{OUT} = 5 V$

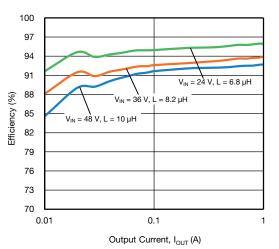

Fig. 15 - SiC471 Efficiency vs. Output Current - Light Load,  $V_{\text{OUT}}$  = 12 V

S21-1143-Rev. G, 29-Nov-2021

13

Document Number: 75786

For technical questions, contact: <u>powerictechsupport@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

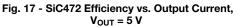

### Vishay Siliconix

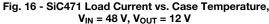

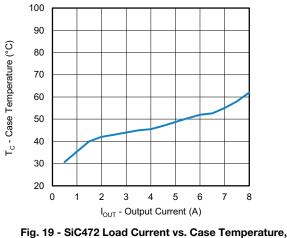

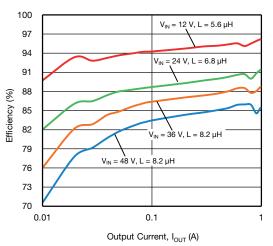

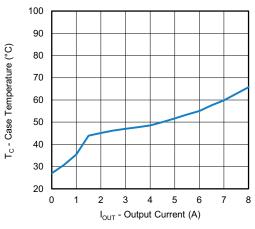

**ELECTRICAL CHARACTERISTICS** (V<sub>IN</sub> = 48 V, V<sub>OUT</sub> = 5 V, f<sub>sw</sub> = 300 kHz, SiC472 (8 A), unless otherwise noted)

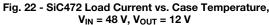

Fig. 18 - SiC472 Efficiency vs. Output Current,  $V_{OUT}$  = 12 V

S21-1143-Rev. G, 29-Nov-2021

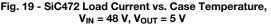

Fig. 20 - SiC472 Efficiency vs. Output Current - Light Load,  $V_{\text{OUT}}$  = 5 V

Fig. 21 - SiC472 Efficiency vs. Output Current - Light Load,  $V_{\text{OUT}}$  = 12 V

14

Document Number: 75786

For technical questions, contact: <u>powerictechsupport@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

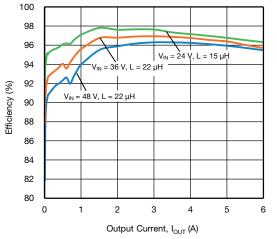

Vishay Siliconix

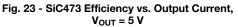

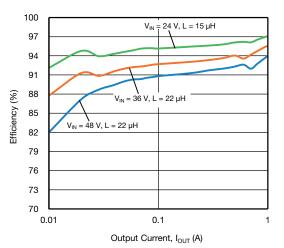

ELECTRICAL CHARACTERISTICS (V<sub>IN</sub> = 48 V, V<sub>OUT</sub> = 5 V, f<sub>sw</sub> = 300 kHz, SiC473 (5 A), unless otherwise noted)

Fig. 24 - SiC473 Efficiency vs. Output Current,  $V_{OUT}$  = 12 V

S21-1143-Rev. G, 29-Nov-2021

Fig. 26 - SiC473 Efficiency vs. Output Current - Light Load,  $V_{OUT}$  = 5 V

Fig. 27 - SiC473 Efficiency vs. Output Current - Light Load,  $V_{\text{OUT}}$  = 12 V

Document Number: 75786

For technical questions, contact: <a href="mailto:powerictechsupport@vishay.com">powerictechsupport@vishay.com</a> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <a href="http://www.vishay.com/doc?91000">www.vishay.com/doc?91000</a>

### **Vishay Siliconix**

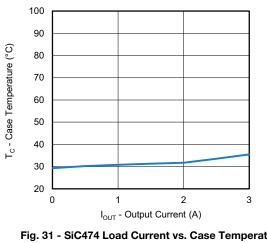

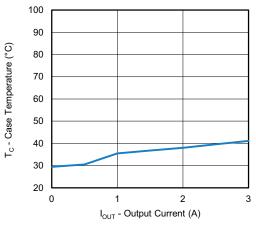

ELECTRICAL CHARACTERISTICS (VIN = 48 V, VOUT = 5 V, fsw = 300 kHz, SiC474 (3 A), unless otherwise noted)

Fig. 32 - SiC474 Efficiency vs. Output Current - Light Load,  $V_{OUT} = 5 V$

Fig. 33 - SiC474 Efficiency vs. Output Current - Light Load, V<sub>OUT</sub> = 12 V

S21-1143-Rev. G, 29-Nov-2021

16

Document Number: 75786

For technical questions, contact: <a href="mailto:powerictechsupport@vishay.com">powerictechsupport@vishay.com</a> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

**Vishay Siliconix**

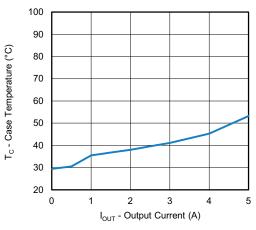

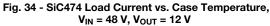

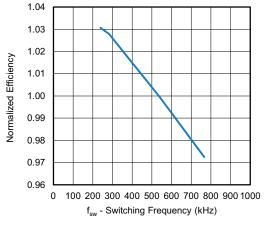

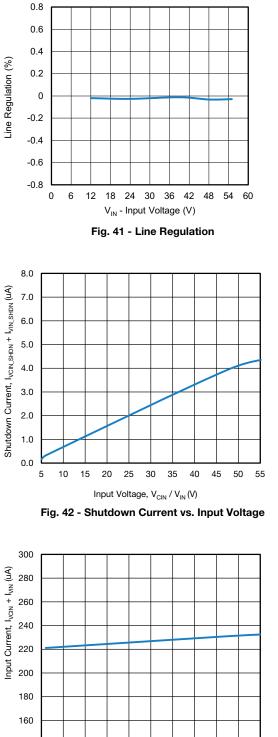

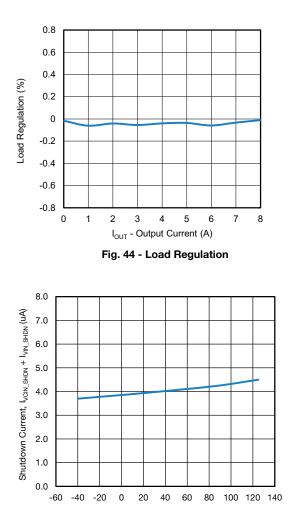

### ELECTRICAL CHARACTERISTICS (V<sub>IN</sub> = 48 V, V<sub>OUT</sub> = 5 V, f<sub>sw</sub> = 300 kHz, SiC472 (8 A), unless otherwise noted)

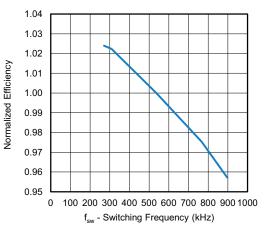

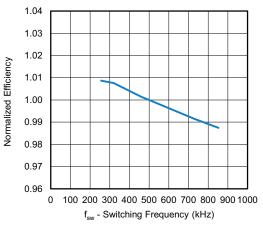

Fig. 35 - SiC471 Efficiency vs. Switching Frequency

Fig. 36 - SiC473 Efficiency vs. Switching Frequency

Fig. 38 - SiC472 Efficiency vs. Switching Frequency

Fig. 39 - SiC474 Efficiency vs. Switching Frequency

S21-1143-Rev. G, 29-Nov-2021

17

Document Number: 75786

For technical questions, contact: <u>powerictechsupport@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

Vishay Siliconix

Temperature (°C)

Fig. 45 - Shutdown Current vs. Junction Temperature

Fig. 46 - Input Current vs. Junction Temperature

S21-1143-Rev. G, 29-Nov-2021

18

Document Number: 75786

For technical questions, contact: powerictechsupport@vishay.com THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

**Vishay Siliconix**

**ELECTRICAL CHARACTERISTICS** ( $V_{IN}$  = 48 V,  $V_{OUT}$  = 5 V,  $f_{sw}$  = 300 kHz, SiC472 (8 A), unless otherwise noted)

Fig. 47 - EN Logic Threshold vs. Junction Temperature

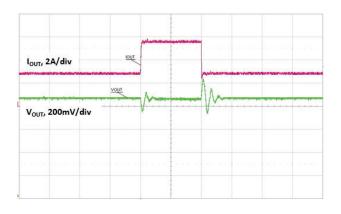

Fig. 48 - Load Transient (3 A to 6 A), Time = 100 µs/div

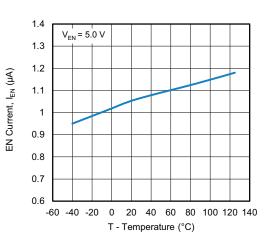

Fig. 50 - EN Current vs. Junction Temperature

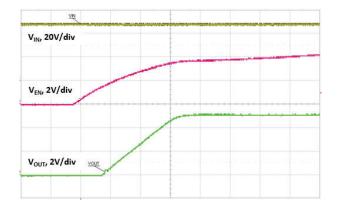

Fig. 51 - Line Transient (8 V to 48 V), Time = 10 ms/div

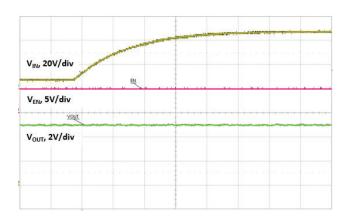

Fig. 49 - Start-Up with EN, Time = 1 ms/div

S21-1143-Rev. G, 29-Nov-2021

19 s. contact: powerictechsu Document Number: 75786

For technical questions, contact: <a href="mailto:powerictechsupport@vishay.com">powerictechsupport@vishay.com</a> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <a href="http://www.vishay.com/doc?91000">www.vishay.com/doc?91000</a>

## VISHAY www.vishay.com

## SiC471, SiC472, SiC473, SiC474

Vishay Siliconix

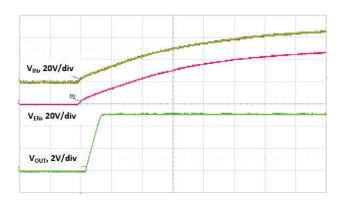

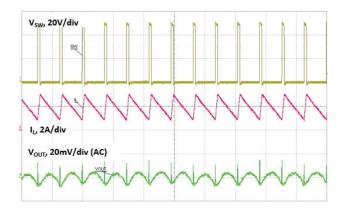

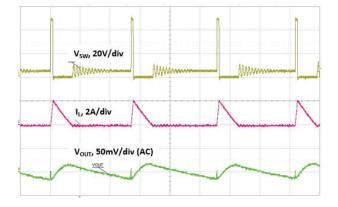

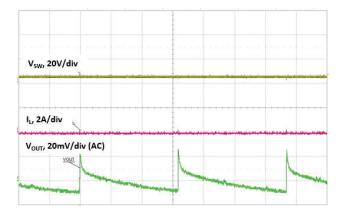

ELECTRICAL CHARACTERISTICS (VIN = 48 V, VOUT = 5 V, fsw = 300 kHz, SiC472 (8 A), unless otherwise noted)

Fig. 53 - Output Ripple 2 A, Time = 5 µs/div

Fig. 55 - Output Ripple 300 mA, Time = 5 µs/div

Fig. 54 - Output Ripple PSM, Time = 10 ms/div

### Vishay Siliconix

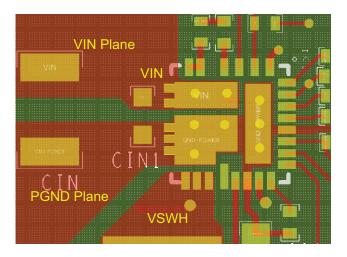

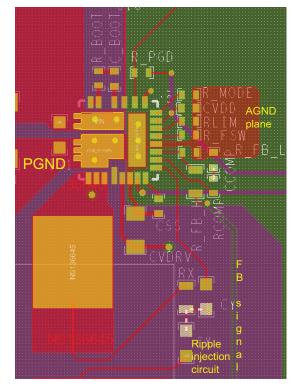

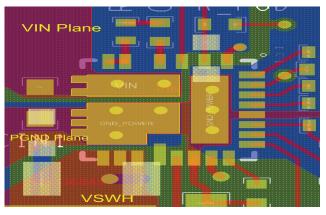

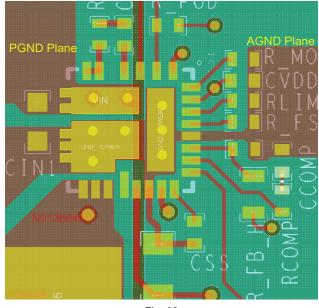

### PCB LAYOUT RECOMMENDATIONS

#### Step 1: V<sub>IN</sub>/GND Planes and Decoupling

Fig. 56

- 1. Layout  $V_{\text{IN}}$  and  $P_{\text{GND}}$  planes as shown above

- 2. Ceramic capacitors should be placed between  $V_{\text{IN}}$  and  $P_{\text{GND}},$  and very close to the device for best decoupling effect

- 3. Various ceramic capacitor values and package sizes should be used to cover entire coupling spectrum e.g. 1210 and 0603

- 4. Smaller capacitance values, closer to  $V_{\text{IN}}$  pin(s), provide better high frequency response

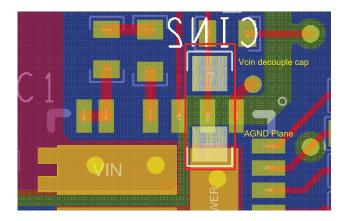

#### Step 2: V<sub>CIN</sub> Pin

#### Fig. 57

- 1.  $V_{CIN}$  is the input pin for both internal LDO and  $t_{ON}$  block.  $t_{ON}$  varies with input voltage and it is necessary to put a decoupling capacitor close to this pin

- 2. The connection can be made through a via and the capacitor can be placed at bottom layer

S21-1143-Rev. G, 29-Nov-2021

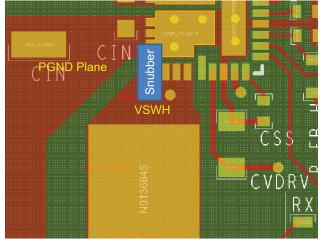

Step 3: SW Plane

Fig. 58

- 1. Connect output inductor to device with large plane to lower resistance

- 2. If any snubber network is required, place the components on the bottom side as shown above

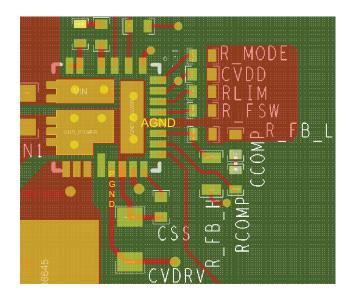

#### Step 4: V<sub>DD</sub>/V<sub>DRV</sub> Input Filter

Fig. 59

- 1.  $C_{VDD}$  cap should be placed between  $V_{DD}$  and  $A_{GND}$  to achieve best noise filtering

- C<sub>VDRV</sub> cap should be placed close to V<sub>DRV</sub> and P<sub>GND</sub> pins to reduce effects of trace impedance and provide maximum instantaneous driver current for low side MOSFET during switching cycle

21 For technical questions, contact: <u>powerictechsupport@vishay.com</u>

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

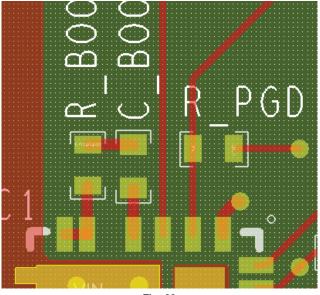

#### Step 5: BOOT Resistor and Capacitor Placement

Fig. 60

- 1.  $C_{BOOT}$  and  $R_{BOOT}$  need to be placed very close to the device, between PHASE and BOOT pins

- 2. In order to reduce parasitic inductance, it is recommended to use 0402 chip size for the resistor and the capacitor

#### **Step 6: Signal Routing**

- Separate the small analog signal from high current path. As shown above, the high current paths with high dv/dt, di/dt are placed on the left side of the IC, while the small control signals are placed on the right side of the IC. All the components for small analog signal should be placed closer to IC with minimum trace length

- 2. IC analog ground ( $A_{GND}$ ), pin 23, should have a single connection to  $P_{GND}$ . The  $A_{GND}$  ground plane connected to pin 23 helps to keep  $A_{GND}$  quiet and improves noise immunity

- 3. Feedback signal can be routed through inner layer. Make sure this signal is far from SW node and shielded by inner ground layer

- 4. Ripple injection circuit can be placed next to inductor. Kelvin connection as shown above is recommended

# Step 7: Adding Thermal Relief Vias and Duplicate Power Path Plane

Fig. 62

- 1. Thermal relief vias can be added on the  $V_{\rm IN}$  and  $P_{\rm GND}$  pads to utilize inner layers for high current and thermal dissipation

- 2. To achieve better thermal performance, additional vias can be placed on V<sub>IN</sub> and P<sub>GND</sub> planes. It is also necessary to duplicate the V<sub>IN</sub> and ground plane at bottom layer to maximize the power dissipation capability of the PCB

- 3. SW pad is a noise source and it is not recommended to place vias on this pad

- 4. 8 mil vias on pads and 10 mil vias on planes are ideal via sizes. The vias on pad may drain solder during assembly and cause assembly issues. Please consult with the assembly house for guideline

#### Step 8: Ground Layer

Fig. 63

- 1. It is recommended to make the entire inner layer (next to top layer) ground plane

- 2. This ground plane provides shielding between noise source on top layer and signal trace within inner layer

- 3. The ground plane can be broken into two sections,  $P_{GND}$  and  $A_{GND}$

www.vishay.com

## SiC471, SiC472, SiC473, SiC474

Vishay Siliconix

| PRODUCT SUMMARY               | PRODUCT SUMMARY                                                                       |                                                                                      |                                                                                      |                                                                                      |  |  |  |

|-------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

| Part number                   | SiC471                                                                                | SiC472                                                                               | SiC473                                                                               | SiC474                                                                               |  |  |  |

| Description                   | 12 A, 4.5 V to 55 V input,<br>100 kHz to 2 MHz,<br>synchronous microBUCK<br>regulator | 8 A, 4.5 V to 55 V input,<br>100 kHz to 2 MHz,<br>synchronous microBUCK<br>regulator | 5 A, 4.5 V to 55 V input,<br>100 kHz to 2 MHz,<br>synchronous microBUCK<br>regulator | 3 A, 4.5 V to 55 V input,<br>100 kHz to 2 MHz,<br>synchronous microBUCK<br>regulator |  |  |  |

| Input voltage min. (V)        | 4.5                                                                                   | 4.5                                                                                  | 4.5                                                                                  | 4.5                                                                                  |  |  |  |

| Input voltage max. (V)        | 55                                                                                    | 55                                                                                   | 55                                                                                   | 55                                                                                   |  |  |  |

| Output voltage min. (V)       | 0.8                                                                                   | 0.8                                                                                  | 0.8                                                                                  | 0.8                                                                                  |  |  |  |

| Output voltage max. (V)       | 0.92 x V <sub>IN</sub>                                                                | 0.92 x V <sub>IN</sub>                                                               | 0.92 x V <sub>IN</sub>                                                               | 0.92 x V <sub>IN</sub>                                                               |  |  |  |

| Continuous current (A)        | 12                                                                                    | 8                                                                                    | 5                                                                                    | 3                                                                                    |  |  |  |

| Switch frequency min. (kHz)   | 100                                                                                   | 100                                                                                  | 100                                                                                  | 100                                                                                  |  |  |  |

| Switch frequency max. (kHz)   | 2000                                                                                  | 2000                                                                                 | 2000                                                                                 | 2000                                                                                 |  |  |  |

| Pre-bias operation (yes / no) | Yes                                                                                   | Yes                                                                                  | Yes                                                                                  | Yes                                                                                  |  |  |  |

| Internal bias reg. (yes / no) | Yes                                                                                   | Yes                                                                                  | Yes                                                                                  | Yes                                                                                  |  |  |  |

| Compensation                  | External                                                                              | External                                                                             | External                                                                             | External                                                                             |  |  |  |

| Enable (yes / no)             | Yes                                                                                   | Yes                                                                                  | Yes                                                                                  | Yes                                                                                  |  |  |  |

| P <sub>GOOD</sub> (yes / no)  | Yes                                                                                   | Yes                                                                                  | Yes                                                                                  | Yes                                                                                  |  |  |  |

| Overcurrent protection        | Yes                                                                                   | Yes                                                                                  | Yes                                                                                  | Yes                                                                                  |  |  |  |

| Protection                    | OVP, OCP, UVP/SCP,<br>OTP, UVLO                                                       | OVP, OCP, UVP/SCP,<br>OTP, UVLO                                                      | OVP, OCP, UVP/SCP,<br>OTP, UVLO                                                      | OVP, OCP, UVP/SCP,<br>OTP, UVLO                                                      |  |  |  |

| Light load mode               | Selectable powersave /<br>ultrasonic                                                  | Selectable powersave / ultrasonic                                                    | Selectable powersave / ultrasonic                                                    | Selectable powersave / ultrasonic                                                    |  |  |  |

| Peak efficiency (%)           | 98                                                                                    | 98                                                                                   | 98                                                                                   | 98                                                                                   |  |  |  |

| Package type                  | PowerPAK MLP55-27L                                                                    | PowerPAK MLP55-27L                                                                   | PowerPAK MLP55-27L                                                                   | PowerPAK MLP55-27L                                                                   |  |  |  |

| Package size (W, L, H) (mm)   | 5 x 5 x 0.75                                                                          | 5 x 5 x 0.75                                                                         | 5 x 5 x 0.75                                                                         | 5 x 5 x 0.75                                                                         |  |  |  |

| Status code                   | 1                                                                                     | 1                                                                                    | 1                                                                                    | 1                                                                                    |  |  |  |

| Product type                  | microBUCK<br>(step down regulator)                                                    | microBUCK<br>(step down regulator)                                                   | microBUCK<br>(step down regulator)                                                   | microBUCK<br>(step down regulator)                                                   |  |  |  |

| Applications                  | Computing, consumer,<br>industrial, healthcare,<br>networking                         | Computing, consumer,<br>industrial, healthcare,<br>networking                        | Computing, consumer,<br>industrial, healthcare,<br>networking                        | Computing, consumer,<br>industrial, healthcare,<br>networking                        |  |  |  |

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package / tape drawings, part marking, and reliability data, see www.vishay.com/ppg?75786.

Vishay

## Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.