# Development Kit Setup with SDIO 2.0 and SDIO 3.0 Host DVK-ST60-SIPT/DVK-SU60-SIPT

Application Note v1.1

#### INTRODUCTION

Laird provides two kinds of development kits, DVK-ST60-SIPT and DVK-SU60-SIPT, for the 60-series SIP module. DVK-ST60-SIPT is for the ST60 product family with a SIP form factor and DVK-SU60-SIPT is for the SU60 SIP.

With SDIO 2.0 and SDIO 3.0, the development kit setup is different not only in the DVK board switch settings, but also with the SDIO connector wiring.

#### **DEVELOPMENT KIT PACKAGE CONTENTS**

- DVK-ST60-SIPT or DVK-SU60-SIPT board (1)

- SDIO extender with pin header (1)

- SDIO extender without pin header (1)

- Rainbow cable (1)

- Power adaptor (1)

- FlexPIFA antennas (P/N 001-0016) (2)

- Miscellaneous (such as USB cable, insert card, etc.)

#### **ENVIRONMENT SETUP WITH THE SDIO 2.0 HOST**

## **DVK-ST60-SIPT/DVK-SU60-SIPT Wiring**

To wire the DVK-ST60-SIPT/DVK-SU60-SIPT with SDIO 2.0 host, follow these steps:

1. Wire one side of rainbow cable to the SDIO extender with pin header. The SD-D1 should align with the connector marked in red.

Americas: +1-800-492-2320

Europe: +44-1628-858-940 Hong Kong: +852 2923 0610

**Application Note**

2. Wire the other side of rainbow cable with the connector on the DVK-ST60-SIPT/DVK-SU60-SIPT board. The pin closest to the nearby PCI-E bus should be aligned with the connector marked in red.

3. Connect the two antennas to the u.FL connectors on the DVK-ST60-SIPT/DVK-SU60-SIPT board.

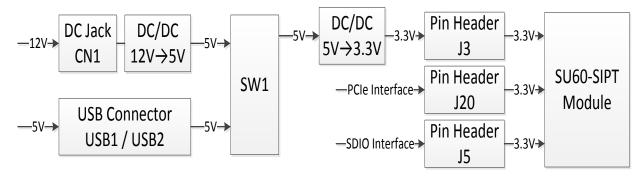

The development board can be powered from a DC 12V supply (into DC jack connector CN1), USB (type micro-B) connector (USB1 and USB2), or the host interface (SDIO interface).

**Application Note**

For regular usage, the power from SDIO bus should be enough with no need for external power from either the DC jack or USB port. To run continuous TX in a regulation test, the host may not be able to support enough current via the SDIO and may need external power.

#### DVK-ST60-SIPT/DVK-SU60-SIPT Board Switch and Jumper Setup

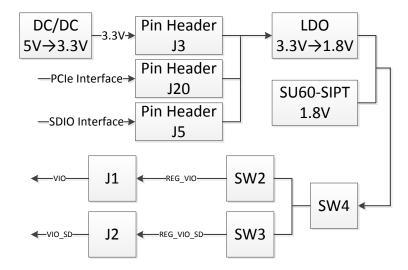

SDIO 2.0 supports both 1.8v and 3.3v in VIO. The following is the block diagram for the 1.8/3.3v power switching on the DVK-ST60-SIPT/DVK-SU60-SIPT board.

Americas: +1-800-492-2320 Europe: +44-1628-858-940 Hong Kong: +852 2923 0610

**Application Note**

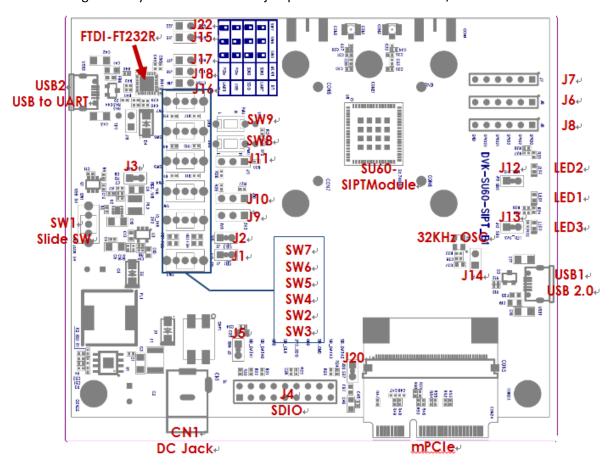

The following is the layout of switches and jumpers on the DVK-ST60-SIPT/DVK-SU60-SIPT board.

Hong Kong: +852 2923 0610

**Application Note**

A VIO 3.3v host platform requires the following switch and jumper settings:

- J11: Left (located near USB2)

- J10: Right (located near SIP)

- J9: Right (located near SIP)

- Switch 4: Right (located near SIP)

- Switch 2: Left (located near USB2)

- Switch 3: Left (located near USB2)

A VIO 1.8v host platform requires the following switch and jumper settings:

- J11: Left (located near USB2)

- J10: Right (located near SIP)

- J9: Left (located near USB2)

- Switch 4: Right (located near SIP)

- Switch 2: Right (located near SIP)

- Switch 3: Right (located near SIP)

There are several Wi-Fi/BT interface support options on the DVK-ST60-SIPT/DVK-SU60-SIPT board.

Table 1: Wi-Fi/BT interface support options for SDIO 2

| Wi-Fi | BT   | Switch 7                 | Switch 6                 | Switch 5                 |

|-------|------|--------------------------|--------------------------|--------------------------|

| SDIO  | UART | Left (located near USB2) | Left (located near USB2) | Left (located near USB2) |

| SDIO  | SDIO | Left (located near USB2) | Left (located near USB2) | Right (located near SIP) |

| PCle  | USB  | Left (located near USB2) | Right (located near SIP) | Left (located near USB2) |

| PCle  | UART | Left (located near USB2) | Right (located near SIP) | Right (located near SIP) |

Americas: +1-800-492-2320 Europe: +44-1628-858-940 Hong Kong: +852 2923 0610

**Application Note**

#### **ENVIRONMENT SETUP WITH SDIO 3.0 HOST**

## **DVK-ST60-SIPT/DVK-SU60-SIPT Wiring**

With an SDIO 3.0 host, the Laird module runs in SDR104 mode. An SDIO clock is much faster than SDIO 2.0 and it is more sensitive with a bus signal.

To wire the DVK-ST60-SIPT/DVK-SU60-SIPT with SDIO 3.0 host, follow these steps to prevent a driver loading failure due to a poor SDIO signal:

Mount the SDIO extender board without pin header on the DVK-ST60-SIPT/DVK-SU60-SIPT SDIO connector. Align the pin closest to the PCI-E bus with the SD\_D1 pin of SDIO extender board

2. Solder each pin of the SDIO extender board.

Americas: +1-800-492-2320

Europe: +44-1628-858-940

Hong Kong: +852 2923 0610

**Application Note**

3. Connect the two antennas to the u.FL connectors on the DVK-ST60-SIPT/DVK-SU60-SIPT board.

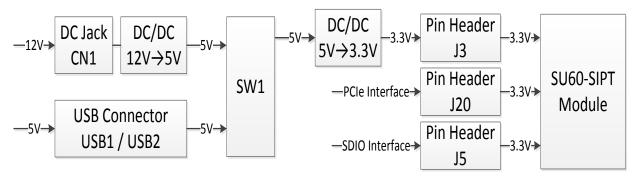

The development board can be powered from DC 12V supply (into DC jack connector CN1), USB (type micro-B) connector (USB1 and USB2), or the host interface (SDIO interface).

For regular usage, the power from SDIO bus should be enough with no need for external power from either the DC jack or USB port. To run continuous TX in a regulation test, the host may not be able to support enough current via the SDIO and may need external power.

**Application Note**

# DVK-ST60-SIPT/DVK-SU60-SIPT Board Switch and Jumper Setup

SDIO 3.0 bus only supports VIO 1.8v and requires the following switch and jumper settings:

- J11: Left (located near USB2)

- J10: Right (located near SIP)

- J9: Left (located near USB2)

- Switch 4: Right (located near SIP)

- Switch 2: Right (located near SIP)

- Switch 3: Right (located near SIP)

There are several options of Wi-Fi/BT interface support in DVK-ST60-SIPT/DVK-SU60-SIPT board.

Table 2: Wi-Fi/BT interface support options for SDIO 3

| Wi-Fi | BT   | Switch 7                 | Switch 6                 | Switch 5                 |

|-------|------|--------------------------|--------------------------|--------------------------|

| SDIO  | UART | Left (located near USB2) | Left (located near USB2) | Left (located near USB2) |

| SDIO  | SDIO | Left (located near USB2) | Left (located near USB2) | Right (located near SIP) |

| PCle  | USB  | Left (located near USB2) | Right (located near SIP) | Left (located near USB2) |

| PCle  | UART | Left (located near USB2) | Right (located near SIP) | Right (located near SIP) |

#### **REVISION HISTORY**

| Version | Date         | Notes                                                                     | Approver    |

|---------|--------------|---------------------------------------------------------------------------|-------------|

| 1.0     | 07 Sept 2017 | Initial release                                                           | Jay White   |

| 1.1     | 20 Sept 2017 | Updated Table 1 and 2 – Reversed the Switch 5 and Switch 7 column headins | Miles Chung |