HOTON IS OUR BUSINESS

# **Profile sensor**

S9132

## High-speed frame rate sensor capable of acquiring two-dimensional projection data

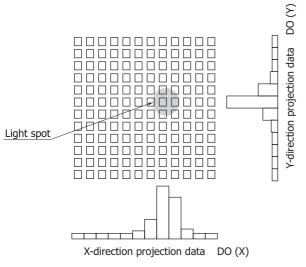

The profile sensor S9132 is a high-performance CMOS area sensor particularly intended to acquire projection data. A projection profile in the X and Y directions has very small amounts of data compared to normal area sensors and therefore allows high-speed position detection and moving object detection. The S9132 also has advantages over convensional 2D PSDs (Position Sensitive Detectors) that the output linearity is improved, multiple light spots can be detected and external circuits are simplified. A timing generator, bias voltage generator and 10-bit AD converter circuits are all integrated on the same chip, allowing operations with a very simple external driver circuit and external signal processing circuit.

#### Features

- Sensor for acquiring 2D projection data

- High-speed frame rate: 3200 frames/s max. (8-bit) 1600 frames/s max. (10-bit)

- **▶** Low power consumption

- Digital video output

- **10-bit/8-bit switchable ADC**

#### Applications

- Light spot position detection (printers, FA inspection equipment, amusement machines)

- Moving object detection (FA inspection equipment, amusement machines)

- 3D measurement (FA inspection equipment, medical measurement)

#### Conceptual view of light spot detection

KMPDC0168EA

#### Structure

| Parameter           | Value           | Unit |

|---------------------|-----------------|------|

| Number of pixels    | 256 × 256       | -    |

| Pixel pitch         | 7.8             | μm   |

| Photosensitive area | 1.9968 × 1.9968 | mm   |

| Package             | Ceramic         | -    |

| Window material     | Tenpax          | mm   |

## **■** Absolute maximum ratings

| Parameter                       | Symbol | Value      | Unit |

|---------------------------------|--------|------------|------|

| Analog supply voltage           | Vdd(A) | -0.3 to +6 | V    |

| Digital supply voltage          | Vdd(D) | -0.3 to +6 | V    |

| Gain selection terminal voltage | Vg     | -0.3 to +6 | V    |

| AD mode selection voltage       | Vsel   | -0.3 to +6 | V    |

| Clock pulse voltage             | V(clk) | -0.3 to +6 | V    |

| Start pulse voltage             | V(st)  | -0.3 to +6 | V    |

| Operating temperature*1         | Topr   | -5 to +65  | °C   |

| Storage temperature*1           | Tstg   | -10 to +85 | °C   |

<sup>\*1:</sup> No condensation

#### **⇒** Recommended terminal voltage

| Parameter                       |                          | Symbol | Min.          | Тур.   | Max.          | Unit |

|---------------------------------|--------------------------|--------|---------------|--------|---------------|------|

| Analog supply voltage           |                          | Vdd(A) | 4.75          | 5      | 5.25          | V    |

| Digital supply voltage*2        | Digital supply voltage*2 |        | 3             | 5      | Vdd(A)        | V    |

| Cain coloction terminal voltage | High gain                | Va     | 0             | 0 -    | 0.4           | V    |

| Gain selection terminalvoltage  | Low gain                 | Vg     | Vdd(A) - 0.25 | Vdd(A) | Vdd(A) + 0.25 |      |

| AD mode selectionvoltage        | 10-bit mode              | Vsel   | Vdd(A) - 0.25 | Vdd(A) | Vdd(A) + 0.25 | V    |

| AD Mode Selectionvoltage        | 8-bit mode               |        | 0             | -      | 0.4           |      |

| Clock pulse voltage             | High level               | V(clk) | Vdd(D) - 0.25 | Vdd(D) | Vdd(D) + 0.25 | V    |

| Clock pulse voltage             | Low level                | V(CIK) | 0             | -      | 0.4           | V    |

| Start pulse voltage             | High level               | \/(ct) | Vdd(D) - 0.25 | Vdd(D) | Vdd(D) + 0.25 | V    |

|                                 | Low level                | V(st)  | 0             | -      | 0.4           |      |

<sup>\*2:</sup> When the latter-stage digital processing circuit is a 3.3 V family, the high level of digital output signal is 3.3 V when operated at Vdd(A)=5 V, Vdd(D)=3.3 V.

## **■** Electrical characteristics (Ta=25 °C)

| Parameter                |             | Symbol | Min.          | Тур.      | Max. | Unit |

|--------------------------|-------------|--------|---------------|-----------|------|------|

| Clock pulse frequency*3  | 10-bit MODE | f(clk) | 500           | -         | 5 M  | Hz   |

| Clock pulse frequency    | 8-bit MODE  |        | 500           | -         | 10 M |      |

| Video data rate          |             | VR     | -             | f(clk)/12 | -    | Hz   |

| Digital output voltage   | High level  | VDO(H) | Vdd(D) - 0.15 | -         | -    | V    |

|                          | Low level   | VDO(L) | -             | -         | 0.15 |      |

| Digital output rise time | CL=10 pF    | +      | -             | -         | 30   | 20   |

| (10 to 90%)*4            | CL=30 pF    | tr     | -             | -         | 60   | ns   |

| Digital output fall time | CL=10 pF    | ıc     | -             | -         | 30   |      |

| (10 to 90%)*4            | CL=30 pF    | tf     | -             | -         | 60   | ns   |

| Power consumption*5      |             | Р      | -             | 75        | -    | mW   |

<sup>\*3:</sup> Vdd(A)=Vdd(D)=5 V, V(clk)=V(st)=5 V, Vg=5 V (Low gain)

<sup>\*4:</sup> CL: Load capacitance of digital output terminal

<sup>\*5:</sup> Vdd(A)=Vdd(D)=5 V, V(clk)=V(st)=V(st)=5 V, f(clk)=5 MHz, f(st)=1.5 kHz

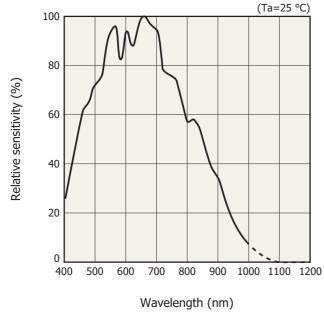

## **=** Electrical and optical characteristics [Ta=25 °C, Vdd(A)=Vdd(D)=5 V, V(clk)=V(st)=5 V]

| Paramete                  | r                               | Symbol | nbol Min. Typ. |             | Max. | Unit  |

|---------------------------|---------------------------------|--------|----------------|-------------|------|-------|

| Spectral response range   |                                 | λ      |                | 380 to 1000 |      |       |

| Peak sensitivity wavelen  | gth                             | λр     | -              | 650         | -    | nm    |

| Photo sensitivity*6       | High gain                       | DEC    | -              | 40          | -    | \//1  |

| FIIOLO SCIISILIVILY       | Low gain                        | RES    | -              | 8           | -    | V/nJ  |

| Dark current              |                                 | ID     | -              | 0.2         | 0.6  | рА    |

| Saturation charge         |                                 | Qsat   | -              | 8           | -    | pC    |

| Feedback capacitanceof    | High gain                       | Cf     | -              | 0.2         | -    | pF    |

| charge amplifier*7        | Low gain                        | 1 (1   | -              | 1           | -    |       |

| Dark output voltage*8     | High gain                       |        | -              | 100         | 300  | m)/   |

| Dark output voitage       | Low gain                        | ] Vu   | -              | 20          | 60   | - mV  |

| Saturation output voltage | High gain                       | Vsat   | 2.5            | 3.5         | -    | V     |

|                           | Low gain                        | VSdL   | 2.5            | 3           | -    | \ \ \ |

| Photo response nonunifo   | o response nonuniformity*9 PRNU |        | -              | -           | ±10  | %     |

<sup>\*6:</sup> Vg=5 V (Low gain), Vg=0 V (High gain)

## Spectral response (typical example)

KMPDB0231E

#### **→** A/D converter characteristics (Ta=25 °C)

| Par                           | Parameter   |      | Value         | Unit  |

|-------------------------------|-------------|------|---------------|-------|

| Digital output format         |             | -    | Serial output | -     |

| Resolution*10                 | 10-bit mode | RESO | 10            | bit   |

| Resolution                    | 8-bit mode  | KESU | 8             | ] DIL |

| Conversion time               |             | tCON | 12/f(clk)     | s/ch  |

| Frame readout time            |             | FR   | 3100/f(clk)   | s/f   |

| Conversion voltage range*11 - |             | -    | 0 to 3.8      | V     |

<sup>\*10:</sup> Vsel=5 V (10-bit mode), Vsel=0 V (8-bit mode)

10-bit mode: D9 to D0 8-bit mode: D7 to D0

<sup>\*7:</sup> λ=780 nm

<sup>\*8:</sup> Storage time Ts=100 ms

<sup>\*9:</sup> Uniformity is defined under the condition that the device is uniformly illuminated by light which is 50% of the saturation exposure level and using 254 pixels excluding both ends pixels as follows:  $PRNU = \Delta V/V \times 100$  (%)

X: the average output of all pixels,  $\Delta X$ : the difference from the maximum or minimum output and X

<sup>\*11:</sup> Digital output is available from MSB as serial output.

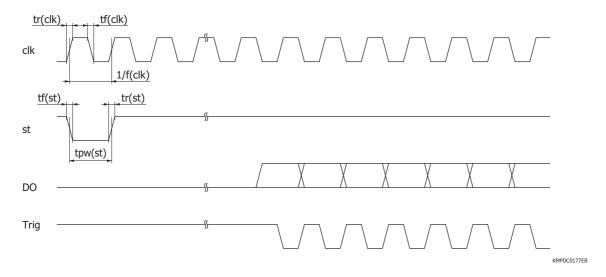

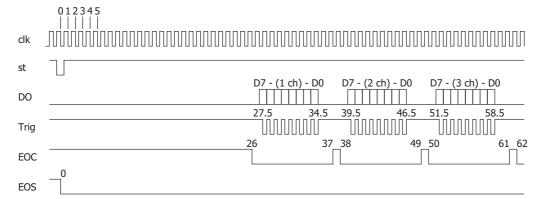

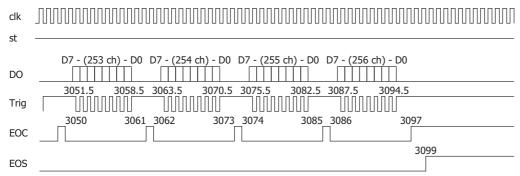

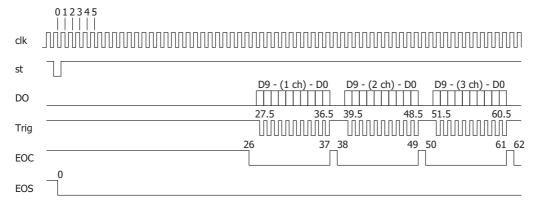

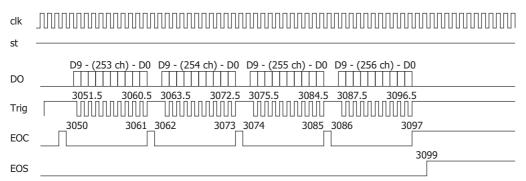

## Timing chart

| Parameter                      | Symbol           | Min.        | Тур. | Max. | Unit |

|--------------------------------|------------------|-------------|------|------|------|

| Start pulse interval           | T(st)            | 3101/f(clk) | -    | -    | S    |

| Clock pulse duty ratio         | -                | 45          | 50   | 55   | %    |

| Clock pulse rise and fall time | tr(clk), tf(clk) | 0           | 20   | 30   | ns   |

| Start pulse width              | tpw(st)          | 90          | -    | -    | ns   |

| Start pulse rise and fall time | tr(st), tr(st)   | 0           | 20   | 30   | ns   |

Note: Operation in the X and Y directions can be performed independently.

The internal timing circuit starts operating at the fall timing of the clock pulse immediately after the start pulse goes "Low".

It doesn't matter how many times the clock pulse goes "Low" during the "Low" period of the start pulse.

The storage time is determined by the start pulse intervals. However, scince the charge storage of each pixel is carried out between the signal readout of that pixel and the next signal readout of the same pixel, the start time of charge storage differs depending on each pixel. In addition, the next start pulse cannot be input until signal readout from all pixels is completed.

The above timing chart applies to operation at 5 MHz. If operated at 10 MHz, the DO, Trig and EOC timings may delay by half a clock cycle.

#### 8-bit mode

• In the neighborhood of start pixel

• In the neighborhood of last pixel

KMPDC0173EA

#### 10-bit mode

• In the neighborhood of start pixel

• In the neighborhood of last pixel

KMPDC0174EA

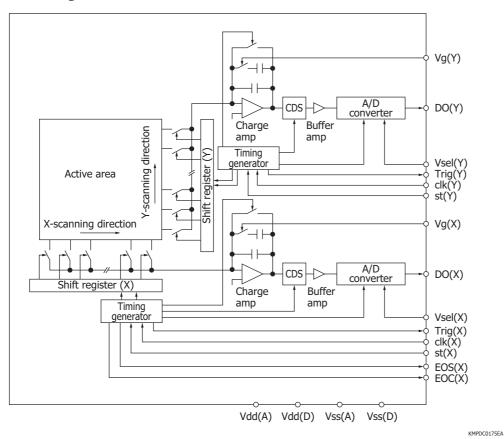

#### **Block diagram**

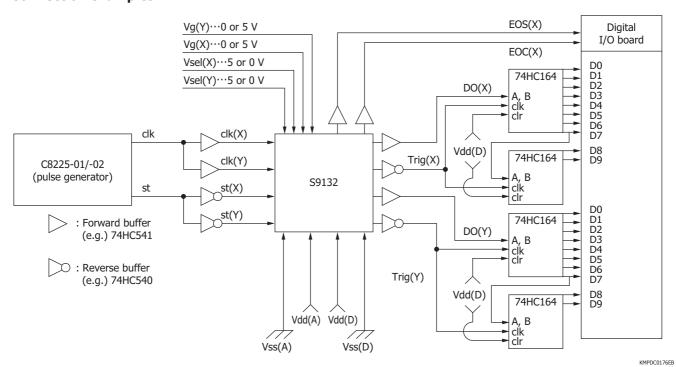

#### - Connection examples

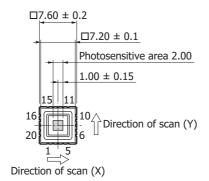

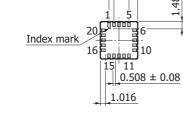

## Dimensional outline (unit: mm)

- \*1: Length from upper surface of window to photosensitive surface \*2: Length from bottom surface of package to photosensitive surface

KMPDA0174EC

| Pin no. | Symbol  | I/O | Function                  |

|---------|---------|-----|---------------------------|

| 1       | Vsel(X) | I   | AD mode selection voltage |

| 2       | Vg(X)   | I   | Gain selection voltage    |

| 3       | st(X)   | I   | Start pulse               |

| 4       | clk(X)  | I   | Clock pulse               |

| 5       | EOS(X)  | 0   | End of scan pulse         |

| 6       | clk(Y)  | I   | Clock pulse               |

| 7       | st(Y)   | I   | Start pulse               |

| 8       | Vdd(A)  | I   | Analog supply voltage     |

| 9       | Vg(Y)   | I   | Gain selection voltage    |

| 10      | Vsel(Y) | I   | AD mode selection voltage |

| 11      | Vss(A)  | I   | Analog ground             |

| 12      | Vss(D)  | I   | Digital ground            |

| 13      | Trig(Y) | 0   | Trigger pulse             |

| 14      | DO(Y)   | 0   | Digital output            |

| 15      | Vdd(D)  | I   | Digital supply voltage    |

| 16      | NC      |     | No connection             |

| 17      | DO(X)   | 0   | Digital output            |

| 18      | Trig(X) | 0   | Trigger pulse             |

| 19      | EOC(X)  | 0   | End of conversion pulse   |

| 20      | Vss(A)  | I   | Analog ground             |

Profile sensor mounted on terminal pitch conversion board S9132-01

S9132-01 is a profile sensor mounted on a terminal pitch conversion board having 1-inch (2.54 mm) pitch output terminals.

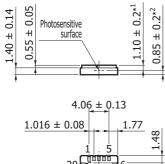

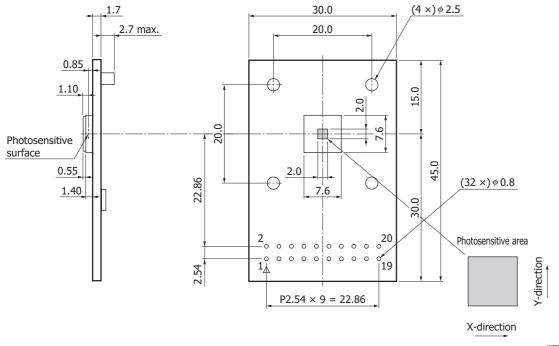

## Dimensional outline (unit: mm)

KMPDA0180EC

| Pin no. | Symbol  | I/O | Function                  |

|---------|---------|-----|---------------------------|

| 1       | Vsel(X) | I   | AD mode selection voltage |

| 2       | Vg(X)   | I   | Gain selection voltage    |

| 3       | st(X)   | I   | Start pulse               |

| 4       | clk(X)  | I   | Clock pulse               |

| 5       | EOS(X)  | 0   | End of scan pulse         |

| 6       | clk(Y)  | I   | Clock pulse               |

| 7       | st(Y)   | I   | Start pulse               |

| 8       | Vdd(A)  | I   | Analog supply voltage     |

| 9       | Vg(Y)   | I   | Gain selection voltage    |

| 10      | Vsel(Y) | I   | AD mode selection voltage |

| 11      | Vss(A)  | I   | Analog ground             |

| 12      | Vss(D)  | I   | Digital ground            |

| 13      | Trig(Y) | 0   | Trigger pulse             |

| 14      | DO(Y)   | 0   | Digital output            |

| 15      | Vdd(D)  | I   | Digital supply voltage    |

| 16      | NC      |     | No connection             |

| 17      | DO(X)   | 0   | Digital output            |

| 18      | Trig(X) | 0   | Trigger pulse             |

| 19      | EOC(X)  | 0   | End of conversion pulse   |

| 20      | Vss(A)  | I   | Analog ground             |

#### Precautions during use

#### (1) Electrostatic countermeasures

This device has a built-in protection circuit against static electrical charges. However, to prevent destroying the device with electrostatic charges, take countermeasures such as grounding yourself, the workbench and tools to prevent static discharges. Also protect this device from surge voltages which might be caused by peripheral equipment.

#### (2) Incident window

If dust or dirt gets on the light incident window, it will show up as black blemishes on the image. When cleaning, avoid rubbing the window surface with dry cloth or dry cotton swab, since doing so may generate static electricity. Use soft cloth, paper or a cotton swab moistened with alcohol to wipe dust and dirt off the window surface. Then blow compressed air onto the window surface so that no spot or stain remains.

#### (3) Soldering by hand

To prevent damaging the device during soldering, take precautions to prevent excessive soldering temperatures and times. Soldering should be performed within 5 seconds at a soldering temperature below 260 °C.

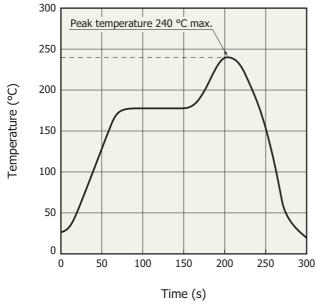

#### (4) Reflow soldering

Soldering conditions may differ depending on the board size, reflow furnace, etc. Check the conditions before soldering. A sudden temperature rise and cooling may be the cause of trouble, so make sure that the temperature change is within 4 °C per second. The bonding portion between the ceramic base and the glass may discolor after reflow soldering, but this has no adverse effects on the hermetic sealing of the product.

#### (5) UV exposure

This product is not designed to prevent deterioration of characteristics caused by UV exposure, so do not expose it to UV light.

#### Recommended solder reflow condition

KAPDB0169EA

Information described in this material is current as of December, 2011.

Product specifications are subject to change without prior notice due to improvements or other reasons. Before assembly into final products, please contact us for the delivery specification sheet to check the latest information.

Type numbers of products listed in the delivery specification sheets or supplied as samples may have a suffix "(X)" which means preliminary specifications or a suffix "(Z)" which means developmental specifications.

The product warranty is valid for one year after delivery and is limited to product repair or replacement for defects discovered and reported to us within that one year period. However, even if within the warranty period we accept absolutely no liability for any loss caused by natural disasters or improper product use.

Copying or reprinting the contents described in this material in whole or in part is prohibited without our prior permission.

## HAMAMATSU

www.hamamatsu.com

HAMAMATSU PHOTONICS K.K., Solid State Division

1126-1 Ichino-cho, Higashi-ku, Hamamatsu City, 435-8558 Japan, Telephone: (81) 53-434-3311, Fax: (81) 53-434-5184

U.S.A.: Hamamatsu Corporation: 360 Footbill Road, P.O.Box 6910, Bridgewater, N.J. 08807-0910, U.S.A., Telephone: (1) 908-231-0960, Fax: (1) 908-231-1218

Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, D-82211 Herrsching am Ammersee, Germany, Telephone: (49) 8152-375-0, Fax: (49) 8152-265-8

France: Hamamatsu Photonics France S.A.R.L.: 19, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: 33-(1) 69 53 71 00, Fax: 33-(1) 69 53 71 10

United Kingdom: Hamamatsu Photonics UK Limited: 2 Howard Court, 10 Tewin Road, Welwyn Garden City, Hertfordshire AL7 1BW, United Kingdom, Telephone: (44) 1707-294888, Fax: (44) 1707-325777

North Europe: Hamamatsu Photonics Norden AB: Smidesvägen 12, SE-171 41 Solna, Sweden, Telephone: (49) 8-509-031-001

Italy: Hamamatsu Photonics Italia S.R.L.: Strada della Moia, 1 int. 6, 20020 Arese, (Milano), Italy, Telephone: (39) 02-935-81-733, Fax: (39) 02-935-81-741

China: Hamamatsu Photonics (China) Co., Ltd.: 1201 Tower B, Jiaming Center, No.27 Dongsanhuan Beilu, Chaoyang District, Beijing 100020, China, Telephone: (86) 10-6586-6006, Fax: (86) 10-6586-2866