### **Product Change Notification - SYST-24DUVO623**

Date:

25 Jan 2019

**Product Category:**

16-Bit - Microcontrollers and Digital Signal Controllers

Affected CPNs:

|大||登|

Notification subject:

ERRATA - PIC24FJ128GA310 Family Errata

**Notification text:**

SYST-24DUVO623

Microchip has released a new DeviceDoc for the PIC24FJ128GA310 Family Errata of devices. If you are using one of these devices please read the document located at <a href="PIC24FJ128GA310">PIC24FJ128GA310</a> Family Errata.

**Notification Status:** Final

**Description of Change:** Added silicon issue 15

Impacts to Data Sheet: None

**Reason for Change:** To Improve Productivity

**Change Implementation Status: Complete**

**Date Document Changes Effective: 25 Jan 2019**

**NOTE:** Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A Attachment(s):

71114011110111(0)1

PIC24FJ128GA310 Family Errata

Please contact your local <u>Microchip sales office</u> with questions or concerns regarding this notification.

#### **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN home page</u> select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section.

If you wish to <u>change your PCN profile, including opt out,</u> please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.

#### Affected Catalog Part Numbers (CPN)

PIC24FJ128GA306-I/MR

PIC24FJ128GA306-I/PT

PIC24FJ128GA306-I/PTC06

PIC24FJ128GA306-I/PTC09

PIC24FJ128GA306-I/PTREL

PIC24FJ128GA306T-I/MR

PIC24FJ128GA306T-I/PT

PIC24FJ128GA306T-I/PT025

PIC24FJ128GA306T-I/PTC02

PIC24FJ128GA308-I/PT

PIC24FJ128GA308-I/PTC03

PIC24FJ128GA308T-I/PT

PIC24FJ128GA310-I/BG

PIC24FJ128GA310-I/PF

PIC24FJ128GA310-I/PT

PIC24FJ128GA310-I/PTC04

PIC24FJ128GA310-I/PTC09

PIC24FJ128GA310-I/PTREL

PIC24FJ128GA310T-I/BG

PIC24FJ128GA310T-I/PT

PIC24FJ64GA306-I/MR

PIC24FJ64GA306-I/PT

PIC24FJ64GA306-I/PTC08

PIC24FJ64GA306-I/PTREL

PIC24FJ64GA306T-I/MR

PIC24FJ64GA306T-I/MR024

PIC24FJ64GA306T-I/PT

PIC24FJ64GA308-I/PT

PIC24FJ64GA308T-I/PT

PIC24FJ64GA310-I/BG

PIC24FJ64GA310-I/BGC07

PIC24FJ64GA310-I/PF

PIC24FJ64GA310-I/PT

PIC24FJ64GA310-I/PTC10

PIC24FJ64GA310-I/PTREL

PIC24FJ64GA310T-I/BG

PIC24FJ64GA310T-I/PT

Date: Thursday, January 24, 2019

## PIC24FJ128GA310 Family Silicon Errata and Data Sheet Clarification

The PIC24FJ128GA310 family devices that you have received conform functionally to the current Device Data Sheet (DS30009996 $\mathbf{G}$ ), except for the anomalies described in this document.

The silicon issues discussed in the following pages are for silicon revisions with the Device and Revision IDs listed in Table 1. The silicon issues are summarized in Table 2.

The errata described in this document will be addressed in future revisions of the PIC24FJ128GA310 family silicon.

Note: This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated in the last column of Table 2 apply to the current silicon revision (C0).

Data Sheet clarifications and corrections start on Page 7, following the discussion of silicon issues.

The silicon revision level can be identified using the current version of MPLAB® IDE and Microchip's programmers, debuggers and emulation tools, which are available at the Microchip corporate website (www.microchip.com).

For example, to identify the silicon revision level using MPLAB IDE in conjunction with MPLAB ICD 2 or PICkit™ 3:

- Using the appropriate interface, connect the device to the MPLAB ICD 2 programmer/ debugger or PICkit™ 3.

- 2. From the main menu in MPLAB IDE, select <u>Configure>Select Device</u>, and then select the target part number in the dialog box.

- 3. Select the MPLAB hardware tool (*Debugger>Select Tool*).

- Perform a "Connect" operation to the device (<u>Debugger>Connect</u>). Depending on the development tool used, the part number and Device Revision ID value appear in the **Output** window.

**Note:** If you are unable to extract the silicon revision level, please contact your local Microchip sales office for assistance.

The DEVREV values for the various PIC24FJ128GA310 family silicon revisions are shown in Table 1.

TABLE 1: SILICON DEVREV VALUES

| Part Number     | Device ID <sup>(1)</sup> | Revision ID for<br>Silicon Revision <sup>(2)</sup> |    |  |

|-----------------|--------------------------|----------------------------------------------------|----|--|

|                 |                          | B2                                                 | C0 |  |

| PIC24FJ64GA306  | 46C0h                    |                                                    |    |  |

| PIC24FJ64GA308  | 46C4h                    |                                                    |    |  |

| PIC24FJ64GA310  | 46C8h                    | ]                                                  |    |  |

| PIC24FJ128GA306 | 46C2h                    | 4                                                  | 6  |  |

| PIC24FJ128GA308 | 46C6h                    |                                                    |    |  |

| PIC24FJ128GA310 | 46CAh                    |                                                    |    |  |

- **Note 1:** The Device IDs (DEVID and DEVREV) are located at the last two implemented addresses of configuration memory space. They are shown in hexadecimal in the format, "DEVID DEVREV".

- **2:** Refer to the "PIC24FJXXXDA1/DA2/GB2/GA3/GC0 Families Flash Programming Specification" (DS39970) for detailed information on Device and Revision IDs for your specific device.

TABLE 2: SILICON ISSUE SUMMARY

| Module            | Feature                            | Item   | Issue Summary                                                                                |    | ected<br>ions <sup>(1)</sup> |

|-------------------|------------------------------------|--------|----------------------------------------------------------------------------------------------|----|------------------------------|

|                   |                                    | Number | -                                                                                            | B2 | C0                           |

| A/D               | Threshold<br>Detect                | 1.     | Auto-scan feature may not trigger correctly in Sleep mode.                                   | Х  |                              |

| A/D               | Threshold<br>Detect                | 2.     | In Auto-Scan mode, the highest number A/D channel may not cause an interrupt.                | Х  |                              |

| A/D               | Accuracy                           | 3.     | Noise injection on A/D input pin during A/D operation (when reading a high-impedance input). | Х  | Х                            |

| Core              | VBAT mode                          | 4.     | VBTBOR (CW3<7>) is not functional.                                                           | Х  | Х                            |

| RTCC              | _                                  | 5.     | During a Power-on Reset, the RTCC may be enabled.                                            | Х  |                              |

| A/D               | DNL                                | 6.     | DNL will not meet data sheet specifications and possible missing codes.                      | Х  |                              |

| Core              | Deep Sleep                         | 7.     | IPD maximum numbers are higher than in the data sheet.                                       | Х  | Х                            |

| A/D               | DMA PIA<br>Mode                    | 8.     | DMA with A/D in PIA mode will not work.                                                      | Х  |                              |

| Reset             | Low-Voltage/<br>Retention<br>Sleep | 9.     | POR and BOR bits may get set after Reset.                                                    | Х  | Х                            |

| A/D               | _                                  | 10.    | Band gap input (VBG/2) is not functional.                                                    | Х  | Х                            |

| Reset             | VBAT and POR                       | 11.    | POR failure without proper voltage on VBAT pin.                                              | Х  |                              |

| LCD               | SEG37                              | 12.    | LCD pin, SEG37, does not work on 80-pin devices.                                             | Х  | Х                            |

| Power-on<br>Reset | POR                                | 13.    | Power-on Reset is not getting re-initialized.                                                | Х  | Х                            |

| Core              | Sleep                              | 14.    | Address trap may occur in Sleep mode with VREGS (RCON<8>) = 1 when the system clock is FRC.  | Х  | Х                            |

| Core              | Low-Voltage/<br>Retention<br>Sleep | 15.    | If the device is woken immediately after a Retention Sleep, the device may get a Reset.      | Х  | Х                            |

**Note 1:** Only those issues indicated in the last column apply to the current silicon revision.

#### Silicon Errata Issues

**Note:** Corrections are shown in bold. Where possible, the original bold text formatting.

#### 1. Module: A/D (Threshold Detect)

When the auto-scan feature of the Threshold Detect is enabled (AD1CON5<15> = 1), the automatic scan may fail when these conditions occur together:

- · The Device is in Sleep mode, and

- Timer1 is selected as the sample trigger clock source (AD1CON1<7:4> = 0110).

Timer1 and other timers will function correctly as sample triggers in other power-saving modes, such as Idle mode.

#### Work around

Use INT0 to trigger the A/D in Sleep mode.

#### **Affected Silicon Revisions**

| B2 | CO |  |  |  |

|----|----|--|--|--|

| Х  |    |  |  |  |

#### 2. Module: A/D (Threshold Detect)

In Auto-Scan mode (AD1CON5<15> = 1), when the Auto-Scan Interrupt mode bits are set to '11' (AD1CON5<9:8> = 11), the highest number channel selected for scanning in AD1CSSL, or AD1CSSH, may not trigger an interrupt on a valid comparison.

#### Work around

Add a dummy channel to the scanning sequence. For example, when scanning AN0 and AN1, set AD1CSSL to 0x0007 or 0x8003, or whatever is practical given the implementation.

Also, if the highest number channel needs to be scanned, the AD1CHITH register bits can be polled to observe a valid comparison.

#### **Affected Silicon Revisions**

| B2 | C0 |  |  |  |

|----|----|--|--|--|

| Х  |    |  |  |  |

#### 3. Module: A/D (Accuracy)

Noise injection on the A/D input pin during A/D operation (when reading a high-impedance input) may adversely affect the conversion results.

#### Work around

Increase the sample time for the channel that is being converted or reduce the source impedance.

#### **Affected Silicon Revisions**

| B2 | CO |  |  |  |

|----|----|--|--|--|

| Χ  | Χ  |  |  |  |

#### 4. Module: Core (VBAT Mode)

VBTBOR (CW3<7>) will not work correctly. The behavior of this bit is different in Revision B2 and C0.

In Revision B2, it does not matter if this bit (CW3<7>) is '1' or '0', the feature will not work.

In Revision C0, the feature is available but may not work correctly, so it is recommended to maintain CW3<7> = 0 to disable the VBTBOR. If the bit is maintained as '1', the RTCC may be reset above VBT voltage (1.6V).

#### Work around

The application can monitor the VBAT voltage using ADC after a POR in VBAT mode. The ADC is internally connected to VBAT to measure VBAT/2 (CH0SB<4:0>= 11111).

The VBAT can be monitored using ADC, and if the VBAT has gone below VBT (1.6V), RTCC needs to be reconfigured with the correct date and time.

| B2 | C0 |  |  |  |

|----|----|--|--|--|

| Х  | Х  |  |  |  |

#### 5. Module: RTCC

During a Power-on Reset, the RTCC may be enabled.

#### Work around

To ensure that the RTCC is not enabled, make sure to clear the RTCEN bit after a POR. This is recommended whether RTCC is used or not.

After a POR, execute the code shown in Example 1 to disable the RTCC.

#### Affected Silicon Revisions

| B2 | C0 |  |  |  |

|----|----|--|--|--|

| Х  |    |  |  |  |

#### **EXAMPLE 1: DISABLING THE RTCC FOLLOWING POR**

| MOV    | #NVMKEY,    | W1   | ; move the address of NVMKEY into W1 |

|--------|-------------|------|--------------------------------------|

| MOV    | #0x55,      | W2   |                                      |

| MOV    | W2,         | [W1] | ;start 55/AA sequence                |

| MOV    | #0xAA,      | W3   |                                      |

| MOV    | W3,         | [W1] |                                      |

| BSET   | RCFGCAL,    | #13  | ;set the RTCWREN bit                 |

| RCFGCA | Lbits.RTCEN | I=0; |                                      |

#### 6. Module: A/D

The DNL will not meet the data sheet specification; the DNL will be  $\leq$ 1.5. There may be possible missing codes in 12-bit mode in locations: 511, 1023, 1535, 2047, 2559, 3071, 3583.

#### Work around

None.

#### **Affected Silicon Revisions**

| B2 | C0 |  |  |  |

|----|----|--|--|--|

| Χ  |    |  |  |  |

#### 7. Module: Core (Deep Sleep)

The IPD maximum number for Deep Sleep may not meet the data sheet specification (DC70).

The maximum value for Deep Sleep at 3.3V will be 6  $\mu$ A.

#### Work around

None.

#### **Affected Silicon Revisions**

| B2 | C0 |  |  |  |

|----|----|--|--|--|

| Χ  | Χ  |  |  |  |

#### 8. Module: A/D

The A/D will not work with DMA in PIA mode.

#### Work around

None.

#### **Affected Silicon Revisions**

| B2 | C0 |  |  |  |

|----|----|--|--|--|

| Χ  |    |  |  |  |

#### 9. Module: Reset

When the device is in Low-Voltage/Retention Sleep mode (Sleep with CW1<10> = 0 and RETEN = 1), if a Master Clear Reset is given, the POR (RCON<0>) and BOR (RCON<1>) bits may get set after the Reset.

#### Work around

Use registers, such as DSGPR0 or DSGPR1, to indicate the device was in Low-Voltage/Retention Sleep mode before the MCLR Reset is given.

| B2 | C0 |  |  |  |

|----|----|--|--|--|

| Х  | Х  |  |  |  |

#### 10. Module: A/D

The internal VBG/2 input channel is not functional. When this input is selected as the channel to be converted, no conversion will occur and a device Reset will occur.

#### Work around

None.

#### **Affected Silicon Revisions**

| B2 | CO |  |  |  |

|----|----|--|--|--|

| Χ  | Χ  |  |  |  |

#### 11. Module: Reset (VBAT and POR)

For applications that use the VBAT feature, the device may fail to start/restart on POR if VBAT voltage is below 1.2V.

#### Work around

If the VBAT mode features will be used in the application, ensure that a VBAT source of at least 1.2V is always connected to the VBAT pin.

If the VBAT mode features are not to be used, always connect the VBAT pin to VDD, as recommended in the data sheet.

#### **Affected Silicon Revisions**

| B2 | CO |  |  |  |

|----|----|--|--|--|

| Χ  |    |  |  |  |

#### 12. Module: LCD

LCD segment, SEG37, will not function as an LCD segment pin. The issue only exists in the 80-pin devices (PIC24FJ128GA308 and PIC24FJ64GA308). The SEG37 pin works correctly on 100-pin devices.

#### Work around

None.

#### **Affected Silicon Revisions**

| B2 | CO |  |  |  |

|----|----|--|--|--|

| Χ  | Χ  |  |  |  |

#### 13. Module: Power-on Reset

When the device is operating with Brown-out Reset (BOR) disabled, it is recommended to follow the data sheet specification of starting the VDD from Vss to ensure an internal Power-on Reset. Failing to do so may result in the device failing to start up or other unexpected behavior.

#### Work around

There are three work arounds to resolve the issue:

- Enable the BOR to ensure that the device gets a proper Power-on Reset.

- If the BOR cannot be enabled, always start the VDD from Vss to ensure a proper Poweron Reset (Parameter No. DC16 in Table 32-3 of Section 32.0 "Electrical Characteristics" in the data sheet).

- 3. Use an external voltage supervisor chip on the MCLR pin to hold the MCLR low when the power supply voltage is between 1.4V and 2.0V. Release MCLR after the VDD is in the operating range.

#### Affected Silicon Revisions

| B2 | CO |  |  |  |

|----|----|--|--|--|

| Χ  | Χ  |  |  |  |

#### 14. Module: Core

In Sleep mode, with the following conditions:

- 1. Sleep mode with VREGS (RCON<8>) = 1 (for faster wake-up).

- 2. System clock is used as the FRC.

An address trap may occur if an interrupt wakes up the device immediately after executing the SLEEP instruction (within 500 ns).

#### Work around

There are two ways to resolve the issue:

- 1. Select the FRCDIV as the system clock and use the following steps:

- a) Before going to Sleep, change the clock divider to the slowest speed (RCDIV<2:0> (CLKDIV<10:8>) = 111).

- b) Execute the SLEEP instruction.

- c) When the interrupt wakes up the device, switch the FRCDIV to the required clock (RCDIV<2:0> (CLKDIV<10:8>) = required clock).

Repeat the above steps any time the device goes to Sleep and wakes up.

OR

2. Execute Sleep with VREGS (RCON<8>) = 0.

| B2 | C0 |  |  |  |

|----|----|--|--|--|

| Χ  | Х  |  |  |  |

#### 15. Module: Core

When the device wakes from a Low-Voltage/ Retention Sleep mode (Sleep with CW1<10> = 0 and RETEN = 1), if the wake-up event is within 1 ms after the SLEEP instruction, the device may go into Reset.

#### Work around

Enable the BOR to ensure that the device band gap is enabled during the Retention Sleep.

| B2 | CO |  |  |  |

|----|----|--|--|--|

| Χ  | Χ  |  |  |  |

#### **Data Sheet Clarifications**

The following typographic corrections and clarifications are to be noted for the latest version of the device data sheet (DS30009996**G**):

**Note:** Corrections are shown in **bold**. Where possible, the original bold text formatting has been removed for clarity.

#### 1. Module: Pin Diagrams

The following note has been added to the 64-Pin TQFP/QFN pin diagram on Page 3:

Note 2: It is recommended to connect the metal pad on the bottom of the 64-pin QFN package to Vss.

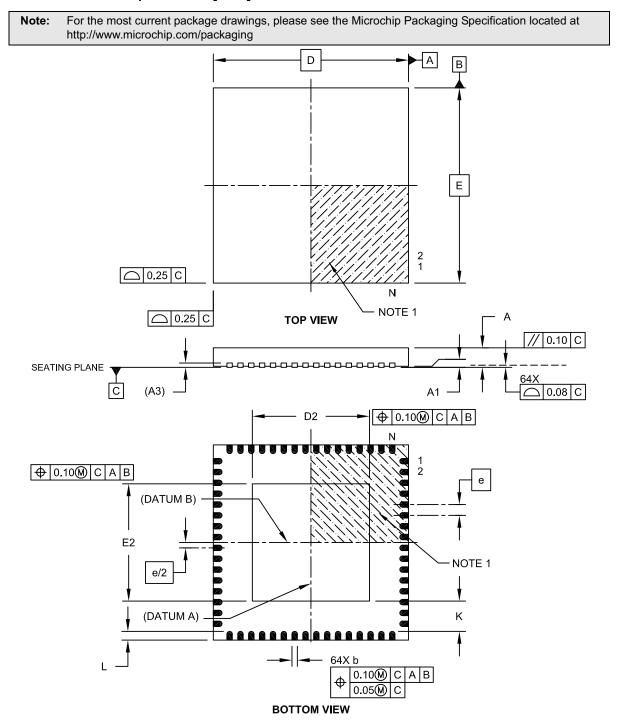

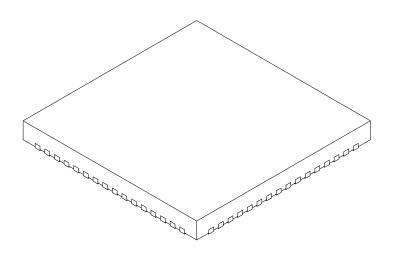

#### 2. Module: Packaging Information

The 64-Lead Plastic Quad Flat, No Lead Package (MR) drawings on Pages 391 through 393 have been replaced with the C04-154A package drawings shown below.

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2

## 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |          |          |      |  |  |

|------------------------|-------------|----------|----------|------|--|--|

| Dimension              | MIN         | NOM      | MAX      |      |  |  |

| Number of Pins         | N           |          | 64       |      |  |  |

| Pitch                  | е           |          | 0.50 BSC |      |  |  |

| Overall Height         | Α           | 0.80     | 0.90     | 1.00 |  |  |

| Standoff               | A1          | 0.00     | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3          | 0.20 REF |          |      |  |  |

| Overall Width          | Е           | 9.00 BSC |          |      |  |  |

| Exposed Pad Width      | E2          | 5.30     | 5.40     | 5.50 |  |  |

| Overall Length         | D           | 9.00 BSC |          |      |  |  |

| Exposed Pad Length     | D2          | 5.30     | 5.40     | 5.50 |  |  |

| Contact Width          | b           | 0.20     | 0.25     | 0.30 |  |  |

| Contact Length         | Ĺ           | 0.30     | 0.40     | 0.50 |  |  |

| Contact-to-Exposed Pad | K           | 0.20     | -        | -    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

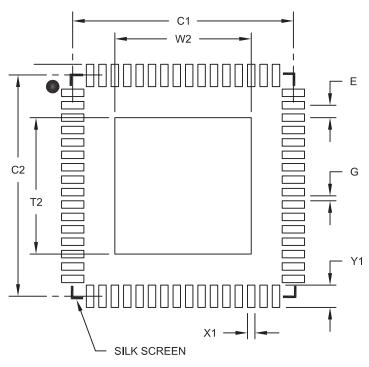

Microchip Technology Drawing C04-154A Sheet 2 of 2

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length and 5.40x5.40mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimension                  | MIN         | NOM      | MAX  |      |  |

| Contact Pitch              | Е           | 0.50 BSC |      |      |  |

| Optional Center Pad Width  | W2          |          |      | 5.50 |  |

| Optional Center Pad Length | T2          |          |      | 5.50 |  |

| Contact Pad Spacing        | C1          |          | 8.90 |      |  |

| Contact Pad Spacing        | C2          |          | 8.90 |      |  |

| Contact Pad Width (X64)    | X1          |          |      | 0.30 |  |

| Contact Pad Length (X64)   | Y1          |          |      | 0.85 |  |

| Distance Between Pads      | G           | 0.20     |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2154A

# APPENDIX A: DOCUMENT REVISION HISTORY

#### Rev A Document (11/2011)

Initial release of this document. Includes silicon issues 1 (A/D Conversion During Sleep), 2 (A/D Auto-Scan Mode), 3 (A/D Accuracy), 4 (VBTBOR) and 5 (RTCC). Added data sheet clarification 1 (Section 22.0 Real Time Clock and Calendar).

#### Rev B Document (4/2012)

Included changes to silicon issue 1 (A/D Conversion During Sleep) and added silicon issues 8 (A/D) and 9 (Reset), and added data sheet clarifications 2 (Special Features), 3 (Special Features), 4 (Special Features), 5 (Timer1), 6 (Pin Diagrams), 7 (Pin Diagrams), 8 (Guidelines for Getting Started with 16-Bit Microcontrollers), 9 (Memory Organization), 10 (I/O Ports), 11 (Memory Organization), 12 (I/O Ports), 13 (Electrical Characteristics), 14 (Electrical Characteristics), 15 (12-Bit A/D Converter with Threshold Scan), 16 (Real-Time Clock and Calendar – RTCC) and 17 (A/D Converter).

#### Rev C Document (7/2012)

Added silicon revision C0 to document, with existing silicon issues 3 (A/D, Accuracy) and 9 (Reset).

Added new silicon issues 10 (A/D) and 11 (Reset, VBAT and POR) to silicon revision B2. Issue 10 is also added to silicon revision C0.

Added data sheet clarifications 18-19 (A/D), 20-21 (Memory Organization), 22-24 (Oscillator) and 25 (Power-Saving Features).

Corrected the titles of several existing silicon issues (1, 2, 3, 4, 7 and 8) for compatibility with existing errata documentation. No changes are made to the text of any issues.

Updated the title of data sheet clarification 8 ("Getting Started with 16-bit Microcontrollers") to "Overview".

Updated several data sheet clarification issues (3, 4, 13 and 17) to remove extraneous tables, rows and other information not relevant to the items being changed.

Other minor typographic corrections throughout.

#### Rev D Document (1/2013)

In silicon issue 7 (Core (Deep Sleep)), changed the maximum value for Deep Sleep at 3.3V from 2.5  $\mu A$  to 6  $\mu A$ .

Added data sheet clarifications 26 (Power-Saving Features, 27 (Oscillator Configuration), 28 (Packaging Information), 29 (Serial Peripheral Interface (SPI)) and 30 (I/O Ports).

#### Rev E Document (2/2013)

Indicated that silicon issue 7 is also applicable to silicon revision C0.

Added data sheet clarification 31 (Power-Saving Features).

#### Rev F Document (10/2013)

Added silicon issue 12 (LCD).

#### Rev G Document (6/2014)

Updated silicon issue 4 (Core, VBAT mode) with information regarding VBTBOR in Revision B2 and Revision C0. Added silicon issue 13 (Power-on Reset).

Removed all previous data sheet clarifications that have been addressed in the latest data sheet revision.

#### Rev H (9/2016

Added silicon issue 14 (Core).

Added data sheet clarifications 1 (Pin Diagrams) and 2 (Packaging Information).

#### Rev J (1/2019)

Added silicon issue 15 (Core).

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A. Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM, net. PICkit, PICtail, PowerSmart, PureSilicon. QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2019, Microchip Technology Incorporated, All Rights Reserved. ISBN: 978-1-5224-4088-8

## **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support: http://www.microchip.com/

support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

**China - Chengdu** Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

**China - Xiamen** Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu

Tel: 82-53-744-4301

**Korea - Seoul** Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820