# **Datasheet**

Lyra P

Version 1.3

# **REVISION HISTORY**

| Version | Date         | Notes                                                                                                                                | Contributors                                 | Approver      |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------|

| 1.0     | 18 Feb 2022  | Initial release.                                                                                                                     | Raj Khatri,<br>Dave Drogowski                | Jonathan Kaye |

| 1.1     | 10 June 2022 | Updates to 5 Reference Diagrams and added 5.3 Boot.                                                                                  | Greg Leach,<br>Raj Khatri,<br>Dave Drogowski | Jonathan Kaye |

| 1.2     | 7 Sept 2022  | Fixed typo in 2 Ordering Information.                                                                                                | Dave Drogowski                               | Jonathan Kaye |

| 1.3     | 10 Feb 2023  | Added new Wireless Xpress SKU information. Updated section 2 Ordering Information and 5.3 Boot for Wireless Xpress part (453-00147). | Greg Leach                                   | Jonathan Kaye |

## **CONTENTS**

| 1 | Intro | oduction                                                                                    | 5  |

|---|-------|---------------------------------------------------------------------------------------------|----|

|   | 1.1   | Key Features                                                                                | 5  |

|   | 1.2   | Hardware Features                                                                           | 6  |

|   | 1.3   | Firmware Options                                                                            | 6  |

| 2 | Orde  | ering Information                                                                           | 7  |

| 3 | Syst  | tem Overview                                                                                | 8  |

|   | 3.1   | Block Diagram                                                                               | 8  |

|   | 3.2   | EFR32BG22 SoC                                                                               | 8  |

|   | 3.3   | Antenna                                                                                     |    |

|   | 3.4   | Power Supply                                                                                |    |

| 4 | Elec  | etrical Characteristics                                                                     | 10 |

|   | 4.1   | Absolute Maximum Ratings                                                                    | 10 |

|   | 4.2   | General Operating Conditions                                                                | 10 |

|   | 4.3   | MCU Current Consumption with 3 V Supply                                                     | 13 |

|   | 4.4   | Radio Current Consumption with 3 V Supply                                                   | 14 |

|   | 4.5   | RF Transmitter General Characteristics for the 2.4 GHz Band                                 | 15 |

|   | 4.6   | RF Receiver General Characteristics for the 2.4 GHz Band                                    | 15 |

|   | 4.7   | RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 1 Mbps Data Rate   | 16 |

|   | 4.8   | RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 2 Mbps Data Rate   | 17 |

|   | 4.9   | RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 500 kbps Data Rate | 18 |

|   | 4.10  | RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 125 kbps Data Rate | 19 |

|   | 4.11  | High-Frequency Crystal                                                                      | 20 |

|   | 4.12  | Low-Frequency Crystal                                                                       | 20 |

|   | 4.13  | Precision Low Frequency RC Oscillator (LFRCO)                                               | 20 |

|   | 4.14  | GPIO Pins                                                                                   | 21 |

|   | 4.15  | Microcontroller Peripherals                                                                 | 22 |

|   | 4.16  | Typical Performance Curves                                                                  | 23 |

| 5 | Refe  | erence Diagrams                                                                             | 24 |

|   | 5.1   | Network Co-Processor (NCP) Application with UART Host                                       | 24 |

|   | 5.2   | SoC Application                                                                             | 25 |

|   | 5.3   | Boot                                                                                        | 25 |

| 6 | Pin I | Definitions                                                                                 | 26 |

|   | 6.1   | Lyra P 31-Pin PCB Module Pinout                                                             | 26 |

|   | 6.2   | Alternate Function Table                                                                    | 27 |

|   | 6.3   | Analog Peripheral Connectivity                                                              | 28 |

|   | 6.4   | Digital Peripheral Connectivity                                                             | 29 |

| 7 | Des   | ign Guidelines                                                                              | 32 |

|   | 7.1   | Layout and Placement                                                                        | 32 |

### Lyra P Datasheet

|    | 7.2  | Proximity to Other Materials                                | 33 |

|----|------|-------------------------------------------------------------|----|

|    | 7.3  | Proximity to Human Body                                     | 33 |

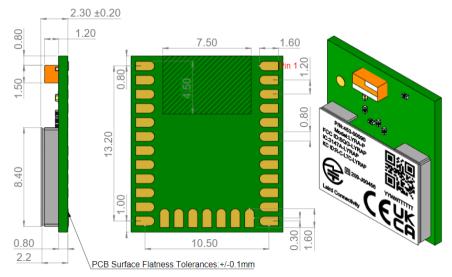

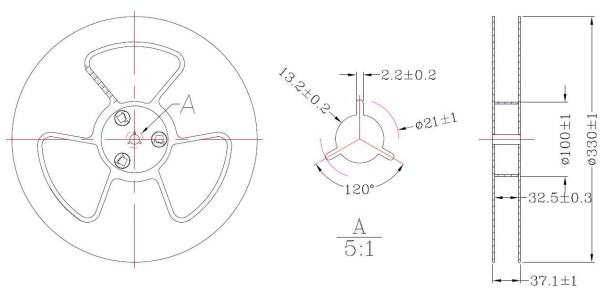

| 8  | Mech | nanical Specifications                                      | 34 |

|    | 8.1  | Dimensions                                                  | 34 |

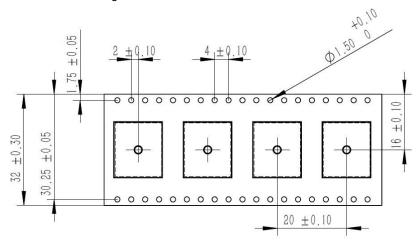

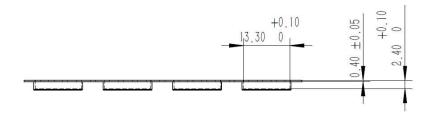

|    | 8.2  | PCB Land Pattern                                            | 35 |

|    | 8.3  | Lyra P Label Marking                                        | 36 |

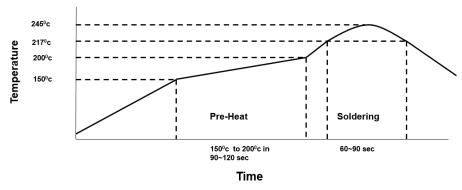

| 9  | Sold | ering Recommendations                                       | 37 |

|    | 9.1  | Reflow for lead Free Solder Paste                           | 37 |

|    | 9.2  | Recommended Reflow Profile for lead Free Solder Paste       | 37 |

| 10 | Misc | ellaneous                                                   | 38 |

|    | 10.1 | Cleaning                                                    | 38 |

|    | 10.2 | Rework                                                      | 38 |

|    | 10.3 | Handling and Storage                                        | 38 |

| 11 | Таре | and Reel                                                    | 39 |

| 12 | Regu | ılatory                                                     | 40 |

| 13 | Blue | tooth SIG Qualification                                     | 41 |

|    | 13.1 | Overview                                                    | 41 |

|    | 13.2 | Qualification Steps When Referencing on End Product Listing | 41 |

| 14 | Δddi | tional Information                                          | 43 |

#### INTRODUCTION

The Lyra P is a module designed and built to meet the performance, security, and reliability requirements of battery-powered IoT products running on Bluetooth networks.

Based on the EFR32BG22 SoC, the Lyra P enables Bluetooth® Low Energy connectivity while delivering best-in-class RF range and performance, future-proof capability for feature and OTA firmware updates, enhanced security features, and low energy consumption.

Lyra P modules are a full solution that comes with fully upgradeable, robust software stacks, world-wide regulatory certifications, advanced development and debugging tools, and support that will minimize and simplify the engineering and development of your end-products helping to accelerate their time-to-market.

The Lyra P is intended for a broad range of applications, including:

- Asset Tags and Beacons

- Sports, Fitness, and Wellness devices

- Portable Medical

- Connected Home

- Industrial and Building Automation

- Bluetooth mesh Low Power Node

#### **Key Features** 1.1

- Bluetooth 5.3

- Bluetooth mesh Low Power Node

- Built-in antenna

- Up to 8 dBm TX power

- -98.9 dBm BLE RX sensitivity at 1 Mbps

- 32-bit ARM Cortex-M33 core at up to 76.8 MHz

- 512/32 kB of Flash/RAM memory

- Optimal selection of MCU peripherals

- Up to 24 GPIO pins

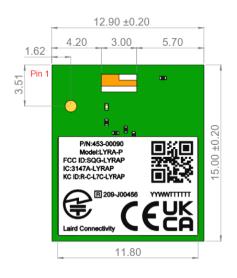

- 12.9 mm x 15.0 mm

#### 1.2 Hardware Features

#### · Supported Protocols

- Bluetooth Low Energy (Bluetooth 5.3)

- Direction finding

- 1M, 2M and LE Coded PHYs

- · Bluetooth Mesh Low Power Node

#### · Wireless System-on-Chip

- · 2.4 GHz radio

- TX power up to +8 dBm

- High-performance 32-bit ARM Cortex-M33® with DSP instruction and floating-point unit for efficient signal processing

- · 512 kB flash program memory

- · 32 kB RAM data memory

- Embedded Trace Macrocell (ETM) for advanced debugging

#### · High-Receiver Performance

- · -106.7 dBm sensitivity (0.1% BER) at 125 kbps GFSK

- -102.5 dBm sensitivity (0.1% BER) at 500 kbps GFSK

- · -98.9 dBm sensitivity (0.1% BER) at 1 Mbps GFSK

- -96.2 dBm sensitivity (0.1% BER) at 2 Mbps GFSK

#### Low-Energy Consumption

- 4.3 mA RX current at 1 Mbps GFSK

- 4.8 mA TX current at 0 dBm output power

- · 10.6 mA TX current at 8 dBm output power

- 26 μA/MHz in Active Mode (EM0)

- 1.40 µA EM2 DeepSleep current (RTCC running from LFXO, Full RAM retention)

#### Regulatory Certifications

- FCC

- CE

- ISED

- MIC/TELEC

- KCC

#### Wide Operating Range

- 1.8 to 3.8 V

- -40 to +105°C

#### Dimensions

12.9 mm x 15.0 mm x 2.2 mm

#### · Security Features

- Secure Boot with Root of Trust and Secure Loader (RTSL)

- Hardware Cryptographic Acceleration for AES128/256, SHA-1, SHA-2 (up to 256-bit), ECC (up to 256-bit), ECDSA, and ECDH

- True Random Number Generator (TRNG) compliant with NIST SP800-90 and AIS-31

- ARM® TrustZone®

- · Secure Debug with lock/unlock

#### Wide Selection of MCU Peripherals

- Analog to Digital Converter (ADC)

- 12-bit @ 1 Msps

- 16-bit @ 76.9 ksps

- Up to 24 General Purpose I/O pins with output state retention and asynchronous interrupts

- · 8 Channel DMA Controller

- 12 Channel Peripheral Reflex System (PRS)

- 4 x 16-bit Timer/Counter with 3 Compare/Capture/PWM channels

- 1 x 32-bit Timer/Counter with 3 Compare/Capture/PWM channels

- · 32-bit Real Time Counter

- 24-bit Low Energy Timer for waveform generation

- 1 x Watchdog Timer

- 2 x Universal Synchronous/Asynchronous Receiver/Transmitter (UART/SPI/SmartCard (ISO 7816)/IrDA/I2S)

- 1 x Enhanced Universal Asynchronous Receiver/Transmitter (EUART)

- 2 x I2C interface with SMBus support

- Digital microphone interface (PDM)

- · RFSENSE with selective OOK mode

## 1.3 Firmware Options

The Lyra series supports three different firmware options for software development:

**AT Command Set** – fully featured and extensible to suit any developer's needs.

- Proven over 5+ years

- Basic Bluetooth LE cable replacement

- Simplest implementation possible

- Includes all key features of Wireless Xpress and more

**Wireless Xpress** – Frozen at current release, path for existing Silicon Labs customers

- Basic Bluetooth LE cable replacement

- Secure FOTA capable FW

- Xpress command API for iOS & Android

**C Code –** Full software development with Silicon Labs SDK and Toolchain

- Native C code development

- Use Simplicity Studio IDE

- Full functionality of Silicon Labs HW / SW

## **2 Ordering Information**

Table 1: Ordering Information

| Part         | Description                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------|

| 453-00090R   | Lyra Series - Bluetooth v5.3 PCB Module with integrated antenna (Silicon Labs EFR32BG22) - Tape / Reel                 |

| 453-00090C   | Lyra Series - Bluetooth v5.3 PCB Module with integrated antenna (Silicon Labs EFR32BG22) - Cut / Tape                  |

| 453-00147R   | Lyra Series - Bluetooth v5.3 PCB Module, Integrated Antenna, Wireless Xpress FW (Silicon Labs EFR32BG22) - Tape / Reel |

| 453-00147C   | Lyra Series - Bluetooth v5.3 PCB Module, Integrated Antenna, Wireless Xpress FW (Silicon Labs EFR32BG22) – Cut / Tape  |

| 453-00090-K1 | Lyra Series - Development Kit - Bluetooth v5.3 PCB Module with integrated antenna                                      |

Note:

Part 453-00147 ships from the factory configured with Laird Connectivity's Organizational Unique Identifier (OUI) (18-C2-93) in One Time Programmable memory. This is used as the basis for the part Bluetooth address.

Legacy BGX220P parts shipped with Silabs' OUI (60-A4-23).

#### 3 SYSTEM OVERVIEW

# 3.1 Block Diagram

The Lyra P module combines an energy-friendly MCU with a highly integrated radio transceiver in a PCB module with a robust, integrated antenna. This section gives a short introduction to the features of the module.

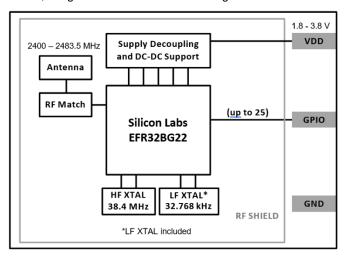

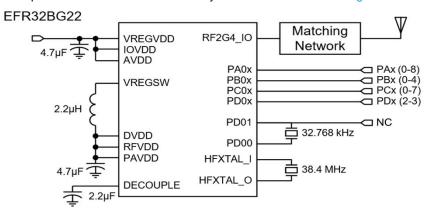

Figure 1: Lyra P Block Diagram

The block diagram for the Lyra P module is shown in Figure 1. The wireless module includes the EFR32BG22 wireless System on a Chip (SoC), required decoupling capacitors and inductors, 38.4 MHz and 32.768 kHz crystals, RF matching circuit, and integrated chip antenna.

A simplified internal schematic for the Lyra P module is shown in Figure 2.

Figure 2: Lyra P Module Schematic

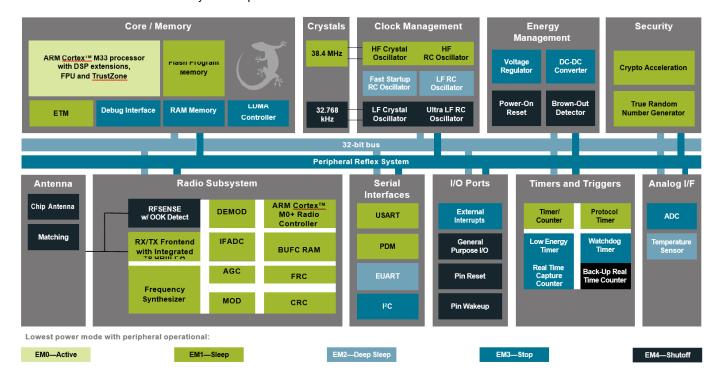

#### 3.2 EFR32BG22 SoC

The EFR32BG22 SoC features a 32-bit ARM Cortex M33 core, a 2.4 GHz high-performance radio, 512 kB of flash memory, a rich set of MCU peripherals, and various clock management and serial interfacing options. Consult the EFR32xG22 Wireless Gecko Reference Manual and the EFR32BG22 Data Sheet for details.

### 3.3 Antenna

Lyra P modules include a ceramic chip antenna on board with the characteristics detailed in the table below.

Table 2: Antenna Efficiency and Peak Gain

| Parameter  | With optimal layout | Note                                                                                                                 |

|------------|---------------------|----------------------------------------------------------------------------------------------------------------------|

| Efficiency | -1 dB               | Antenna efficiency, gain and radiation pattern are highly dependent on the application PCB                           |

| Peak gain  | 1.86 dBi            | layout and mechanical design. Refer to Design Guidelines for recommendations to achieve optimal antenna performance. |

# 3.4 Power Supply

The Lyra P requires a single nominal supply level of 3.0 V to operate. All necessary decoupling and filtering components are included in the module.

## 4 ELECTRICAL CHARACTERISTICS

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on T<sub>A</sub>=25 °C and VDD supply at 3.0 V, by production test and/or technology characterization.

- Radio performance numbers are measured in conducted mode, based on Silicon Laboratories reference designs using output power-specific external RF impedance-matching networks for interfacing to a 50 Ω antenna.

- Minimum and maximum values represent the worst conditions across supply voltage, process variation, and operating temperature, unless stated otherwise.

## 4.1 Absolute Maximum Ratings

Stresses beyond those listed below may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions beyond those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 3: Absolute Maximum Ratings

| Parameter                           | Symbol                 | Test Condition | Min  | Тур | Max                    | Unit   |

|-------------------------------------|------------------------|----------------|------|-----|------------------------|--------|

| Storage temperature range           | $T_{STG}$              |                | -40  | _   | +105                   | °C     |

| Voltage on VDD supply pin           | $V_{DDMAX}$            |                | -0.3 | _   | 3.8                    | V      |

| Voltage ramp rate on VDD supply pin | V <sub>DDRAMPMAX</sub> |                | _    | _   | 1.0                    | V / µs |

| DC voltage on any GPIO pin          | V <sub>DIGPIN</sub>    |                | -0.3 | _   | V <sub>VDD</sub> + 0.3 | V      |

| Total current into VDD pin          | $I_{VDDMAX}$           | Source         | _    | _   | 200                    | mA     |

| Total current into GND pin          | I <sub>GNDMAX</sub>    | Sink           | _    | _   | 200                    | mA     |

| Current per I/O pin                 | I <sub>IOMAX</sub>     | Sink           | _    | _   | 50                     | mA     |

|                                     |                        | Source         | _    | _   | 50                     | mA     |

| Current for all I/O pins            | I <sub>IOALLMAX</sub>  | Sink           | _    | _   | 200                    | mA     |

|                                     |                        | Source         | _    | _   | 200                    | mA     |

# 4.2 General Operating Conditions

This table specifies the general operating temperature range and supply voltage range for all supplies. The minimum and maximum values of all other tables are specified over this operating range, unless otherwise noted.

| Parameter                    | Symbol            | Test Condition                  | Min | Тур | Max  | Unit |

|------------------------------|-------------------|---------------------------------|-----|-----|------|------|

| Operating ambient            | $T_A$             | -G temperature grade            | -40 | _   | +85  | °C   |

| temperature range            |                   | -N temperature grade            | -40 | _   | +105 | °C   |

| VDD operating supply voltage | $V_{VDD}$         | DCDC in regulation <sup>1</sup> | 2.2 | 3.0 | 3.8  | V    |

| voltage                      |                   | DCDC in bypass                  | 1.8 | 3.0 | 3.8  | V    |

| HCLK and SYSCLK frequency    | f <sub>HCLK</sub> | VSCALE2, MODE =<br>WS1          | _   | _   | 76.8 | MHz  |

|                              |                   | VSCALE2, MODE =<br>WS0          | _   | _   | 40   | MHz  |

|                              |                   | VSCALE1, MODE =<br>WS0          | _   | _   | 40   | MHz  |

| Parameter            | Symbol                   | Test Condition        | Min | Тур  | Max  | Unit |

|----------------------|--------------------------|-----------------------|-----|------|------|------|

| PCLK frequency       | f <sub>PCLK</sub>        | VSCALE2               | _   | _    | 50   | MHz  |

|                      |                          | VSCALE1               | _   | _    | 40   | MHz  |

| EM01 Group A clock   | f <sub>EM01GRPACLK</sub> | VSCALE2               | _   | _    | 76.8 | MHz  |

| frequency            |                          | VSCALE1               | _   | _    | 40   | MHz  |

| EM01 Group B clock   | f <sub>EM01GRPBCLK</sub> | VSCALE2               | _   | _    | 76.8 | MHz  |

| frequency            |                          | VSCALE1               | _   | _    | 40   | MHz  |

| Radio HCLK frequency | f <sub>RHCLK</sub>       | VSCALE2 or<br>VSCALE1 | _   | 38.4 | _    | MHz  |

<sup>1.</sup> The supported maximum  $V_{VDD}$  in regulation mode is a function of temperature and 10-year lifetime average load current. See more details in DC-DC Operating Limits.

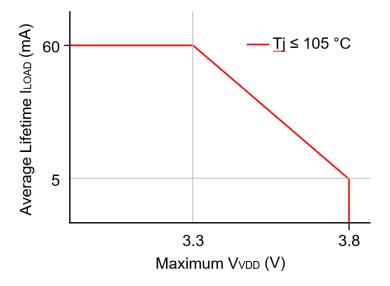

#### 4.2.1 DC-DC Operating Limits

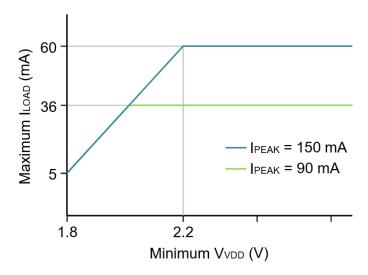

The maximum supported voltage on the VDD supply pin is limited under certain conditions. Maximum input voltage is a function of temperature and the average load current over a 10-year lifetime. Figure 3 shows the safe operating region under specific conditions. Exceeding this safe operating range may impact the reliability and performance of the DC-DC converter.

The average load current for an application can typically be determined by examining the current profile during the time the device is powered. For example, an application that is continuously powered which spends 99% of the time asleep consuming  $2 \mu A$  and 1% of the time active and consuming  $10 \mu A$  has an average lifetime load current of about  $102 \mu A$ .

Figure 3: Lifetime average load current limit vs. maximum input voltage

The minimum input voltage for the DC-DC in EM0/EM1 mode is a function of the maximum load current, and the peak current setting. Figure 4 shows the max load current vs. input voltage for different DC-DC peak inductor current settings.

Figure 4: Transient maximum load current vs. Minimum input voltage

# 4.3 MCU Current Consumption with 3 V Supply

Unless otherwise indicated, typical conditions are: Module supply voltage = 3.0 V. Voltage scaling level = VSCALE1.  $T_A$  = 25 °C. Mini mum and maximum values in this table represent the worst conditions across process variation at  $T_A$  = 25 °C.

Table 4: MCU Current Consumption with 3 V Supply

| Parameter                                                     | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Test Condition                                                                                       | Min | Тур  | Max | Unit   |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0 mode with all peripherals disabled | I <sub>ACTIVE</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 76.8 MHz HFRCO w/ DPLL referenced to 38.4 MHz crystal, CPU running while loop from flash, VSCALE2    | _   | 27   | _   | µA/MHz |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76.8 MHz HFRCO w/ DPLL referenced to 38.4 MHz crystal, CPU running CoreMark loop from flash, VSCALE2 | _   | 37   | _   | µA/MHz |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38.4 MHz crystal, CPU running Prime from flash                                                       | _   | 28   | _   | μΑ/MHz |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38.4 MHz crystal, CPU running while loop from flash                                                  | _   | 26   | _   | µA/MHz |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38.4 MHz crystal, CPU running CoreMark loop from flash                                               | _   | 38   | _   | µA/MHz |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38 MHz HFRCO, CPU running while loop from flash                                                      | _   | 22   | _   | µA/MH  |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76.8 MHz HFRCO w/ DPLL referenced to 38.4 MHz crystal, CPU running Prime from flash, VSCALE2         | _   | 28   | _   | μA/MH: |

| Current consumption in EM1 mode with all peripherals disabled | I <sub>EM1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76.8 MHz HFRCO w/ DPLL referenced to 38.4 MHz crystal, VSCALE2                                       | _   | 17   | _   | µA/MH: |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38.4 MHz crystal                                                                                     | _   | 17   | _   | μΑ/MH: |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38 MHz HFRCO                                                                                         | _   | 13   | _   | μA/MH: |

| Current consumption in EM2 mode, VSCALE0                      | from flash  38.4 MHz crystal, CPU running CoreMark — 38 loop from flash  38 MHz HFRCO, CPU running while loop — 22 from flash  76.8 MHz HFRCO w/ DPLL referenced to — 38.4 MHz crystal, CPU running Prime from flash, VSCALE2  1 EM1 76.8 MHz HFRCO w/ DPLL referenced to — 17 als 38.4 MHz crystal, VSCALE2  38.4 MHz crystal, VSCALE2  38.4 MHz crystal — 17 38 MHz HFRCO — 13 Full RAM retention and RTC running from — 1.40 LFXO  Full RAM retention and RTC running from — 1.40 LFRCO  Full RAM retention and RTC running from — 1.75 LFRCO in precision mode  24 kB RAM retention and RTC running — 1.35 from LFXO | 1.40                                                                                                 | _   | μΑ   |     |        |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                      | _   | 1.40 | _   | μA     |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <del>-</del>                                                                                         | _   | 1.75 | _   | μΑ     |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                    | _   | 1.32 | _   | μΑ     |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <del>-</del>                                                                                         | _   | 1.66 | _   | μΑ     |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8 kB RAM retention and RTC running from LFXO                                                         | _   | 1.21 | _   | μА     |

| Parameter                                                                            | Symbol               | Test Condition                                 | Min | Тур  | Max | Unit |

|--------------------------------------------------------------------------------------|----------------------|------------------------------------------------|-----|------|-----|------|

|                                                                                      |                      | 8 kB RAM retention and RTC running from LFRCO  | _   | 1.20 | _   | μΑ   |

| Current consumption in EM3 mode, VSCALE0                                             | I <sub>EM3_VS</sub>  | 8 kB RAM retention and RTC running from ULFRCO | _   | 1.05 | _   | μΑ   |

| Current consumption in EM4 mode                                                      | I <sub>EM4</sub>     | No BURTC, No LF Oscillator, DCDC bypassed      |     | 0.17 | _   | μΑ   |

| Additional current in EM2 or EM3 when any peripheral in PD0B is enabled <sup>1</sup> | I <sub>PD0B_VS</sub> |                                                | _   | 0.37 | _   | μΑ   |

Note:

1. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See for a list of the peripherals in each power domain.

# 4.4 Radio Current Consumption with 3 V Supply

RF current consumption measured with MCU in EM1, HCLK = 38.4 MHz, and all MCU peripherals disabled. Unless otherwise indicated, typical conditions are: VDD = 3.0 V.  $T_A$  = 25 °C. Minimum and maximum values in this table represent the worst conditions across process variation at  $T_A$  = 25 °C.

| Parameter                                                           | Symbol                 | Test Condition                                             | Min | Тур  | Max | Unit |

|---------------------------------------------------------------------|------------------------|------------------------------------------------------------|-----|------|-----|------|

| System current consumption in receive mode, active packet reception | I <sub>RX_ACTIVE</sub> | 125 kbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running | _   | 4.5  | _   | mA   |

|                                                                     |                        | 500 kbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running | _   | 4.5  | _   | mA   |

|                                                                     |                        | 1 Mbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running   | _   | 4.3  | _   | mA   |

|                                                                     |                        | 2 Mbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running   | _   | 4.8  | _   | mA   |

| System current consumption in receive mode, listening for packet    | I <sub>RX_LISTEN</sub> | 125 kbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running | _   | 4.4  | _   | mA   |

|                                                                     |                        | 500 kbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running | _   | 4.4  | _   | mA   |

|                                                                     |                        | 1 Mbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running   | _   | 4.2  | _   | mA   |

|                                                                     |                        | 2 Mbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running   | _   | 4.7  | _   | mA   |

| System current consumption in transmit mode                         | I <sub>TX</sub>        | f = 2.4 GHz, CW, 0 dBm output power                        | _   | 4.8  | _   | mA   |

|                                                                     |                        | f = 2.4 GHz, CW, 6 dBm output power                        | _   | 8.8  | _   | mA   |

|                                                                     |                        | f = 2.4 GHz, CW, 8 dBm output power                        | _   | 10.6 | _   | mA   |

## 4.5 RF Transmitter General Characteristics for the 2.4 GHz Band

Unless otherwise indicated, typical conditions are:  $T_A = 25$  °C, VDD = 3.0V. RF center frequency 2.45 GHz.

| Parameter                                                                    | Symbol                | <b>Test Condition</b> (Output Power)             | Min  | Тур  | Max    | Unit |

|------------------------------------------------------------------------------|-----------------------|--------------------------------------------------|------|------|--------|------|

| RF tuning frequency range                                                    | F <sub>RANGE</sub>    |                                                  | 2400 | _    | 2483.5 | MHz  |

| Maximum TX power                                                             | POUT <sub>MAX</sub>   | 8 dBm                                            | _    | 8.2  | _      | dBm  |

| Minimum active TX Power                                                      | POUT <sub>MIN</sub>   | 8 dBm                                            | _    | -27  | _      | dBm  |

| Output power variation vs VDD supply voltage variation, frequency = 2450 MHz | POUT <sub>VAR_V</sub> | 8 dBm with VDD voltage swept from 1.8 V to 3.0 V | _    | 0.04 | _      | dB   |

| Output power variation vs temperature,<br>Frequency = 2450 MHz               | POUT <sub>VAR_T</sub> | 8 dBm, (-40 to +105 °C)                          | _    | 0.9  | _      | dB   |

| Output power variation vs RF frequency                                       | POUT <sub>VAR_F</sub> | 8 dBm                                            | _    | 0.2  | _      | dB   |

## 4.6 RF Receiver General Characteristics for the 2.4 GHz Band

Unless otherwise indicated, typical conditions are: T<sub>A</sub> = 25 °C, VDD = 3.0V. RF center frequency 2.45 GHz.

Table 5: RF Receiver General Characteristics for the 2.4 GHz Band

| Parameter                 | Symbol             | Test Condition | Min  | Тур | Max    | Unit |

|---------------------------|--------------------|----------------|------|-----|--------|------|

| RF tuning frequency range | F <sub>RANGE</sub> |                | 2400 | _   | 2483.5 | MHz  |

https://www.lairdconnect.com/

# 4.7 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 1 Mbps Data Rate

Unless otherwise indicated, typical conditions are:  $T_A = 25$  °C, VDD = 3.0V. RF center frequency 2.45 GHz.

Table 6: RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 1 Mbps Data Rate

| Parameter                              | Symbol              | Test Condition                                                                               | Min | Тур       | Max      | Unit |

|----------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-----|-----------|----------|------|

| Max usable receiver input level        | SAT                 | Signal is reference signal <sup>1</sup>                                                      | _   | 10        | _        | dBm  |

| Sensitivity                            | SENS                | Signal is reference signal, 37 byte payload <sup>2</sup>                                     | _   | -<br>98.9 | _        | dBm  |

|                                        |                     | Signal is reference signal, 255 byte payload <sup>1</sup>                                    | _   | -<br>97.4 | _        | dBm  |

|                                        |                     | With non-ideal signals <sup>3 1</sup>                                                        | _   | -<br>96.9 | _        | dBm  |

| Signal to co-channel<br>interferer     | C/I <sub>CC</sub>   | (see notes) <sup>1 4</sup>                                                                   | _   | 8.7       | _        | dB   |

| N ± 1 Adjacent channel selectivity     | C/I <sub>1</sub>    | Interferer is reference signal at +1 MHz offset <sup>1 5 4 6</sup>                           | _   | -6.6      | _        | dB   |

|                                        |                     | Interferer is reference signal at -1 MHz offset <sup>1 5 4 6</sup>                           | _   | -6.5      | _        | dB   |

| N ± 2 Alternate channel selectivity    | C/I <sub>2</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 5 4 6</sup>                           | _   | -<br>40.9 | _        | dB   |

|                                        |                     | Interferer is reference signal at -2 MHz offset 1 5 4 6                                      | _   | -<br>39.9 | _        | dB   |

| N ± 3 Alternate channel selectivity    | C/I <sub>3</sub>    | Interferer is reference signal at +3 MHz offset <sup>1 5 4 6</sup>                           | _   | -<br>45.9 | _        | dB   |

|                                        |                     | Interferer is reference signal at -3 MHz offset 1 5 4 6                                      | _   | -<br>46.2 | _        | dB   |

| Selectivity to image frequency         | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision 1 6                   | _   | -<br>23.5 | _        | dB   |

| Selectivity to image frequency ± 1 MHz | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +1 MHz with 1 MHz precision <sup>1 6</sup> | _   | -<br>40.9 | _        | dB   |

|                                        |                     | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision <sup>1 6</sup> | _   | -6.6      | _        | dB   |

| Intermodulation<br>performance         | IM                  | n = 3 (see note <sup>7</sup> )                                                               | _   | -<br>17.1 | <u>—</u> | dBm  |

#### Note:

- 1.0.017% Bit Error Rate.

- 2.0.1% Bit Error Rate.

- 3. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 4. Desired signal -67 dBm.

- 5. Desired frequency 2402 MHz ≤ Fc ≤ 2480 MHz.

- 6. With allowed exceptions.

- 7. As specified in Bluetooth Core specification version 5.1, Vol 6, Part A, Section 4.4

# 4.8 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 2 Mbps Data Rate

Unless otherwise indicated, typical conditions are:  $T_A = 25$  °C, VDD = 3.0V. RF center frequency 2.45 GHz.

Table 7: RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 2 Mbps Data Rate

| Parameter                                            | Symbol              | Test Condition                                                                               | Min | Тур       | Max | Unit |

|------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-----|-----------|-----|------|

| Max usable receiver input level                      | SAT                 | Signal is reference signal <sup>1</sup>                                                      | _   | 10        | _   | dBm  |

| Sensitivity                                          | SENS                | Signal is reference signal, 37 byte payload <sup>2</sup>                                     | _   | -<br>96.2 | _   | dBm  |

|                                                      |                     | Signal is reference signal, 255 byte payload <sup>1</sup>                                    | —   | -<br>94.6 | _   | dBm  |

|                                                      |                     | With non-ideal signals <sup>3 1</sup>                                                        | _   | -<br>94.4 | _   | dBm  |

| Signal to co-channel interferer                      | C/I <sub>CC</sub>   | (see notes) <sup>1 4</sup>                                                                   | _   | 8.8       | _   | dB   |

| N ± 1 Adjacent channel selectivity                   | C/I <sub>1</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 5 4 6</sup>                           | _   | -9.2      | _   | dB   |

|                                                      |                     | Interferer is reference signal at -2 MHz offset <sup>1 5 4 6</sup>                           | _   | -6.6      | _   | dB   |

| N ± 2 Alternate channel C/I <sub>2</sub> selectivity |                     | Interferer is reference signal at +4 MHz offset <sup>1 5 4 6</sup>                           | _   | -<br>43.3 | _   | dB   |

|                                                      |                     | Interferer is reference signal at -4 MHz offset <sup>1 5 4 6</sup>                           | _   | -<br>44.0 | _   | dB   |

| N ± 3 Alternate channel selectivity                  | C/I <sub>3</sub>    | Interferer is reference signal at +6 MHz offset 1 5 4 6                                      | _   | -<br>48.6 | _   | dB   |

|                                                      |                     | Interferer is reference signal at -6 MHz offset <sup>1 5 4 6</sup>                           | _   | -<br>50.7 | _   | dB   |

| Selectivity to image frequency                       | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision 16                    | _   | -<br>23.8 | _   | dB   |

| Selectivity to image frequency ± 2 MHz               | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +2 MHz with 1 MHz precision <sup>1 6</sup> | _   | -<br>43.3 | _   | dB   |

|                                                      |                     | Interferer is reference signal at image frequency -2 MHz with 1 MHz precision 1 6            | _   | -9.2      | _   | dB   |

| Intermodulation performance                          | IM                  | n = 3 (see note <sup>7</sup> )                                                               | _   | -<br>18.8 | _   | dBm  |

#### Note:

- 1.0.017% Bit Error Rate.

- 2.0.1% Bit Error Rate.

- 3. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 4. Desired signal -64 dBm.

- 5. Desired frequency 2402 MHz ≤ Fc ≤ 2480 MHz.

- 6. With allowed exceptions.

- 7. As specified in Bluetooth Core specification version 5.1, Vol 6, Part A, Section 4.4

# 4.9 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 500 kbps Data Rate

Unless otherwise indicated, typical conditions are: T<sub>A</sub> = 25 °C, VDD = 3.0V. RF center frequency 2.45 GHz.

Table 8: RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 500 kbps Data Rate

| Parameter                              | Symbol              | Test Condition                                                                                     | Min | Тур        | Max | Unit |

|----------------------------------------|---------------------|----------------------------------------------------------------------------------------------------|-----|------------|-----|------|

| Max usable receiver input level        | SAT                 | Signal is reference signal <sup>1</sup>                                                            | _   | 10         | _   | dBm  |

| Sensitivity                            | SENS                | Signal is reference signal, 37 byte payload <sup>2</sup>                                           | _   | -<br>102.5 | _   | dBm  |

|                                        |                     | Signal is reference signal, 255 byte payload <sup>1</sup>                                          | _   | -<br>101.2 | _   | dBm  |

|                                        |                     | With non-ideal signals <sup>3 1</sup>                                                              | _   | -<br>100.2 | _   | dBm  |

| Signal to co-channel interferer        | C/I <sub>CC</sub>   | (see notes) <sup>1 4</sup>                                                                         | _   | 2.7        | _   | dB   |

| N ± 1 Adjacent channel selectivity     |                     |                                                                                                    | _   | -8.0       | _   | dB   |

|                                        |                     | Interferer is reference signal at -1 MHz offset <sup>1 5 4 6</sup>                                 | _   | -7.9       | _   | dB   |

| N ± 2 Alternate channel selectivity    | C/I <sub>2</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 5 4 6</sup>                                 | _   | -46.5      | _   | dB   |

|                                        |                     | Interferer is reference signal at -2 MHz offset <sup>1 5 4 6</sup>                                 | _   | -49.9      | _   | dB   |

| N ± 3 Alternate channel selectivity    | C/I <sub>3</sub>    | Interferer is reference signal at +3 MHz offset <sup>1 5 4 6</sup>                                 | _   | -48.9      | _   | dB   |

|                                        |                     | Interferer is reference signal at -3 MHz offset <sup>1 5 4 6</sup>                                 | _   | -53.8      | _   | dB   |

| Selectivity to image frequency         | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision 16                          | _   | -48.3      | _   | dB   |

| Selectivity to image frequency ± 1 MHz | C/I <sub>IM_1</sub> | Interferer is reference signal at image<br>frequency +1 MHz with 1<br>MHz precision <sup>1 6</sup> | _   | -49.9      | _   | dB   |

|                                        |                     | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision 16                   | _   | -46.5      | _   | dB   |

#### Note:

- 1.0.017% Bit Error Rate.

- 2.0.1% Bit Error Rate.

- 3. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 4. Desired signal -72 dBm.

- 5. Desired frequency 2402 MHz ≤ Fc ≤ 2480 MHz.

- 6. With allowed exceptions.

# 4.10 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 125 kbps Data Rate

Unless otherwise indicated, typical conditions are:  $T_A = 25$  °C, VDD = 3.0V. RF center frequency 2.45 GHz.

Table 9: RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 125 kbps Data Rate

| Parameter                                                | Symbol            | Test Condition                                                                                     | Min | Тур    | Max | Unit |

|----------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------|-----|--------|-----|------|

| Max usable receiver input level                          | SAT               | Signal is reference signal <sup>1</sup>                                                            | _   | 10     | _   | dBm  |

| Sensitivity                                              | SENS              | Signal is reference signal, 37 byte payload <sup>2</sup>                                           | _   | -106.7 | _   | dBm  |

|                                                          |                   | Signal is reference signal, 255 byte payload <sup>1</sup>                                          | _   | -106.4 | _   | dBm  |

|                                                          |                   | With non-ideal signals <sup>3</sup>                                                                | _   | -105.8 | _   | dBm  |

| Signal to co-channel interferer                          | C/I <sub>CC</sub> | (see notes) <sup>1 4</sup>                                                                         | _   | 0.9    | _   | dB   |

| N ± 1 Adjacent channel selectivity                       | C/I <sub>1</sub>  | Interferer is reference signal at +1 MHz offset <sup>1 5 4 6</sup>                                 | _   | -13.6  | _   | dB   |

|                                                          |                   | Interferer is reference signal at -1 MHz offset <sup>1 5 4 6</sup>                                 | _   | -13.4  | _   | dB   |

| N ± 2 Alternate channel selectivity                      | C/I <sub>2</sub>  | Interferer is reference signal at +2 MHz offset <sup>1 5 4 6</sup>                                 | _   | -52.6  | _   | dB   |

|                                                          |                   | Interferer is reference signal at -2 MHz offset <sup>1 5 4 6</sup>                                 | _   | -55.8  | _   | dB   |

| N ± 3 Alternate channel selectivity                      | C/I <sub>3</sub>  | Interferer is reference signal at +3 MHz offset <sup>1 5 4 6</sup>                                 | _   | -53.7  | _   | dB   |

|                                                          |                   | Interferer is reference signal at -3 MHz offset <sup>1 5 4 6</sup>                                 | _   | -59.0  | _   | dB   |

| Selectivity to image frequency                           | C/I <sub>IM</sub> | Interferer is reference signal at image frequency with 1 MHz precision <sup>16</sup>               | _   | -52.7  | _   | dB   |

| Selectivity to image C/I <sub>IM</sub> frequency ± 1 MHz |                   | Interferer is reference signal at image<br>frequency +1 MHz with 1<br>MHz precision <sup>1 6</sup> | _   | -53.7  | _   | dB   |

|                                                          |                   | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision 16                   | _   | -52.6  | -   | dB   |

- 1.0.017% Bit Error Rate.

- 2.0.1% Bit Error Rate.

- 3. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 4. Desired signal -79 dBm.

- 5. Desired frequency 2402 MHz  $\leq$  Fc  $\leq$  2480 MHz.

- 6. With allowed exceptions.

## 4.11 High-Frequency Crystal

Table 10: High-Frequency Crystal

| Parameter                   | Symbol                  | Test Condition                     | Min | Тур  | Max | Unit |

|-----------------------------|-------------------------|------------------------------------|-----|------|-----|------|

| Crystal frequency           | f <sub>HFXTAL</sub>     |                                    | _   | 38.4 | _   | MHz  |

| Initial calibrated accuracy | ACC <sub>HFXTAL</sub>   |                                    | -10 | ±5   | 10  | ppm  |

| Temperature drift           | DRIFT <sub>HFXTAL</sub> | Across specified temperature range | -20 | _    | 20  | ppm  |

# 4.12Low-Frequency Crystal

Table 11: Low-Frequency Crystal

| Parameter                      | Symbol                  | Test Condition    | Min  | Тур    | Max | Unit |

|--------------------------------|-------------------------|-------------------|------|--------|-----|------|

| Crystal frequency <sup>1</sup> | $f_{LFXTAL}$            |                   | _    | 32.768 | _   | kHz  |

| Temperature drift              | DRIFT <sub>LFXTAL</sub> | -40 °C to +85 °C  | -100 | _      | 100 | ppm  |

|                                |                         | -40 °C to +105 °C | -150 | _      | 150 | ppm  |

| Note:                          |                         |                   |      |        |     |      |

# 4.13 Precision Low Frequency RC Oscillator (LFRCO)

#### Table 12: Precision Low Frequency RC Oscillator (LFRCO)

1. Nominal frequency tolerance of the crystal is ± 20 ppm.

| Parameter                     | Symbol                 | Test Condition                                                                | Min  | Тур    | Max | Unit |

|-------------------------------|------------------------|-------------------------------------------------------------------------------|------|--------|-----|------|

| Nominal oscillation frequency | F <sub>LFRCO</sub>     |                                                                               | _    | 32.768 | _   | kHz  |

| Frequency accuracy            | F <sub>LFRCO_ACC</sub> | Normal mode                                                                   | -3   | _      | 3   | %    |

|                               |                        | Precision mode <sup>1</sup> , across operating temperature range <sup>2</sup> | -500 | _      | 500 | ppm  |

| Startup time                  | t <sub>STARTUP</sub>   | Normal mode                                                                   | _    | 204    | _   | μs   |

|                               |                        | Precision mode <sup>1</sup>                                                   | _    | 11.7   | _   | ms   |

| Current consumption           | I <sub>LFRCO</sub>     | Normal mode                                                                   | _    | 175    | _   | nA   |

|                               |                        | Precision mode <sup>1</sup> , T = stable at 25 °C <sup>3</sup>                | _    | 655    | _   | nA   |

- 1. The LFRCO operates in high-precision mode when CFG\_HIGHPRECEN is set to 1. High-precision mode is not available in EM4.

- 2. Includes  $\pm$  40 ppm frequency tolerance of the HFXO crystal.

- 3. Includes periodic re-calibration against HFXO crystal oscillator.

### 4.14GPIO Pins

Unless otherwise indicated, typical conditions are: VDD = 3.0 V.

Table 13: GPIO Pins

| Parameter                       | Symbol                 | Test Condition                                                                                                                            | Min        | Тур  | Max           | Unit |

|---------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------|------|---------------|------|

| Leakage current                 | I <sub>LEAK_IO</sub>   | MODEx = DISABLED, VDD<br>= 3.0 V                                                                                                          | _          | 2.5  | _             | nA   |

| Input low voltage <sup>1</sup>  | $V_{IL}$               | Any GPIO pin                                                                                                                              | _          | _    | 0.3 *<br>VDD  | V    |

|                                 |                        | RESETn                                                                                                                                    | _          | _    | 0.3 *<br>DVDD | V    |

| Input high voltage <sup>1</sup> | $V_{IH}$               | Any GPIO pin                                                                                                                              | 0.7 * VDD  | _    | _             | V    |

|                                 |                        | RESETn                                                                                                                                    | 0.7 * DVDD | _    | _             | V    |

| Hysteresis of input             | $V_{HYS}$              | Any GPIO pin                                                                                                                              | 0.05*VDD   | _    | _             | V    |

| voltage                         |                        | RESETn                                                                                                                                    | 0.05*DVDD  | _    | _             | V    |

| Output low voltage              | V <sub>OL</sub>        | Sinking 20mA, VDD = 3.0 V                                                                                                                 | _          | _    | 0.2 *<br>VDD  | V    |

|                                 |                        | Sinking 8mA, VDD = 1.62 V                                                                                                                 | _          | _    | 0.4 *<br>VDD  | V    |

| Output high voltage             | $V_{OH}$               | Sourcing 20mA, VDD = 3.0 V                                                                                                                | 0.8 * VDD  | _    | _             | V    |

|                                 |                        | Sourcing 8mA, VDD = 1.62 V                                                                                                                | 0.6 * VDD  | _    | _             | V    |

| GPIO rise time                  | T <sub>GPIO_RISE</sub> | VDD = 3.0V, $C_{load}$ = 50pF,<br>SLEWRATE = 4, 10% to<br>90%                                                                             | _          | 8.4  | _             | ns   |

|                                 |                        | VDD = 1.7V, $C_{load}$ = 50pF,<br>SLEWRATE = 4, 10% to<br>90%                                                                             | _          | 13   | _             | ns   |

| GPIO fall time                  | T <sub>GPIO_FALL</sub> | VDD = 3.0V, $C_{load}$ = 50pF,<br>SLEWRATE = 4, 90% to<br>10%                                                                             | _          | 7.1  | _             | ns   |

|                                 |                        | VDD = 1.7V, $C_{load}$ = 50pF,<br>SLEWRATE = 4, 90% to<br>10%                                                                             | _          | 11.9 | _             | ns   |

| Pull up/down<br>resistance      | R <sub>PULL</sub>      | GPIO pull-up to VDD:  MODEn = DISABLE,  DOUT=1. GPIO pull- down to VSS: MODEn =  WIREDORPULLDOWN,  DOUT = 0.  RESETn pin pull-up to DVDD. | 35         | 44   | 55            | kΩ   |

| Maximum filtered glitch width   | $T_{GF}$               | MODE = INPUT, DOUT = 1                                                                                                                    | _          | 27   | _             | ns   |

<sup>1.</sup> GPIO input thresholds are proportional to the VDD pin. RESETn input thresholds are proportional to the internal DVDD supply, which is generated by the DC-DC converter. DVDD is equal to 1.8 V when DC-DC is active and bypassed to VDD when DC-DC is inactive.

## 4.15 Microcontroller Peripherals

The MCU peripherals set available in Lyra P modules includes:

- ADC: 12-bit at 1 Msps, 16-bit at 76.9 ksps

- 16-bit and 32-bit Timers/Counters

- 24-bit Low Energy Timer for waveform generation

- 32-bit Real Time Counter

- USART (UART/SPI/SmartCards/IrDA/I2S)

- EUART (UART/IrDA)

- I<sup>2</sup>C peripheral interfaces

- PDM interface

- 12 Channel Peripheral Reflex System

For details on their electrical performance, consult the relevant portions of Section 4 in the SoC datasheet.

To learn which GPIO ports provide access to every peripheral, consult Analog Peripheral Connectivity and Digital Peripheral Connectivity.

## 4.16 Typical Performance Curves

Typical performance curves indicate typical characterized performance under the stated conditions.

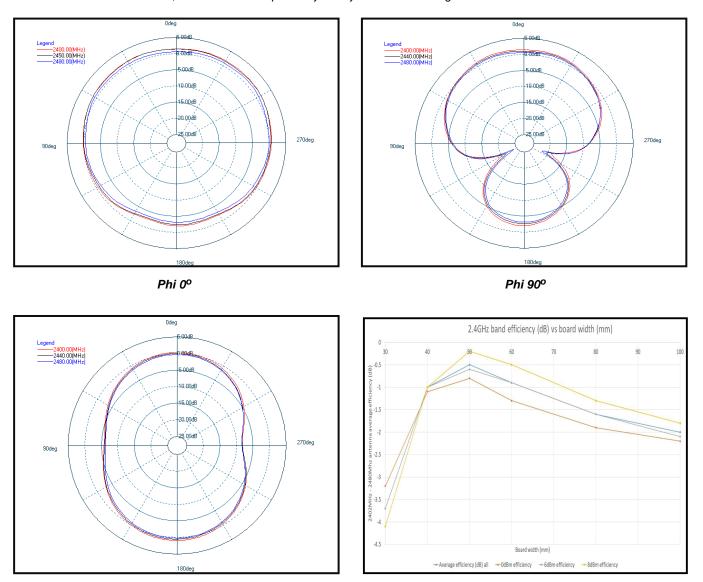

#### 4.16.1 Antenna Radiation and Efficiency

Typical Lyra P radiation patterns and efficiency for the on-board chip antenna under optimal operating conditions are plotted in the figures that follow. Antenna gain and radiation patterns have a strong dependence on the size and shape of the application PCB the module is mounted on, as well as on the proximity of any mechanical design to the antenna.

Figure 5: Typical 2D Antenna Radiation Patterns and Efficiency

Theta 90°

Americas: +1-800-492-2320 Europe: +44-1628-858-940 Hong Kong: +852-2762-4823

Radiation Efficiency vs Application Board GND Plane Width

### 5 REFERENCE DIAGRAMS

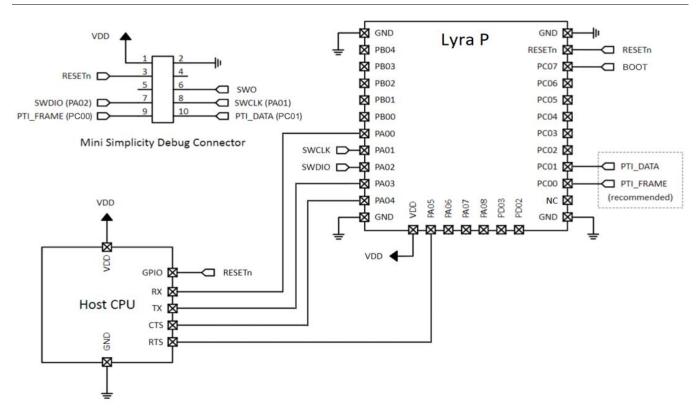

# 5.1 Network Co-Processor (NCP) Application with UART Host

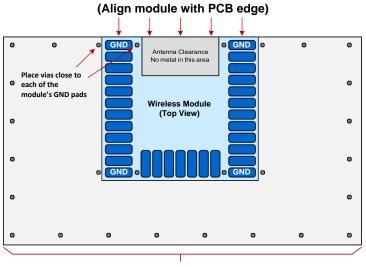

The Lyra P can be controlled over the UART interface as a peripheral to an external host processor. Typical power supply, programming/debug interface, and host interface connections are shown in the figure below.

Note: For boot pin, see section 5.3 Boot.

Figure 6: UART NCP Configuration

Hong Kong: +852-2762-4823

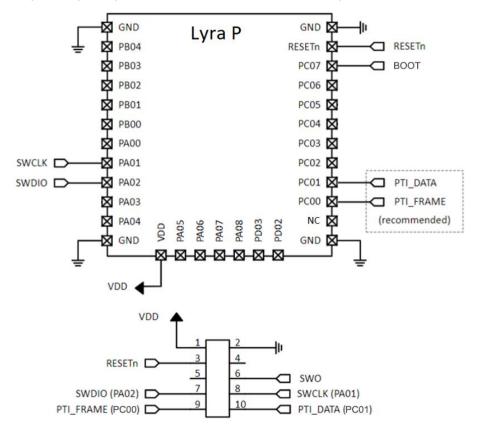

## 5.2 SoC Application

The Lyra P can be used in a stand-alone SoC configuration without an external host processor. Typical power supply and programming/debug interface connections are shown in the figure below.

Figure 7: Stand-Alone SoC Configuration

#### 5.3 Boot

The BOOT pin is used to determine when execution of the bootloader is required. Upon reset, execution of the bootloader begins. The state of the BOOT pin is read immediately upon start-up of the bootloader. If LOW, execution of the bootloader continues, facilitating firmware update via the UART. If the BOOT pin is HIGH, the bootloader will stop execution and pass control to the main application firmware.

Note:

To maintain backwards compatibility with legacy BGX220P Wireless Xpress parts, the BOOT pin for 453-00147 is mapped to the legacy part BOOT pin location. Refer to the table below for details of the appropriate part BOOT pin location.

Table 14: Different BOOT Pin Locations for Lyra P

| Part      | BOOT Pin Location |                 |  |  |  |

|-----------|-------------------|-----------------|--|--|--|

| Fail      | Pin Number        | Pin Description |  |  |  |

| 453-00090 | 29                | PC07            |  |  |  |

| 453-00147 | 19                | PD02            |  |  |  |

### **6** PIN DEFINITIONS

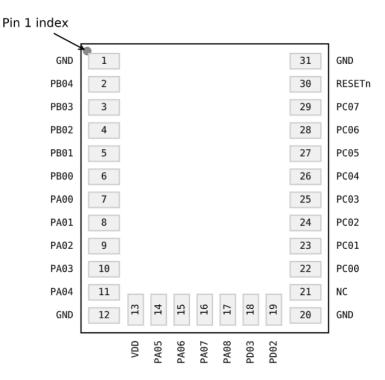

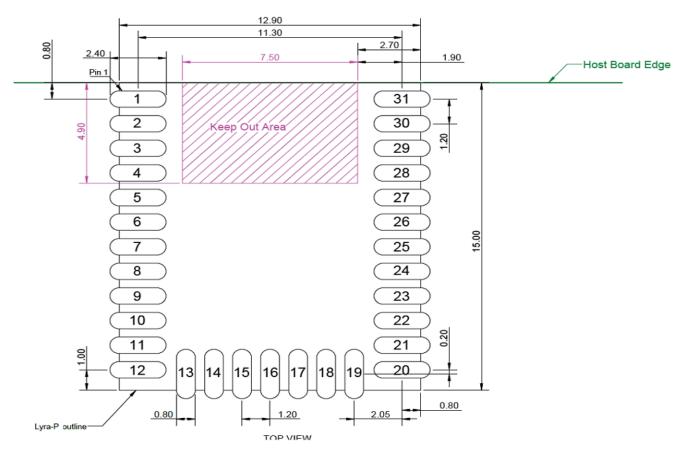

# 6.1 Lyra P 31-Pin PCB Module Pinout

Figure 8: Lyra P 31-Pin PCB Module With LF Crystal Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see Table 15: GPIO alternate function table, Analog Peripheral Connectivity, and Digital Peripheral Connectivity.

| Pin<br>Name | Pin(s) | Description    | Pin<br>Name | Pin(s) | Description |

|-------------|--------|----------------|-------------|--------|-------------|

| GND         | 1      | Ground         | PB04        | 2      | GPIO        |

| PB03        | 3      | GPIO           | PB02        | 4      | GPIO        |

| PB01        | 5      | GPIO           | PB00        | 6      | GPIO        |

| PA00        | 7      | GPIO           | PA01        | 8      | GPIO        |

| PA02        | 9      | GPIO           | PA03        | 10     | GPIO        |

| PA04        | 11     | GPIO           | GND         | 12     | Ground      |

| VDD         | 13     | Power supply   | PA05        | 14     | GPIO        |

| PA06        | 15     | GPIO           | PA07        | 16     | GPIO        |

| PA08        | 17     | GPIO           | PD03        | 18     | GPIO        |

| PD02        | 19     | GPIO           | GND         | 20     | Ground      |

| NC          | 21     | Do not connect | PC00        | 22     | GPIO        |

| PC01        | 23     | GPIO           | PC02        | 24     | GPIO        |

| PC03        | 25     | GPIO           | PC04        | 26     | GPIO        |

| PC05        | 27     | GPIO           | PC06        | 28     | GPIO        |

All Rights Reserved

| Pin<br>Name | Pin(s) | Description | Pin<br>Name | Pin(s) | Description                                                                                                                                                                                                                                                                                                                                                         |

|-------------|--------|-------------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC07        | 29     | GPIO        | RESETn      | 30     | Reset Pin. The RESETn pin is pulled up to an internal DVDD supply. An external pull-up is not recommended. To apply an external reset source to this pin, it is required to only drive this pin low during reset, and let the internal pull-up ensure that reset is released. The RESETn pin can be left unconnected if no external reset switch or source is used. |

| GND         | 31     | Ground      |             |        |                                                                                                                                                                                                                                                                                                                                                                     |

## 6.2 Alternate Function Table

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows what functions are available on each device pin.

Table 15: GPIO alternate function table

| GPIO |             | Alternate Fur | nction          |

|------|-------------|---------------|-----------------|

| PB03 | GPIO.EM4WU4 |               |                 |

| PB01 | GPIO.EM4WU3 |               |                 |

| PB00 | IADC0.VREFN |               |                 |

| PA00 | IADC0.VREFP |               |                 |

| PA01 | GPIO.SWCLK  |               |                 |

| PA02 | GPIO.SWDIO  |               |                 |

| PA03 | GPIO.SWV    | GPIO.TDO      | GPIO.TRACEDATA0 |

| PA04 | GPIO.TDI    | GPIO.TRACECLK |                 |

| PA05 | GPIO.EM4WU0 |               |                 |

| PD02 | GPIO.EM4WU9 |               |                 |

| PC00 | GPIO.EM4WU6 | GPIO.THMSW_EN |                 |

| PC05 | GPIO.EM4WU7 |               |                 |

| PC07 | GPIO.EM4WU8 |               |                 |

# 6.3 Analog Peripheral Connectivity

Many analog resources are routable and can be connected to numerous GPIO's. The table below indicates which peripherals are available on each GPIO port. When a differential connection is being used, positive inputs are restricted to the EVEN pins and Negative inputs are restricted to the ODD pins. When a single ended connection is being used positive input is available on all pins. See the SoC Reference Manual for more details on the ABUS and analog peripherals.

Table 16: ABUS Routing Table

| Davish saal | Signal  | P    | A   | P    | В   | P    | C   | P    | סי  |

|-------------|---------|------|-----|------|-----|------|-----|------|-----|

| Peripheral  |         | EVEN | ODD | EVEN | ODD | EVEN | ODD | EVEN | ODD |

| IADC0       | ana_neg | Yes  | Yes | Yes  | Yes | Yes  | Yes | Yes  | Yes |

|             | ana_pos | Yes  | Yes | Yes  | Yes | Yes  | Yes | Yes  | Yes |

# 6.4 Digital Peripheral Connectivity

Many digital resources are routable and can be connected to numerous GPIO's. The table below indicates which peripherals are available on each GPIO port.

| B 11 12             | PORT      |           |           |           |  |  |

|---------------------|-----------|-----------|-----------|-----------|--|--|

| Peripheral.Resource | PA        | РВ        | PC        | PD        |  |  |

| CMU.CLKIN0          |           |           | Available | Available |  |  |

| CMU.CLKOUT0         |           |           | Available | Available |  |  |

| CMU.CLKOUT1         |           |           | Available | Available |  |  |

| CMU.CLKOUT2         | Available | Available |           |           |  |  |

| EUART0.CTS          | Available | Available | Available | Available |  |  |

| EUART0.RTS          | Available | Available | Available | Available |  |  |

| EUART0.RX           | Available | Available | Available | Available |  |  |

| EUART0.TX           | Available | Available | Available | Available |  |  |

| FRC.DCLK            |           |           | Available | Available |  |  |

| FRC.DFRAME          |           |           | Available | Available |  |  |

| FRC.DOUT            |           |           | Available | Available |  |  |

| 12C0.SCL            | Available | Available | Available | Available |  |  |

| I2C0.SDA            | Available | Available | Available | Available |  |  |

| 12C1.SCL            |           |           | Available | Available |  |  |

| I2C1.SDA            |           |           | Available | Available |  |  |

| LETIMER0.OUT0       | Available | Available |           |           |  |  |

| LETIMER0.OUT1       | Available | Available |           |           |  |  |