# 2ED2106 (4) S06F (J)

# 2ED2106 (4) S06F (J) 650 V high-side and low-side gate driver with integrated bootstrap diode

#### **Features**

- Unique Infineon Thin-Film-Silicon On Insulator (SOI)-technology •

- Negative VS transient immunity of 100 V •

- Floating channel designed for bootstrap operation •

- Operating voltages (VS node) upto + 650 V •

- Maximum bootstrap voltage (VB node) of + 675 V •

- Integrated ultra-fast, low resistance bootstrap diode •

- Logic operational up to -11 V on VS Pin •

- Negative voltage tolerance on inputs of -5 V •

- Independent under voltage lockout for both channels •

- Schmitt trigger inputs with hysteresis •

- 3.3 V, 5 V and 15 V input logic compatible •

- Maximum supply voltage of 25 V •

- Dual package options of DSO-8 and DSO-14 •

- High and low voltage pins separated for maximum creepage and • clearance (2ED21064S06J version)

- Separate logic and power ground with the 2ED21064S06J version .

- **RoHS** compliant

## Potential applications

Driving IGBTs, enhancement mode N-Channel MOSFETs in various power electronic applications. Typical Infineon recommendations are as below:

- Motor drives, general purpose inverters having TRENCHSTOP™ IGBT6 or 600 V EasyPACK™ modules or its equivalent power stages

- Refrigeration compressors, induction cookers, other major home appliances having RCD series IGBTs or • TRENCHSTOP<sup>™</sup> family IGBTs or their equivalent power stages

- Battery operated small home appliances such as power tools, vaccum cleaners using low voltage • OptiMOS<sup>™</sup> MOSFETs or their equivalent power stages

- Totem pole, half-bridge and full-bridge converters in offline AC-DC power supplies for industrial SMPS having high voltage CoolMOS<sup>™</sup> super junction MOSFETs or TRENCHSTOP<sup>™</sup> H3 and WR5 IGBT series or their equivalent

- High power LED and HID lighting having CoolMOS<sup>™</sup> super junction MOSFETs •

- Electric vehicle (EV) charging stations and battery management systems

- Driving 650 V SiC MOSFETs in above applications

## Product validation

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22

#### Ordering information

| Base part number | Packago typo                  | Standar       | d pack   | Orderable part number |

|------------------|-------------------------------|---------------|----------|-----------------------|

|                  | part number Package type Form |               | Quantity |                       |

| 2ED2106S06F      | DSO - 8                       | Tape and Reel | 2500     | 2ED2106S06FXUMA1      |

| 2ED21064S06J     | DSO - 14                      | Tape and Reel | 2500     | 2ED21064S06JXUMA1     |

## **Product summary**

V<sub>S\_OFFSET</sub> = 650 V max  $I_{o+pk} / I_{o-pk}$  (typ.) = + 0.29 A/ - 0.7 A  $V_{cc} = 10 V \text{ to } 20 V$ Delay matching = 35 ns max. Propogation delay = 200 ns  $t_{ON} / t_{OFF} (typ.) = 200 \text{ ns} / 200 \text{ ns}$

#### Packages

DSO-8

#### Description

#### Description

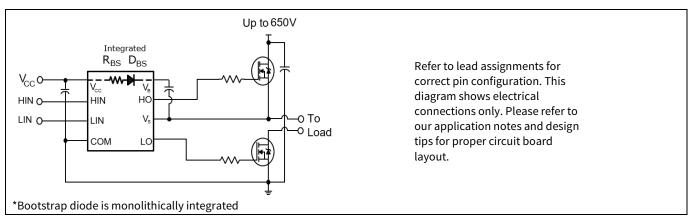

The 2ED2106(4)S06F(J) is a high voltage, high speed power MOSFET and IGBT driver with independent high and low side referenced output channels. Based on Infineon's SOI-technology there is an excellent ruggedness and noise immunity with capability to maintain operational logic at negative voltages of up to - 11 V on VS pin ( $V_{cc}$ = 15 V) on transient voltages. There are not any parasitic thyristor structures present in the device, hence no parasitic latch up may occur at all temperature and voltage conditions. The logic input is compatible with standard CMOS or LSTTL output, down to 3.3 V logic. The output drivers feature a high pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to drive an N-channel power MOSFET, SiC MOSFET or IGBT in the high side configuration, which operate up to 650 V.

#### Figure 1 Typical application block diagram

Summary of feature comparison of the 2ED210x family:

#### Table 1

| Part No.     | Input<br>logic | Cross<br>conduction<br>prevention<br>logic | Deadtime                         | Ground pins | t <sub>on</sub> /t <sub>off</sub> | Package  |

|--------------|----------------|--------------------------------------------|----------------------------------|-------------|-----------------------------------|----------|

| 2ED2106S06F  | HIN, LIN       | No                                         | Nono                             | СОМ         |                                   | DSO - 8  |

| 2ED21064S06J | ΠIN, LIN       | No None                                    | None                             | VSS / COM   | 200 mg /                          | DSO - 14 |

| 2ED2108S06F  | HIN, LIN       | IN Yes                                     | Internal 540 ns                  | COM         | 200 ns /<br>200 ns                | DSO - 8  |

| 2ED21084S06J |                |                                            | Programmable<br>540 ns - 5000 ns | VSS / COM   |                                   | DSO - 14 |

| 2ED2109S06F  |                |                                            | Internal 540 ns                  | СОМ         |                                   | DSO - 8  |

| 2ED21094S06J | IN, <u>SD</u>  | Yes                                        | Programmable<br>540 ns - 5000 ns | VSS / COM   | 740 ns /<br>200 ns                | DSO - 14 |

| 2ED21091S06F | IN, DT/SD      | Yes                                        | Programmable<br>540 ns - 2700 ns | СОМ         | 200 113                           | DSO – 8  |

# 1 Table of contents

| 1    | Table of contents                                                                       | 3  |

|------|-----------------------------------------------------------------------------------------|----|

| 2    | Block diagram                                                                           | 4  |

| 3    | Pin configuration and functionality                                                     | 5  |

| 3.1  | Pin configuration                                                                       | 5  |

| 3.2  | Pin functionality                                                                       | 5  |

| 4    | Electrical parameters                                                                   | 6  |

| 4.1  | Absolute maximum ratings                                                                | 6  |

| 4.2  | Recommended operating conditions                                                        | 6  |

| 4.3  | Static electrical characteristics                                                       | 7  |

| 4.4  | Dynamic electrical characteristics                                                      | 8  |

| 5    | Application information and additional details                                          | 9  |

| 5.1  | IGBT / MOSFET gate drive                                                                | 9  |

| 5.2  | Switching and timing relationships                                                      | 9  |

| 5.3  | Matched propagation delays                                                              | 10 |

| 5.4  | Input logic compatibility                                                               | 10 |

| 5.5  | Undervoltage lockout                                                                    | 11 |

| 5.6  | Bootstrap diode                                                                         | 11 |

| 5.7  | Calculating the bootstrap capacitance $C_{\scriptscriptstyle BS}$                       |    |

| 5.8  | Tolerant to negative tranisents on input pins                                           |    |

| 5.9  | Negative voltage transient tolerance of VS pin                                          |    |

| 5.10 | NTSOA – Negative Transient Safe Operating Area                                          |    |

| 5.11 | Higher headroom for input to output signal transmission with logic operation upto -11 V |    |

| 5.12 | Maximum switching frequency                                                             |    |

| 5.13 | PCB layout tips                                                                         | 18 |

| 6    | Qualification information                                                               | 19 |

| 7    | Related products                                                                        | 19 |

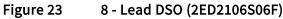

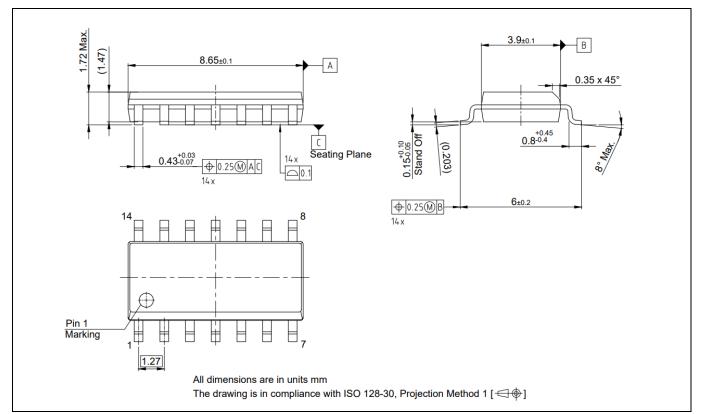

| 8    | Package details                                                                         | 20 |

| 9    | Part marking information                                                                | 21 |

| 10   | Additional documentation and resources                                                  | 22 |

| 10.1 | Infineon online forum resources                                                         | 22 |

| 11   | Revision history                                                                        | 23 |

|      |                                                                                         |    |

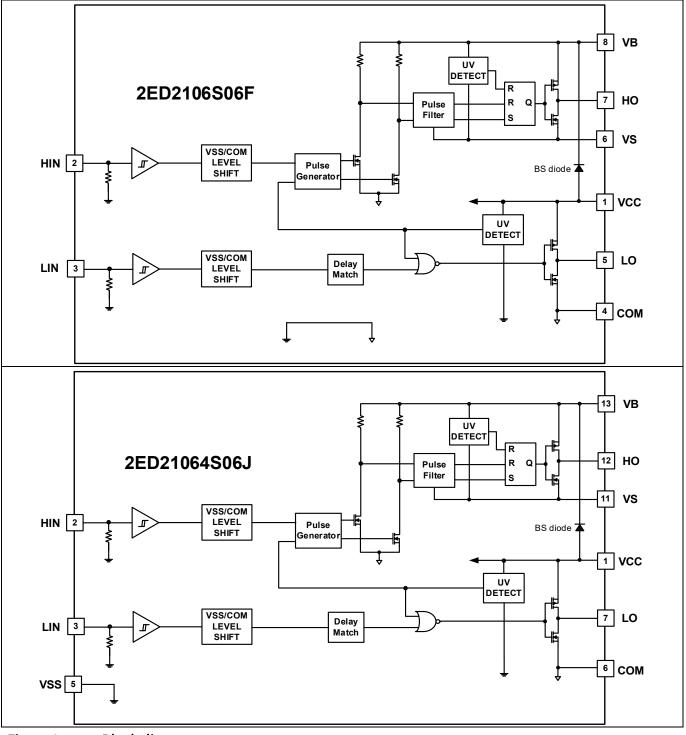

## 2 Block diagram

## 3 Pin configuration and functionality

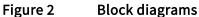

## 3.1 Pin configuration

Figure 3 2ED2106(4)S06F(J) pin assignments (top view)

## 3.2 Pin functionality

#### Table 2

| Symbol | Description                                                                         |

|--------|-------------------------------------------------------------------------------------|

| VCC    | Low-side and logic supply voltage                                                   |

|        | Logic input for high-side gate driver output (HO), in phase. Schmitt trigger inputs |

| HIN    | with hysteresis and pull down                                                       |

| LIN    | Logic input for low-side gate driver output (LO), in phase. Schmitt trigger inputs  |

| LIN    | with hysteresis and pull down                                                       |

| VSS    | Logic ground ( 2ED21064S06J only)                                                   |

| СОМ    | Low-side gate drive return                                                          |

| LO     | Low-side driver output                                                              |

| VS     | High voltage floating supply return                                                 |

| НО     | High-side driver output                                                             |

| VB     | High-side gate drive floating supply                                                |

## 4 Electrical parameters

#### 4.1 Absolute maximum ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM unless otherwise stated in the table. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Table 3           | Absolute maximum ratings                            |                   |                           |                       |        |

|-------------------|-----------------------------------------------------|-------------------|---------------------------|-----------------------|--------|

| Symbol            | Definition                                          | Min.              | Max.                      | Units                 |        |

| V <sub>B</sub>    | High-side floating well supply voltage Note         | 1                 | V <sub>cc</sub> – 5       | 675                   |        |

| Vs                | High-side floating well supply return volta         | ge                | $V_{CC} - V_{BS} - 5$     | 650                   |        |

| V <sub>HO</sub>   | Floating gate drive output voltage                  |                   | Vs - 0.5                  | V <sub>B</sub> + 0.5  |        |

| $V_{\text{BS}}$   | Floating gate drive voltage supply voltage          |                   | -1                        | 25                    | V      |

| $V_{cc}$          | Low side supply voltage                             |                   | -1                        | 25                    | v      |

| $V_{LO}$          | Low-side output voltage                             |                   | -0.5                      | V <sub>cc</sub> + 0.5 |        |

| V <sub>IN</sub>   | Logic input voltage (HIN & LIN)                     |                   | -5/ (V <sub>ss</sub> – 5) | V <sub>cc</sub> + 0.5 |        |

| V <sub>ss</sub>   | Logic ground (2ED21064S06J only)                    |                   | V <sub>cc</sub> – 25      | V <sub>cc</sub> + 0.5 |        |

| dVs/dt            | Allowable Vs offset supply transient relative       | ve to COM         | —                         | 50                    | V/ns   |

| P <sub>D</sub>    | Package power dissipation @ $T_A \leq +25^{\circ}C$ | 8 - Lead DSO - 8  |                           | 0.625                 | W      |

| ГD                |                                                     | 14 - Lead DSO -14 | —                         | 1                     | vv     |

| Rth <sub>JA</sub> | Thermal resistance, junction to ambient             | 8 - Lead DSO - 8  |                           | 200                   | °C/W   |

| IXUIJA            | Thermat resistance, junction to ambient             | 14 - Lead DSO -14 | —                         | 120                   | · C/ W |

| TJ                | Junction temperature                                |                   | —                         | 150                   |        |

| Ts                | Storage temperature                                 |                   | -55                       | 150                   | °C     |

| Τ_                | Lead temperature (soldering, 10 seconds)            |                   | —                         | 300                   |        |

Table 3 Absolute maximum ratings

Note 1: In case  $V_{CC} > V_B$  there is an additional power dissipation in the internal bootstrap diode between pins  $V_{CC}$  and  $V_B$  in case of activated bootstrap diode.

#### 4.2 Recommended operating conditions

For proper operation, the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to COM unless otherwise stated in the table. The offset rating is tested with supplies of  $(V_{CC} - COM) = (V_B - V_S) = 15 \text{ V}.$

| Symbol          | Definition                                           | Min                                 | Мах                       | Units |

|-----------------|------------------------------------------------------|-------------------------------------|---------------------------|-------|

| $V_{B}$         | Bootstrap voltage                                    | V <sub>s</sub> + 10                 | V <sub>s</sub> + 20       |       |

| $V_{\text{BS}}$ | High-side floating well supply voltage               | 10                                  | 20                        |       |

| Vs              | High-side floating well supply offset voltage Note 2 | $V_{\text{CC}} - V_{\text{BS}} - 1$ | 650                       |       |

| V <sub>HO</sub> | Floating gate drive output voltage                   | Vs                                  | V <sub>B</sub>            | V     |

| Vcc             | Low-side supply voltage                              | 10                                  | 20                        | v     |

| V <sub>LO</sub> | Low-side output voltage                              | СОМ                                 | V <sub>cc</sub>           |       |

| V <sub>IN</sub> | Logic input voltage(HIN & LIN)                       | -4 / (V <sub>SS</sub> – 4)          | 5 / (V <sub>ss</sub> + 5) |       |

| $V_{SS}$        | Logic ground (2ED21064S06J only) with respect to COM | -5                                  | +5                        |       |

| T <sub>A</sub>  | Ambient temperature                                  | -40                                 | 125                       | °C    |

Note 2: Logic operation for  $V_S$  of – 11 V to +650 V.

#### 4.3 Static electrical characteristics

$(V_{cc}-COM) = (V_B - V_S) = 15 \text{ V}, V_{SS} = COM \text{ and } T_A = 25 \text{ °C}$  unless otherwise specified. The  $V_{IL}$ ,  $V_{IH}$  and  $I_{IN}$  parameters are referenced to Vss / COM and are applicable to the respective input leads: HIN and LIN. The  $V_0$  and  $I_0$  parameters are referenced to  $V_S$  / COM and are applicable to the respective output leads HO or LO. The  $V_{CCUV}$  parameters are referenced to COM. The  $V_{BSUV}$  parameters are referenced to  $V_S$ .

| Symbol              | Definition                                                               | Min. | Тур. | Max. | Units | <b>Test Conditions</b>                       |

|---------------------|--------------------------------------------------------------------------|------|------|------|-------|----------------------------------------------|

| V <sub>BSUV</sub> + | V <sub>BS</sub> supply undervoltage positive going threshold             | 7.6  | 8.2  | 8.9  |       |                                              |

| V <sub>BSUV</sub> - | V <sub>BS</sub> supply undervoltage negative going threshold             | 6.7  | 7.2  | 8.1  |       |                                              |

| V <sub>BSUVHY</sub> | V <sub>BS</sub> supply undervoltage hysteresis                           | _    | 1.0  | —    | V     |                                              |

| $V_{CCUV^+}$        | V <sub>cc</sub> supply undervoltage positive going threshold             | 8.4  | 9.1  | 9.8  |       |                                              |

| V <sub>ccuv-</sub>  | V <sub>cc</sub> supply undervoltage negative going threshold             | 7.5  | 8.2  | 8.9  |       |                                              |

| V <sub>CCUVHY</sub> | V <sub>cc</sub> supply undervoltage hysteresis                           | _    | 0.9  | —    |       |                                              |

| I <sub>LK</sub>     | High-side floating well offset supply leakage                            | _    | 1    | 12.5 |       | $V_{\rm B} = V_{\rm S} = 650  \rm V$         |

| I <sub>QBS</sub>    | Quiescent V <sub>BS</sub> supply current                                 | _    | 170  | _    | uA    | V <sub>IN</sub> = 0 V or 5 V                 |

| I <sub>QCC</sub>    | Quiescent V <sub>cc</sub> supply current                                 | _    | 300  | 600  |       |                                              |

| V <sub>OH</sub>     | High level output voltage drop, $V_{cc}$ - $V_{LO}$ , $V_{B}$ - $V_{HO}$ | _    | 0.05 | 0.2  | V     | I <sub>0</sub> = 2 mA                        |

| V <sub>OL</sub>     | Low level output voltage drop, V <sub>o</sub>                            | _    | 0.02 | 0.1  | v     |                                              |

| l <sub>o+mean</sub> | Mean output current from 3 V to 6 V                                      | 180  | 230  | _    |       | $C_L = 22 \text{ nF}$<br>$V_O = 0 \text{ V}$ |

| I <sub>0+</sub>     | Peak output current turn-on <sup>1</sup>                                 | —    | 290  | —    | mA    |                                              |

| $I_{o-mean}$        | Mean output current from 12 V to 9 V                                     | 450  | 650  | —    | IIIA  | C <sub>L</sub> = 22 nF                       |

| l <sub>o-</sub>     | Peak output current turn-off <sup>1</sup>                                | _    | 700  | _    |       | V <sub>o</sub> = 15 V                        |

| V <sub>IH</sub>     | Logic "1" input voltage                                                  | 1.7  | 2.1  | 2.4  | v     | Vcc = 10 V to 20 V                           |

| VIL                 | Logic "0" input voltage                                                  | 0.7  | 0.9  | 1.1  | v     | VCC = 10 V to 20 V                           |

| I <sub>IN+</sub>    | Input bias current (Output = High)                                       | —    | 25   | 50   |       | $V_{IN} = 5 V$                               |

| I <sub>IN-</sub>    | Input bias current (Output = Low)                                        | —    | —    | 1    | μA    | $V_{IN} = 0 V$                               |

| $V_{\text{FBSD}}$   | Bootstrap diode forward voltage between Vcc and VB                       | _    | 1    | 1.2  | V     | I <sub>F</sub> = 0.3 mA                      |

| I <sub>FBSD</sub>   | Bootstrap diode forward current between Vcc<br>and VB                    | 45   | 85   | 125  | mA    | $V_{CC} - V_B = 4 V$                         |

| $R_{BSD}$           | Bootstrap diode resistance                                               | 20   | 30   | 45   | Ω     | $V_{F1} = 4 V, V_{F2} = 5 V$                 |

| Vs                  | Allowable Negative VS pin voltage for IN<br>Signal propagation to HO     | _    | -11  | -10  | V     | Vcc = 15 V                                   |

<sup>1</sup> Not subjected to production test, verified by characterization.

## 4.4 Dynamic electrical characteristics

$V_{CC} = V_{BS} = 15$  V,  $V_{SS} = COM$ ,  $T_A = 25$  °C and  $C_L = 1000$  pF unless otherwise specified.

#### Table 6Dynamic electrical characteristics

| Symbol           | Definition                                | Min. | Тур. | Max. | Units | Test<br>Conditions         |

|------------------|-------------------------------------------|------|------|------|-------|----------------------------|

| t <sub>on</sub>  | Turn-on propagation delay                 | _    | 200  | 300  |       |                            |

| t <sub>OFF</sub> | Turn-off propagation delay                | _    | 200  | 300  |       | $V_{\text{LIN/HIN}} = 0 V$ |

| t <sub>R</sub>   | Turn-on rise time                         | —    | 100  | 150  | ns    | or 5 V                     |

| t⊧               | Turn-off fall time                        | _    | 35   | 80   |       | $V_s = 0 V$                |

| MT               | Delay matching time (HS & LS turn-on/off) | _    | _    | 35   |       |                            |

## 5 Application information and additional details

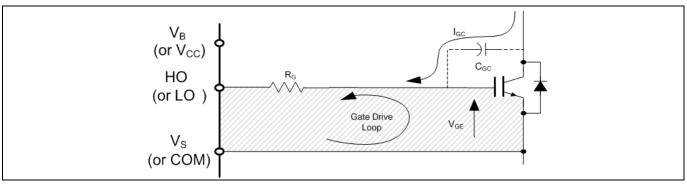

#### 5.1 IGBT / MOSFET gate drive

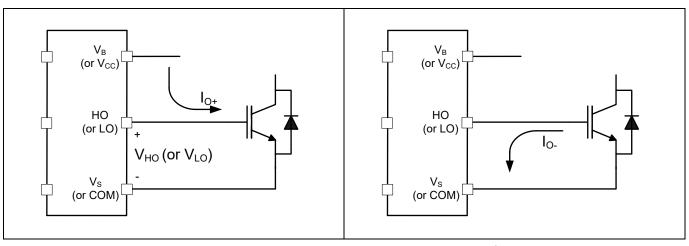

The 2ED2106 (4) S06F (J) HVIC is designed to drive MOSFET or IGBT power devices. Figure 4 and Figure 5 illustrate several parameters associated with the gate drive functionality of the HVIC. The output current of the HVIC, used to drive the gate of the power switch, is defined as  $I_0$ . The voltage that drives the gate of the external power switch is defined as  $V_{HO}$  for the high-side power switch and  $V_{LO}$  for the low-side power switch; this parameter is sometimes generically called  $V_{OUT}$  and in this case does not differentiate between the high-side or low-side output voltage.

Figure 4 HVIC Sourcing current

Figure 5

HVIC Sinking current

## 5.2 Switching and timing relationships

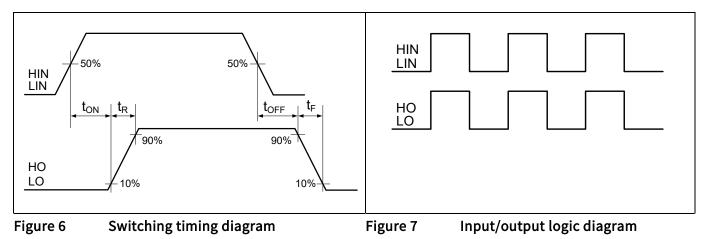

The relationships between the input and output signals of the 2ED2106 (4) S06F (J) are illustrated below in Figure 6 and Figure 7. From these figures, we can see the definitions of several timing parameters (i.e.  $t_{ON}$ ,  $t_{OFF}$ ,  $t_R$ , and  $t_F$ ) associated with this device.

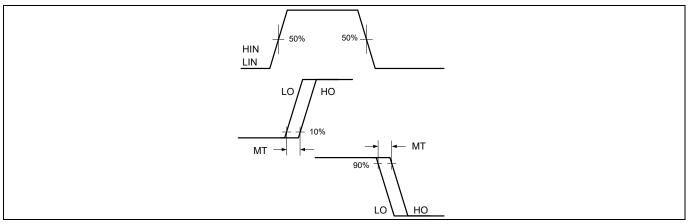

#### 5.3 Matched propagation delays

The 2ED2106 (4) S06F (J) is designed with propagation delay matching circuitry. With this feature, the IC's response at the output to a signal at the input requires approximately the same time duration (i.e.,  $t_{ON}$ ,  $t_{OFF}$ ) for both the low-side channels and the high-side channels; the maximum difference is specified by the delay matching parameter (MT). The propagation turn-on delay ( $t_{ON}$ ) of the 2ED2106 (4) S06F (J) is matched to the propagation turn-off delay ( $t_{OFF}$ ).

#### 5.4 Input logic compatibility

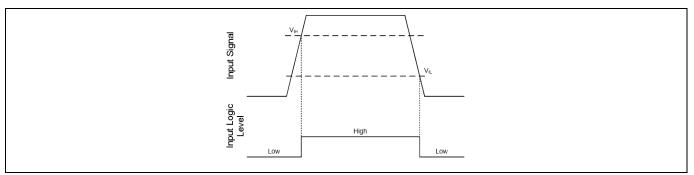

The input pins are based on a TTL and CMOS compatible input-threshold logic that is independent of the Vcc supply voltage. With typical high threshold ( $V_{IH}$ ) of 2.1 V and typical low threshold ( $V_{IL}$ ) of 0.9 V, along with very little temperature variation as summarized in Figure 9, the input pins are conveniently driven with logic level PWM control signals derived from 3.3 V and 5 V digital power-controller devices. Wider hysteresis (typically 0.9 V) offers enhanced noise immunity compared to traditional TTL logic implementations, where the hysteresis is typically less than 0.5 V. 2ED2106 (4) S06F (J) also features tight control of the input pin threshold voltage levels which eases system design considerations and ensures stable operation across temperature. The 2ED2106 (4) S06F (J) features floating input protection wherein if any of the input pin is left floating, the output of the corresponding stage is held in the low state. This is achieved using pull-down resistors on all the input pins (HIN, LIN) as shown in the block diagram. The 2ED2106 (4) S06F (J) has input pins that are capable of sustaining voltages higher than the bias voltage applied on the Vcc pin of the device.

#### 5.5 Undervoltage lockout

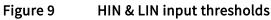

This IC provides undervoltage lockout protection on both the  $V_{CC}$  (logic and low-side circuitry) power supply and the  $V_{BS}$  (high-side circuitry) power supply. Figure 10 is used to illustrate this concept;  $V_{CC}$  (or  $V_{BS}$ ) is plotted over time and as the waveform crosses the UVLO threshold ( $V_{CCUV+/-}$  or  $V_{BSUV+/-}$ ) the undervoltage protection is enabled or disabled.

Upon power-up, should the  $V_{cc}$  voltage fail to reach the  $V_{CCUV+}$  threshold, the IC won't turn-on. Additionally, if the  $V_{cc}$  voltage decreases below the  $V_{ccUV-}$  threshold during operation, the undervoltage lockout circuitry will recognize a fault condition and shutdown the high and low-side gate drive outputs.

Upon power-up, should the  $V_{BS}$  voltage fail to reach the  $V_{BSUV+}$  threshold, the IC won't turn-on. Additionally, if the  $V_{BS}$  voltage decreases below the  $V_{BSUV-}$  threshold during operation, the undervoltage lockout circuitry will recognize a fault condition, and shutdown the high-side gate drive outputs of the IC.

The UVLO protection ensures that the IC drives the external power devices only when the gate supply voltage is sufficient to fully enhance the power devices. Without this feature, the gates of the external power switch could be driven with a low voltage, resulting in the power switch conducting current while the channel impedance is high; this could result in very high conduction losses within the power device and could lead to power device failure.

Figure 10 UVLO protection

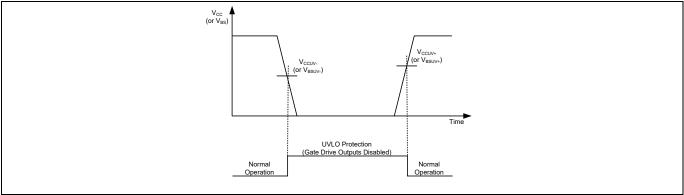

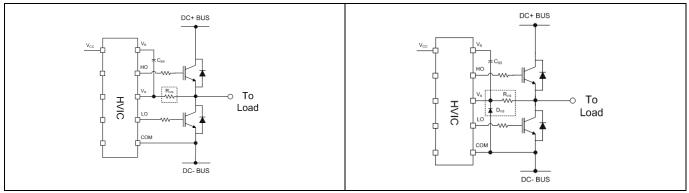

#### 5.6 Bootstrap diode

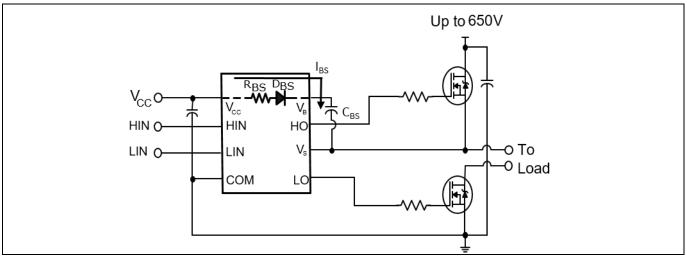

An ultra-fast bootstrap diode is monolithically integrated for establishing the high side supply. The differential resistor of the diode helps to avoid extremely high inrush currents when initially charging the bootstrap capacitor. The integrated diode with its resistrance helps save cost and improve reliability by reducing external components as shown below Figure 11 and Figure 12.

Figure 112ED210x with integrated componentsFigure 12

Standard bootstrap gate driver

The low ohmic current limiting resistor provides essential advantages over other competitor devices with high ohmic bootstrap structures. A low ohmic resistor such as in the 2ED210x family allows faster recharching of the bootstrap capacitor during periods of small duty cycles on the low side transistor. The bootstrap diode is a real pn-diode which works with all control algorithms of modern power electronics, such as trapezoidal or sinusoidal motor drives control.

#### 5.7 Calculating the bootstrap capacitance C<sub>BS</sub>

Bootstrapping is a common method of pumping charges from a low potential to a higher one. With this technique a supply voltage for the floating high side sections of the gate drive can be easily established according to Figure 13. This method has the advantage of being simple and low cost but may force some limitations on duty-cycle and on-time since they are limited by the requirement to refresh the charge in the bootstrap capacitor.Proper capacitor choice can reduce drastically these limitations.

Figure 13 Half bridge bootstrap circuit in 2ED210x

When the low side MOSFET turns on, it will force the potential of pin V<sub>s</sub> to GND. The existing difference between the voltage of the bootstrap capacitor V<sub>CBS</sub> and V<sub>CC</sub> results in a charging current I<sub>BS</sub> into the capacitor C<sub>BS</sub>. The current I<sub>BS</sub> is a pulse current and therefore the ESR of the capacitor C<sub>BS</sub> must be very small in order to avoid losses in the capacitor that result in lower lifetime of the capacitor. This pin is on high potential again after low side is turned off and high side is conducting current. But now the bootstrap diode D<sub>BS</sub> blocks a reverse current, so that the charges on the capacitor cannot flow back to the capacitor C<sub>VCC</sub>. The bootstrap diode D<sub>BS</sub> also takes over the blocking voltage between pin V<sub>B</sub> and V<sub>CC</sub>. The voltage of the bootstrap capacitor can now supply the high side gate drive sections. It is a general design rule for the location of bootstrap capacitors C<sub>BS</sub>, that they must be placed as close as possible to the IC. Otherwise, parasitic resistors and inductances may lead to voltage spikes, which may trigger the undervoltage lockout threshold of the individual high side driver section. However, all parts of the 2ED210x family, which have the UVLO also contain a filter at each supply section in order to actively avoid such undesired UVLO triggers.

The current limiting resistor  $R_{BS}$  according to Figure 13 reduces the peak of the pulse current during the low side MOSFET turn-on. The pulse current will occur at each turn-on of the low side MOSFET, so that with increasing switching frequency the capacitor  $C_{BS}$  is charged more frequently. Therefore a smaller capacitor is suitable at higher switching frequencies. The bootstrap capacitor is mainly discharged by two effects: The high side quiescent current and the gate charge of the high side MOSFET to be turned on.

The minimum size of the bootstrap capacitor is given by

$$C_{BS} = \frac{Q_{GTOT}}{\Delta V_{BS}}$$

$\Delta V_{BS}$  is the maximum allowable voltage drop at the bootstrap capacitor within a switching period, typically 1 V. It is recommended to keep the voltage drop below the undervoltage lockout (UVLO) of the high side and limit

$$\Delta V_{BS} \leq (V_{CC} - V_{F} - V_{GSmin} - V_{DSon})$$

$V_{GSmin} > V_{BSUV-}$ ,  $V_{GSmin}$  is the minimum gate source voltage we want to maintain and  $V_{BSUV-}$  is the high-side supply undervoltage negative threshold.

$V_{cc}$  is the IC voltage supply,  $V_{\text{F}}$  is bootstrapdiode forward voltage and  $V_{\text{DSon}}$  is drain-source voltage of low side MOSFET

Please note, that the value  $Q_{GTOT}$  may vary to a maximum value based on different factors as explained below and the capacitor shows voltage dependent derating behavior of its capacitance.

The influencing factors contributing  $V_{BS}$  to decrease are:

- MOSFET turn on required Gate charge (Q<sub>G</sub>)

- MOSFET gate-source leakage current (ILK\_GS)

- Floating section quiescent current (I<sub>QBS</sub>)

- Floating section leakage current (I<sub>LK</sub>)

- Bootstrap diode leakage current (I<sub>LK\_DIODE</sub>)

- Charge required by the internal level shifters  $(Q_{LS})$ : typical 1nC

- Bootstrap capacitor leakage current (I<sub>LK\_CAP</sub>)

- High side on time ( $T_{\text{HON}}$ )

Considering the above,

$$Q_{GTOT} = Q_G + Q_{LS} + \left(I_{QBS} + I_{LK_{GS}} + I_{LK} + I_{LK_{DIODE}} + I_{LK_{CAP}}\right) * T_{HON}$$

ILK\_CAP is only relevant when using an electrolytic capacitor and can be ignored if other types of capacitors are used. It is strongly recommend using at least one low ESR ceramic capacitor (paralleling electrolytic capacitor and low ESR ceramic capacitor may result in an efficient solution).

The above  $C_{BS}$  equation is valid for pulse by pulse considerations. It is easy to see, that higher capacitance values are needed, when operating continuously at small duty cycles of low side. The recommended bootstrap capacitance is therefore in the range up to 4.7  $\mu$ F for most switching frequencies. The performance of the integrated bootstrap diode supports the requirement for small bootstrap capacitances.

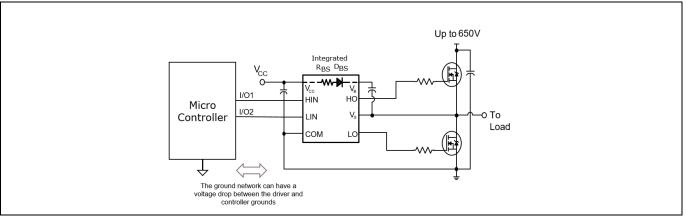

#### 5.8 Tolerant to negative tranisents on input pins

Typically the driver's ground pin is connected close to the source pin of the MOSFET or IGBT. The microcontroller which sends the HIN and LIN PWM signals refers to the same ground and in most cases there will be an offset voltage between the microcontroller ground pin and driver ground because of ground bounce. The 2ED210x family can handle negative voltage spikes up to 5 V. The recommended operating level is at negative 4 V with absolute maximum of negative 5 V. Standard half bridge or high-side/low-side gate drivers only allow negative voltage levels down to -0.3 V. The 2ED210x family has much better noise immunity capability on the input pins.

## 5.9 Negative voltage transient tolerance of VS pin

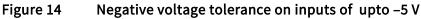

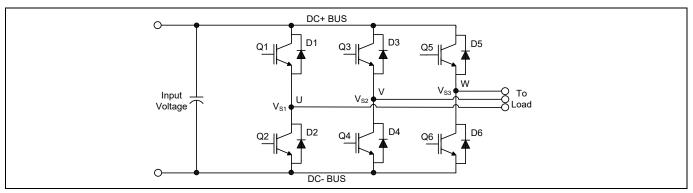

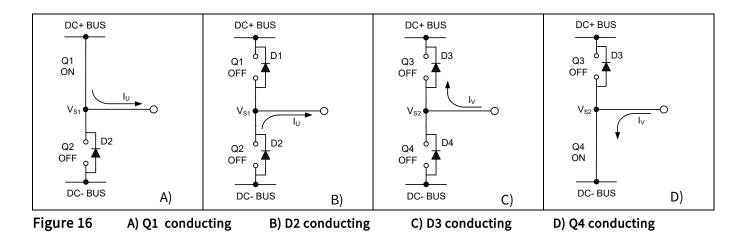

A common problem in today's high-power switching converters is the transient response of the switch node's voltage as the power switches transition on and off quickly while carrying a large current. A typical 3-phase inverter circuit is shown in Figure 15, here we define the power switches and diodes of the inverter.

If the high-side switch (e.g., the IGBT Q1 in Figure 15 and Figure 16) switches from on to off, while the U phase current is flowing to an inductive load, a current commutation occurs from high-side switch (Q1) to the diode (D2) in parallel with the low-side switch of the same inverter leg. At the same instance, the voltage node  $V_{S1}$ , swings from the positive DC bus voltage to the negative DC bus voltage.

#### Figure 15 Three phase inverter

Also when the V phase current flows from the inductive load back to the inverter (see Figure 16 C) and D)), and Q4 IGBT switches on, the current commutation occurs from D3 to Q4. At the same instance, the voltage node,  $V_{s_2}$ , swings from the positive DC bus voltage to the negative DC bus voltage.

However, in a real inverter circuit, the VS voltage swing does not stop at the level of the negative DC bus, rather it swings below the level of the negative DC bus. This undershoot voltage is called "negative V<sub>s</sub> transient"

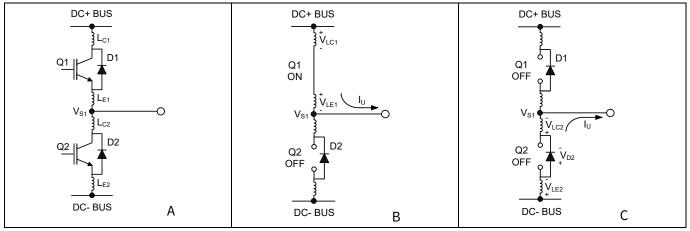

The circuit shown in Figure 17-A depicts one leg of the three phase inverter; Figure 17-B and 17-C show a simplified illustration of the commutation of the current between Q1 and D2. The parasitic inductances in the power circuit from the die bonding to the PCB tracks are lumped together in  $L_c$  and  $L_E$  for each IGBT. When the high-side switch is on,  $V_{S1}$  is below the DC+ voltage by the voltage drops associated with the power switch and the parasitic elements of the circuit. When the high-side power switch turns off, the load current momentarily flows in the low-side freewheeling diode due to the inductive load connected to  $V_{S1}$  (the load is not shown in these figures). This current flows from the DC- BUS (which is connected to the COM pin of the HVIC) to the load and a negative voltage between  $V_{S1}$  and the DC- BUS is induced (i.e., the COM pin of the HVIC is at a higher potential than the  $V_S$  pin).

Figure 17 Figure A shows the parasitic elements. Figure B shows the generation of V<sub>s</sub> positive. Figure C shows the generation of V<sub>s</sub> negative

#### 5.10 NTSOA – Negative Transient Safe Operating Area

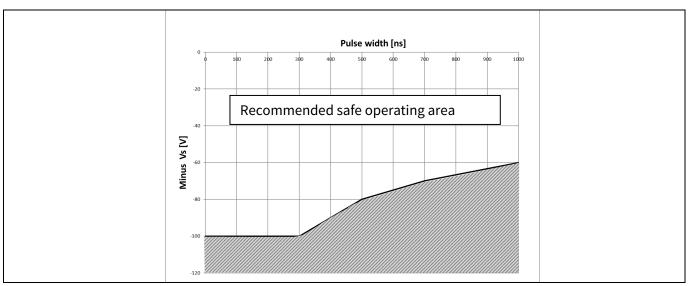

In a typical motor drive system, dV/dt is typically designed to be in the range of 3 – 5 V / ns. The negative VS transient voltage can exceed this range during some events such as short circuit and over-current shutdown, when di/dt is greater than in normal operation.

Infineon's HVICs have been designed for the robustness required in many of today's demanding applications. An indication of the 2ED2106 (4) S06F (J)'s robustness can be seen in Figure 18, where the 2ED2106 (4) S06F (J)'s Safe Operating Area is shown at  $V_{BS}$ =15 V based on repetitive negative VS spikes. A negative VS transient voltage falling in the grey area (outside SOA) may lead to IC permanent damage; viceversa unwanted functional anomalies or permanent damage to the IC do not appear if negative VS transients fall inside the SOA.

Figure 18 Negative VS transient SOA for 2ED2106 (4) S06F (J) @ VBS = 15 V

Even though the 2ED2106 (4) S06F (J) has been shown able to handle these large negative VS transient conditions, it is highly recommended that the circuit designer always limit the negative VS transients as much as possible by careful PCB layout and component use.

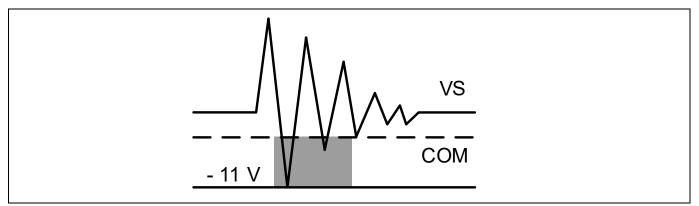

# 5.11 Higher headroom for input to output signal transmission with logic operation upto -11 V

If there is not enough voltage for the level shifter to transmit a valid signal to the high side. High side driver doesn't turn on. The level shifter circuit is with respect to COM (refer to Block Diagram on page 4), the voltage from  $V_B$  to COM is the supply voltage of level shifter. Under the condition of VS is negative voltage with respect to COM, the voltage of VS - COM is decreased, as shown in Figure 19. There is a minimum operational supply voltage of level shifter, if the supply voltage of level shifter is too low, the level shifter cannot pass through HIN signal to HO. The specification of VS is -11 V as the internal structure allows a voltage difference of 15 V between Vcc and COM pins. If  $V_B - V_S$  voltage is different, the minimum VS voltage changes accordingly.

Figure 19 Headroom for HV level shifter data transmission

#### 5.12 Maximum switching frequency

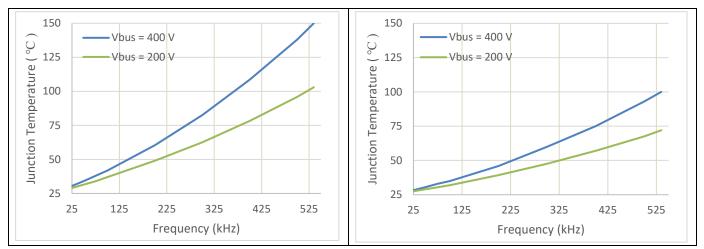

The 2ED2106 (4) S06F (J) is capable of switching at higher frequencies as compared to standard half-bridge or high side / low side gate drivers. They are available in two packages, the PG-DSO-8 and the PG-DSO-14. It is essential to ensure that the component is not thermally overloaded when operating at higher frequencies. This can be checked by means of the thermal resistance junction to ambient and the calculation or measurement of the dissipated power. The thermal resistance is given in the datasheet (section 4) and refers to a specific layout. Changes of this layout may lead to an increased thermal resistance, which will reduce the total dissipated power of the driver IC. One should therefore do temperature measurements in order to avoid thermal overload under application relevant conditions of ambient temperature and housing.

The maximum chip temperature  $T_J$  can be calculated with

$T_I = \text{Pd} \cdot Rth_{IA} + T_{A \max}$ , where  $T_{A_{\max}}$  is the maximum ambient temperature.

The dissipated power Pd by the driver IC is a combination of several sources. These are explained in detail in the application note "2ED2106 (4) S06F (J) (HVICs)"

Here is the example of the figures which estimates the gate driver IC junction temperature when switching a given MOSFET at different switching frequencies.

\*Assumptions for above curves: LLC topology, Power switch = IPP60R600P6,  $T_a = 25 \text{ °C}$ ,  $V_{BUS} = 400 \text{ V}$ ,  $V_{CC} = 12 \text{ V}$ ,  $R_{gon} = 3.9 \Omega$ ,  $R_{goff} = 1 \Omega$

#### Figure 20 Estimated T<sub>J</sub> vs. Frequencies (Left: DSO - 8, Right: DSO - 14)

#### 5.13 PCB layout tips

<u>Distance between high and low voltage components</u>: It's strongly recommended to place the components tied to the floating voltage pins ( $V_B$  and  $V_S$ ) near the respective high voltage portions of the device. Please see the Case Outline information in this datasheet for the details.

<u>Ground Plane</u>: In order to minimize noise coupling, the ground plane should not be placed under or near the high voltage floating side.

<u>Gate Drive Loops</u>: Current loops behave like antennas and are able to receive and transmit EM noise (see Figure 21). In order to reduce the EM coupling and improve the power switch turn on/off performance, the gate drive loops must be reduced as much as possible. Moreover, current can be injected inside the gate drive loop via the IGBT collector-to-gate parasitic capacitance. The parasitic auto-inductance of the gate loop contributes to developing a voltage across the gate-emitter, thus increasing the possibility of a self turn-on effect.

Figure 21 Avoid antenna loops

<u>Supply Capacitor</u>: It is recommended to place a bypass capacitor ( $C_{IN}$ ) between the  $V_{CC}$  and COM pins. A ceramic 1µF ceramic capacitor is suitable for most applications. This component should be placed as close as possible to the pins in order to reduce parasitic elements.

<u>Routing and Placement</u>: Power stage PCB parasitic elements can contribute to large negative voltage transients at the switch node; it is recommended to limit the phase voltage negative transients. In order to avoid such conditions, it is recommended to 1) minimize the high-side emitter to low-side collector distance, and 2) minimize the low-side emitter to negative bus rail stray inductance. However, where negative VS spikes remain excessive, further steps may be taken to reduce the spike. This includes placing a resistor (5  $\Omega$  or less) between the VS pin and the switch node (see Figure 22- A), and in some cases using a clamping diode between COM and V<sub>s</sub> (see Figure 22- B). See DT04-4 at <u>www.infineon.com</u> for more detailed explanations.

# Figure 22 Resistor between the VS pin and the switch node and clamping diode between COM and VS

## 6 Qualification information<sup>1</sup>

#### Table 7Qualification information

| Qualification level        |                      | Industrial <sup>2</sup>                                                                                          |                           |  |  |

|----------------------------|----------------------|------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|

|                            |                      | Note: This family of ICs has passed JEDEC's Industrial qualification. Consumer qualification level is granted by |                           |  |  |

|                            |                      | extension of the higher Industrial level.                                                                        |                           |  |  |

| Moisture sensitivity level |                      | DSO-8/-14                                                                                                        | MSL3 <sup>3</sup> , 260°C |  |  |

|                            |                      | D30-6/-14                                                                                                        | (per IPC/JEDEC J-STD-020) |  |  |

|                            | Charged device model | Class C3 (1.0 kV)                                                                                                |                           |  |  |

| ESD                        | Charged device model | (per JEDEC standard JS-002)                                                                                      |                           |  |  |

| ESD                        | Human bady model     | Class 2 (1.5 kV)                                                                                                 |                           |  |  |

|                            | Human body model     | (per JEDEC standard JS-001)                                                                                      |                           |  |  |

| IC latch-up test           |                      | Class II Level A                                                                                                 |                           |  |  |

|                            |                      | (per JESD85)                                                                                                     |                           |  |  |

| RoHS compliant             |                      | Yes                                                                                                              |                           |  |  |

## 7 Related products

#### Table 8

| Product                      | Description                                                                                                     |

|------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Gate Driver ICs              |                                                                                                                 |

| <u>6EDL04I06 /</u>           | 600 V, 3 phase level shift thin-film SOI gate driver with integrated high speed, low R <sub>BSD</sub> bootstrap |

| 6EDL04N06                    | diodes with over-current protection (OCP), 240/420 mA source/sink current drive, Fault reporting,               |

|                              | and Enable for MOSFET or IGBT switches.                                                                         |

| 2EDL23I06 /                  | 600 V, Half-bridge thin-film SOI level shift gate driver with integrated high speed, low                        |

| 2EDL23N06                    | R <sub>BSD</sub> bootstrap diode, with over-current protection (OCP), 2.3/2.8 A source/sink current driver, and |

|                              | one pin Enable/Fault function for MOSFET or IGBT switches.                                                      |

| Power Switches               |                                                                                                                 |

| <u>IKD04N60R</u> / <u>RF</u> | 650 V TRENCHSTOP™ IGBT with integrated diode in PG-TO252-3 package                                              |

| IKD06N65ET6                  | 650 V TRENCHSTOP™ IGBT with integrated diode in DPAK                                                            |

| IPD65R950CFD                 | 650 V CoolMOS CFD2 with integrated fast body diode in DPAK                                                      |

| IPN50R950CE                  | 500 V CoolMOS CE Superjunction MOSFET in PG-SOT223 package                                                      |

| iMOTION™ Contro              | llers                                                                                                           |

| IRMCK099                     | iMOTION™ Motor control IC for variable speed drives utilizing sensor-less Field Oriented Control                |

|                              | (FOC) for Permanent Magnet Synchronous Motors (PMSM).                                                           |

| <u>IMC101T</u>               | High performance Motor Control IC for variable speed drives based on field oriented control (FOC)               |

|                              | of permanent magnet synchronous motors (PMSM).                                                                  |

<sup>&</sup>lt;sup>1</sup> Qualification standards can be found at Infineon's web site <u>www.infineon.com</u>

<sup>&</sup>lt;sup>2</sup> Higher qualification ratings may be available should the user have such requirements. Please contact your Infineon sales representative for further information.

<sup>&</sup>lt;sup>3</sup> Higher MSL ratings may be available for the specific package types listed here. Please contact your Infineon sales representative for further information.

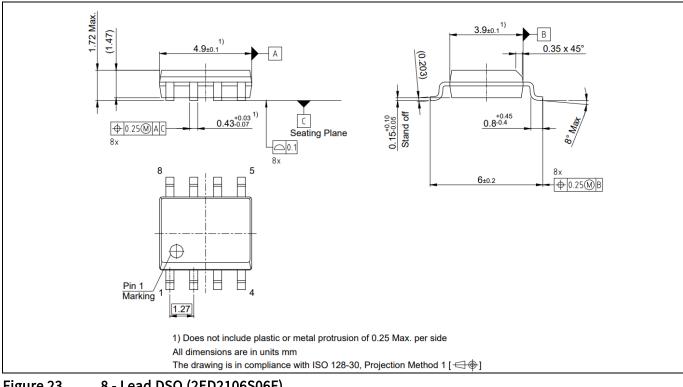

#### Package details 8

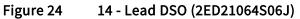

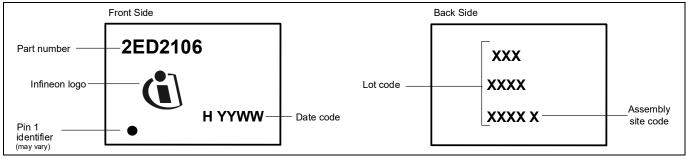

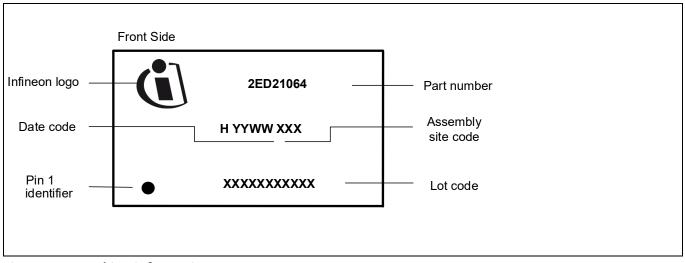

## 9 Part marking information

Figure 25 Marking information PG-DSO-8

Figure 26 Marking information PG-DSO-14

## 10 Additional documentation and resources

Several technical documents related to the use of HVICs are available at <u>www.infineon.com</u>; use the Site Search function and the document number to quickly locate them. Below is a short list of some of these documents.

Application Notes: <u>Understanding HVIC Datasheet Specifications</u> <u>HV Floating MOS-Gate Driver ICs</u> <u>Use Gate Charge to Design the Gate Drive Circuit for Power MOSFETs and IGBTs</u> <u>Bootstrap Network Analysis: Focusing on the Integrated Bootstrap Functionality</u>

Design Tips: <u>Using Monolithic High Voltage Gate Drivers</u> <u>Alleviating High Side Latch on Problem at Power Up</u> <u>Keeping the Bootstrap Capacitor Charged in Buck Converters</u> <u>Managing Transients in Control IC Driven Power Stages</u> <u>Simple High Side Drive Provides Fast Switching and Continuous On-Time</u>

#### 10.1 Infineon online forum resources

The Gate Driver Forum is live at Infineon Forums (<u>www.infineonforums.com</u>). This online forum is where the Infineon gate driver IC community comes to the assistance of our customers to provide technical guidance – how to use gate drivers ICs, existing and new gate driver information, application information, availability of demo boards, online training materials for over 500 gate driver ICs. The Gate Driver Forum also serves as a repository of FAQs where the user can review solutions to common or specific issues faced in similar applications.

Register online at the Gate Driver Forum and learn the nuances of efficiently driving a power switch in any given power electronic application.

# 11 Revision history

| Document version | Date of release | Description of changes                                            |

|------------------|-----------------|-------------------------------------------------------------------|

| 2.00             | July 30, 2019   | Final Datasheet                                                   |

| 2.10             | Sep. 12, 2019   | Revised parameter values in Table 7 to match the test conditions. |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2019-09-12

Published by Infineon Technologies AG 81726 Munich, Germany

© 2019 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

#### **Document reference**

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.