# LMD18200

LMD18200 3A, 55V H-Bridge

Literature Number: SNVS091E

## LMD18200

# 3A, 55V H-Bridge

## **General Description**

The LMD18200 is a 3A H-Bridge designed for motion control applications. The device is built using a multi-technology process which combines bipolar and CMOS control circuitry with DMOS power devices on the same monolithic structure. Ideal for driving DC and stepper motors; the LMD18200 accommodates peak output currents up to 6A. An innovative circuit which facilitates low-loss sensing of the output current has been implemented.

### **Features**

- Delivers up to 3A continuous output

- Operates at supply voltages up to 55V

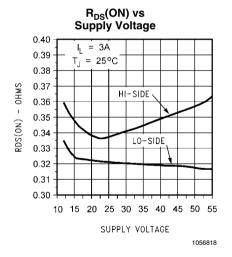

- Low R<sub>DS</sub>(ON) typically 0.33Ω per switch at 3A

- TTL and CMOS compatible inputs

- No "shoot-through" current

- Thermal warning flag output at 145°C

- Thermal shutdown (outputs off) at 170°C

- Internal clamp diodes

- Shorted load protection

- Internal charge pump with external bootstrap capability

### **Applications**

- DC and stepper motor drives

- Position and velocity servomechanisms

- Factory automation robots

- Numerically controlled machinery

- Computer printers and plotters

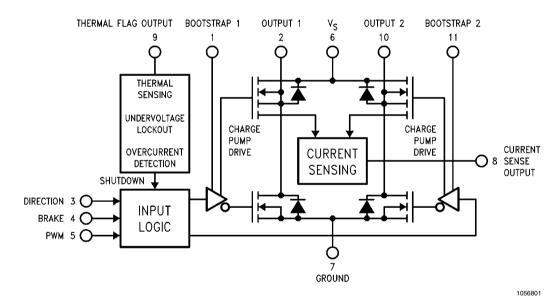

## **Functional Diagram**

FIGURE 1. Functional Block Diagram of LMD18200

# **Connection Diagram and Ordering Information**

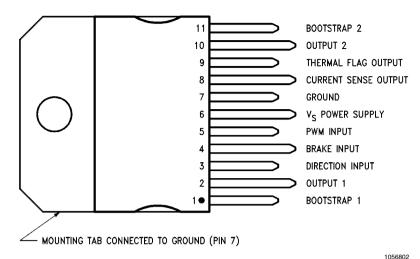

11-Lead TO-220 Package Top View Order Number LMD18200T See NS Package TA11B

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Total Supply Voltage ( $V_S$ , Pin 6) 60V Voltage at Pins 3, 4, 5, 8 and 9 12V Voltage at Bootstrap Pins (Pins 1 and 11)  $V_{OUT}$  +16V

Peak Output Current (200 ms) 6A Continuous Output Current (*Note 2*) 3A  $\begin{array}{lll} \mbox{Power Dissipation (Note 3)} & 25\mbox{W} \\ \mbox{Power Dissipation ($T_A$ = $25^{\circ}$C, Free Air)} & 3\mbox{W} \\ \mbox{Junction Temperature, $T_{J(max)}$} & 150^{\circ}$C \\ \mbox{ESD Susceptibility (Note 4)} & 1500\mbox{V} \\ \mbox{Storage Temperature, $T_{STG}$} & -40^{\circ}$C to +150^{\circ}$C \\ \mbox{Lead Temperature (Soldering, 10 sec.)} & 300^{\circ}$C \\ \end{array}$

### **Operating Ratings** (Note 1)

### **Electrical Characteristics** (Note 5)

The following specifications apply for  $V_S = 42V$ , unless otherwise specified. **Boldface** limits apply over the entire operating temperature range,  $-40^{\circ}\text{C} \le T_J \le +125^{\circ}\text{C}$ , all other limits are for  $T_A = T_J = 25^{\circ}\text{C}$ .

| Symbol               | Parameter                       | Conditions                                   | Тур  | Limit            | Units    |

|----------------------|---------------------------------|----------------------------------------------|------|------------------|----------|

| R <sub>DS</sub> (ON) | Switch ON Resistance            | Output Current = 3A (Note 6)                 | 0.33 | 0.40/ <b>0.6</b> | Ω (max)  |

| R <sub>DS</sub> (ON) | Switch ON Resistance            | Output Current = 6A (Note 6)                 | 0.38 | 0.45/ <b>0.6</b> | Ω (max)  |

| V <sub>CLAMP</sub>   | Clamp Diode Forward Drop        | Clamp Current = 3A (Note 6)                  | 1.2  | 1.5              | V (max)  |

| V <sub>IL</sub>      | Logic Low Input Voltage         | Pins 3, 4, 5                                 |      | -0.1             | V (min)  |

|                      |                                 |                                              |      | 0.8              | V (max)  |

| I <sub>IL</sub>      | Logic Low Input Current         | $V_{IN} = -0.1V$ , Pins = 3, 4, 5            |      | -10              | μA (max) |

| V <sub>IH</sub>      | Logic High Input Voltage        | Pins 3, 4, 5                                 |      | 2                | V (min)  |

|                      |                                 |                                              |      | 12               | V (max)  |

| I <sub>IH</sub>      | Logic High Input Current        | $V_{IN} = 12V$ , Pins = 3, 4, 5              |      | 10               | μA (max) |

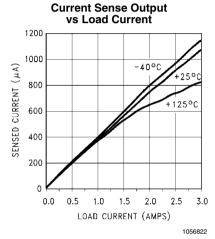

|                      | Current Sense Output            | I <sub>OUT</sub> = 1A ( <i>Note 8</i> )      | 377  | 325/ <b>300</b>  | μA (min) |

|                      |                                 |                                              |      | 425/ <b>450</b>  | μΑ (max) |

|                      | Current Sense Linearity         | 1A ≤ I <sub>OUT</sub> ≤ 3A ( <i>Note 7</i> ) | ±6   | ±9               | %        |

|                      | Undervoltage Lockout            | Outputs turn OFF                             |      | 9                | V (min)  |

|                      |                                 |                                              |      | 11               | V (max)  |

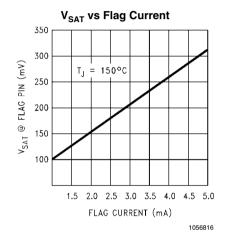

| $T_JW$               | Warning Flag Temperature        | Pin 9 ≤ 0.8V, $I_L = 2 \text{ mA}$           | 145  |                  | °C       |

| V <sub>F</sub> (ON)  | Flag Output Saturation Voltage  | $T_J = T_{JW}, I_L = 2 \text{ mA}$           | 0.15 |                  | V        |

| I <sub>F</sub> (OFF) | Flag Output Leakage             | V <sub>F</sub> = 12V                         | 0.2  | 10               | μA (max) |

| T <sub>JSD</sub>     | Shutdown Temperature            | Outputs Turn OFF                             | 170  |                  | °C       |

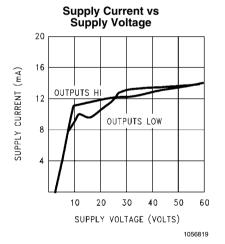

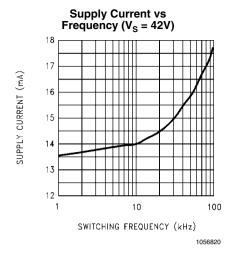

| I <sub>S</sub>       | Quiescent Supply Current        | All Logic Inputs Low                         | 13   | 25               | mA (max) |

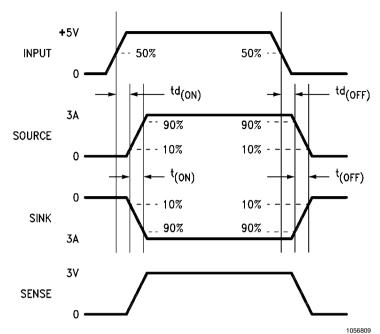

| t <sub>Don</sub>     | Output Turn-On Delay Time       | Sourcing Outputs, I <sub>OUT</sub> = 3A      | 300  |                  | ns       |

|                      |                                 | Sinking Outputs, I <sub>OUT</sub> = 3A       | 300  |                  | ns       |

| t <sub>on</sub>      | Output Turn-On Switching Time   | Bootstrap Capacitor = 10 nF                  |      |                  |          |

|                      |                                 | Sourcing Outputs, I <sub>OUT</sub> = 3A      | 100  |                  | ns       |

|                      |                                 | Sinking Outputs, I <sub>OUT</sub> = 3A       | 80   |                  | ns       |

| t <sub>Doff</sub>    | Output Turn-Off Delay Times     | Sourcing Outputs, I <sub>OUT</sub> = 3A      | 200  |                  | ns       |

|                      |                                 | Sinking Outputs, I <sub>OUT</sub> = 3A       | 200  |                  | ns       |

| t <sub>off</sub>     | Output Turn-Off Switching Times | Bootstrap Capacitor = 10 nF                  |      |                  |          |

|                      |                                 | Sourcing Outputs, I <sub>OUT</sub> = 3A      | 75   |                  | ns       |

|                      |                                 | Sinking Outputs, I <sub>OUT</sub> = 3A       | 70   |                  | ns       |

| t <sub>pw</sub>      | Minimum Input Pulse Width       | Pins 3, 4 and 5                              | 1    |                  | μs       |

| t <sub>cpr</sub>     | Charge Pump Rise Time           | No Bootstrap Capacitor                       | 20   |                  | μs       |

### **Electrical Characteristics Notes**

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its rated operating conditions.

Note 2: See Application Information for details regarding current limiting.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is a function of  $T_{J_{(max)}}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_{D_{(max)}} = (T_{J_{(max)}} - T_A)/\theta_{JA}$ , or the number given in the Absolute Ratings, whichever is lower. The typical thermal resistance from junction to case  $(\theta_{JC})$  is 1.0°C/W and from junction to ambient  $(\theta_{JA})$  is 30°C/W. For guaranteed operation  $T_{J_{(max)}} = 125$ °C.

Note 4: Human-body model, 100 pF discharged through a 1.5 kΩ resistor. Except Bootstrap pins (pins 1 and 11) which are protected to 1000V of ESD.

Note 5: All limits are 100% production tested at 25°C. Temperature extreme limits are guaranteed via correlation using accepted SQC (Statistical Quality Control) methods. All limits are used to calculate AOQL, (Average Outgoing Quality Level).

Note 6: Output currents are pulsed (t<sub>w</sub> < 2 ms, Duty Cycle < 5%).

Note 7: Regulation is calculated relative to the current sense output value with a 1A load.

Note 8: Selections for tighter tolerance are available. Contact factory.

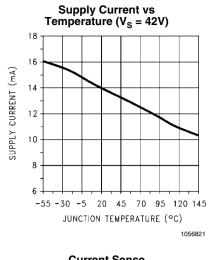

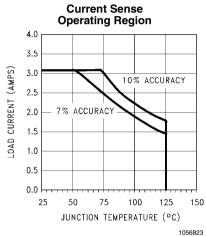

### **Typical Performance Characteristics**

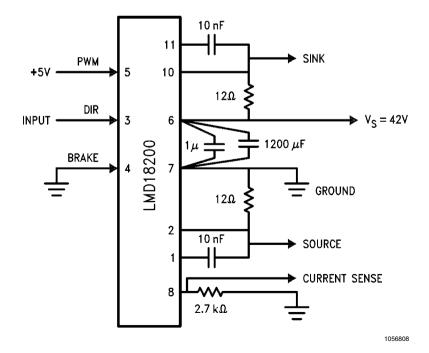

## **Test Circuit**

5

## **Switching Time Definitions**

## **Pinout Description**

(See Connection Diagram)

**Pin 1, BOOTSTRAP 1 Input:** Bootstrap capacitor pin for half H-bridge number 1. The recommended capacitor (10 nF) is connected between pins 1 and 2.

Pin 2, OUTPUT 1: Half H-bridge number 1 output.

**Pin 3, DIRECTION Input:** See *Table 1*. This input controls the direction of current flow between OUTPUT 1 and OUT-PUT 2 (pins 2 and 10) and, therefore, the direction of rotation of a motor load.

**Pin 4, BRAKE Input:** See *Table 1*. This input is used to brake a motor by effectively shorting its terminals. When braking is desired, this input is taken to a logic high level and it is also necessary to apply logic high to PWM input, pin 5. The drivers that short the motor are determined by the logic level at the DIRECTION input (Pin 3): with Pin 3 logic high, both current sourcing output transistors are ON; with Pin 3 logic low, both current sinking output transistors are ON. All output transistors can be turned OFF by applying a logic high to Pin 4 and a logic low to PWM input Pin 5; in this case only a small bias current (approximately –1.5 mA) exists at each output pin.

**Pin 5, PWM Input:** See *Table 1*. How this input (and DIRECTION input, Pin 3) is used is determined by the format of the PWM Signal.

Pin 6, V<sub>S</sub> Power Supply

**Pin 7, GROUND Connection:** This pin is the ground return, and is internally connected to the mounting tab.

**Pin 8, CURRENT SENSE Output:** This pin provides the sourcing current sensing output signal, which is typically 377 μA/A.

Pin 9, THERMAL FLAG Output: This pin provides the thermal warning flag output signal. Pin 9 becomes active-low at

145°C (junction temperature). However the chip will not shut itself down until 170°C is reached at the junction.

Pin 10, OUTPUT 2: Half H-bridge number 2 output.

**Pin 11, BOOTSTRAP 2 Input:** Bootstrap capacitor pin for Half H-bridge number 2. The recommended capacitor (10 nF) is connected between pins 10 and 11.

**TABLE 1. Logic Truth Table**

| PWM | Dir | Brake | Active Output Drivers |

|-----|-----|-------|-----------------------|

| Н   | Н   | L     | Source 1, Sink 2      |

| Н   | L   | L     | Sink 1, Source 2      |

| L   | Х   | L     | Source 1, Source 2    |

| Н   | Н   | Н     | Source 1, Source 2    |

| Н   | L   | Н     | Sink 1, Sink 2        |

| L   | Х   | Н     | NONE                  |

# **Application Information**

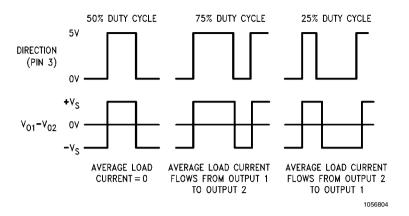

#### **TYPES OF PWM SIGNALS**

The LMD18200 readily interfaces with different forms of PWM signals. Use of the part with two of the more popular forms of PWM is described in the following paragraphs.

Simple, locked anti-phase PWM consists of a single, variable duty-cycle signal in which is encoded both direction and amplitude information (see *Figure 2*). A 50% duty-cycle PWM signal represents zero drive, since the net value of voltage (integrated over one period) delivered to the load is zero. For the LMD18200, the PWM signal drives the direction input (pin 3) and the PWM input (pin 5) is tied to logic high.

FIGURE 2. Locked Anti-Phase PWM Control

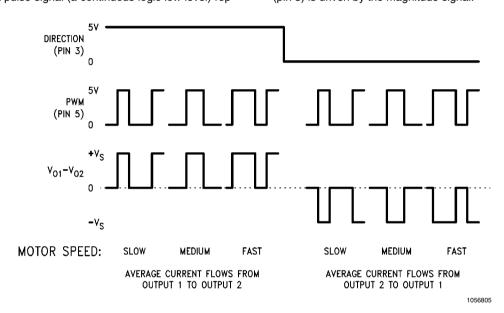

**Sign/magnitude PWM** consists of separate direction (sign) and amplitude (magnitude) signals (see *Figure 3*). The (absolute) magnitude signal is duty-cycle modulated, and the absence of a pulse signal (a continuous logic low level) rep-

resents zero drive. Current delivered to the load is proportional to pulse width. For the LMD18200, the DIRECTION input (pin 3) is driven by the sign signal and the PWM input (pin 5) is driven by the magnitude signal.

FIGURE 3. Sign/Magnitude PWM Control

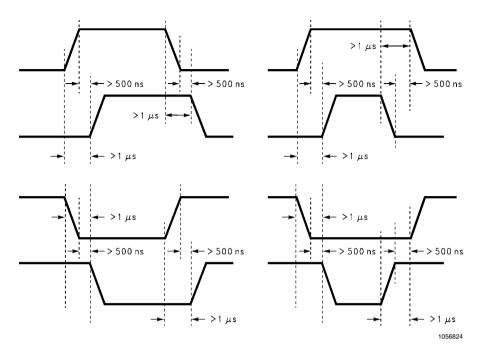

#### SIGNAL TRANSITION REQUIREMENTS

To ensure proper internal logic performance, it is good practice to avoid aligning the falling and rising edges of input signals. A delay of at least 1 µsec should be incorporated be-

tween transitions of the Direction, Brake, and/or PWM input signals. A conservative approach is be sure there is at least 500ns delay between the end of the first transition and the beginning of the second transition. See *Figure 4*.

FIGURE 4. Transitions in Brake, Direction, or PWM Must Be Separated By At Least 1 usec

#### **USING THE CURRENT SENSE OUTPUT**

The CURRENT SENSE output (pin 8) has a sensitivity of 377  $\mu$ A per ampere of output current. For optimal accuracy and linearity of this signal, the value of voltage generating resistor between pin 8 and ground should be chosen to limit the maximum voltage developed at pin 8 to 5V, or less. The maximum voltage compliance is 12V.

It should be noted that the recirculating currents (free wheeling currents) are ignored by the current sense circuitry. Therefore, only the currents in the upper sourcing outputs are sensed.

#### **USING THE THERMAL WARNING FLAG**

The THERMAL FLAG output (pin 9) is an open collector transistor. This permits a wired OR connection of thermal warning flag outputs from multiple LMD18200's, and allows the user to set the logic high level of the output signal swing to match system requirements. This output typically drives the interrupt input of a system controller. The interrupt service routine would then be designed to take appropriate steps, such as reducing load currents or initiating an orderly system shutdown. The maximum voltage compliance on the flag pin is 12V.

#### SUPPLY BYPASSING

During switching transitions the levels of fast current changes experienced may cause troublesome voltage transients across system stray inductance.

It is normally necessary to bypass the supply rail with a high quality capacitor(s) connected as close as possible to the  $V_{\rm S}$  Power Supply (Pin 6) and GROUND (Pin 7). A 1  $\mu F$  high-frequency ceramic capacitor is recommended. Care should be taken to limit the transients on the supply pin below the Absolute Maximum Rating of the device. When operating the chip at supply voltages above 40V a voltage suppressor (transorb) such as P6KE62A is recommended from supply to ground. Typically the ceramic capacitor can be eliminated in the presence of the voltage suppressor. Note that when driv-

ing high load currents a greater amount of supply bypass capacitance (in general at least 100  $\mu F$  per Amp of load current) is required to absorb the recirculating currents of the inductive loads.

#### **CURRENT LIMITING**

Current limiting protection circuitry has been incorporated into the design of the LMD18200. With any power device it is important to consider the effects of the substantial surge currents through the device that may occur as a result of shorted loads. The protection circuitry monitors this increase in current (the threshold is set to approximately 10 Amps) and shuts off the power device as quickly as possible in the event of an overload condition. In a typical motor driving application the most common overload faults are caused by shorted motor windings and locked rotors. Under these conditions the inductance of the motor (as well as any series inductance in the V<sub>CC</sub> supply line) serves to reduce the magnitude of a current surge to a safe level for the LMD18200. Once the device is shut down, the control circuitry will periodically try to turn the power device back on. This feature allows the immediate return to normal operation in the event that the fault condition has been removed. While the fault remains however, the device will cycle in and out of thermal shutdown. This can create voltage transients on the  $V_{\rm CC}$  supply line and therefore proper supply bypassing techniques are required.

The most severe condition for any power device is a direct, hard-wired ("screwdriver") long term short from an output to ground. This condition can generate a surge of current through the power device on the order of 15 Amps and require the die and package to dissipate up to 500 Watts of power for the short time required for the protection circuitry to shut off the power device. This energy can be destructive, particularly at higher operating voltages (>30V) so some precautions are in order. Proper heat sink design is essential and it is normally necessary to heat sink the  $V_{\rm CC}$  supply pin (pin 6) with 1 square inch of copper on the PCB.

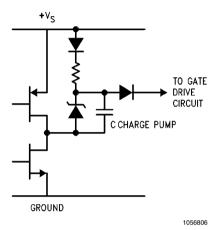

# INTERNAL CHARGE PUMP AND USE OF BOOTSTRAP CAPACITORS

To turn on the high-side (sourcing) DMOS power devices, the gate of each device must be driven approximately 8V more positive than the supply voltage. To achieve this an internal charge pump is used to provide the gate drive voltage. As shown in *Figure 5*, an internal capacitor is alternately switched to ground and charged to about 14V, then switched to V supply thereby providing a gate drive voltage greater than V supply. This switching action is controlled by a continuously running internal 300 kHz oscillator. The rise time of this drive voltage is typically 20 µs which is suitable for operating frequencies up to 1 kHz.

FIGURE 5. Internal Charge Pump Circuitry

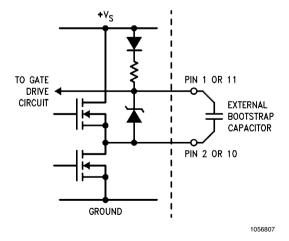

For higher switching frequencies, the LMD18200 provides for the use of external bootstrap capacitors. The bootstrap principle is in essence a second charge pump whereby a large value capacitor is used which has enough energy to quickly charge the parasitic gate input capacitance of the power device resulting in much faster rise times. The switching action is accomplished by the power switches themselves *Figure* 6. External 10 nF capacitors, connected from the outputs to the bootstrap pins of each high-side switch provide typically less than 100 ns rise times allowing switching frequencies up to 500 kHz.

**FIGURE 6. Bootstrap Circuitry**

#### INTERNAL PROTECTION DIODES

A major consideration when switching current through inductive loads is protection of the switching power devices from the large voltage transients that occur. Each of the four switches in the LMD18200 have a built-in protection diode to clamp transient voltages exceeding the positive supply or ground to a safe diode voltage drop across the switch.

The reverse recovery characteristics of these diodes, once the transient has subsided, is important. These diodes must come out of conduction quickly and the power switches must be able to conduct the additional reverse recovery current of the diodes. The reverse recovery time of the diodes protecting the sourcing power devices is typically only 70 ns with a reverse recovery current of 1A when tested with a full 6A of forward current through the diode. For the sinking devices the recovery time is typically 100 ns with 4A of reverse current under the same conditions.

### **Typical Applications**

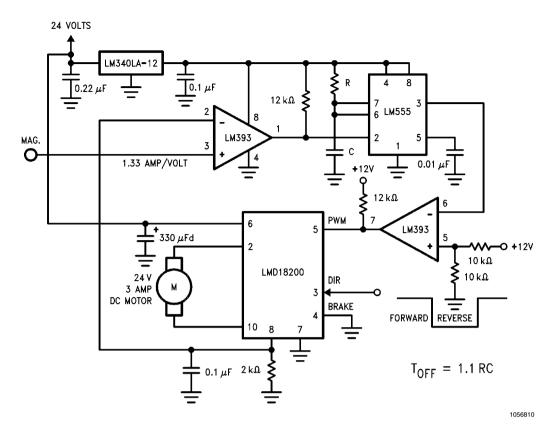

#### **FIXED OFF-TIME CONTROL**

This circuit controls the current through the motor by applying an average voltage equal to zero to the motor terminals for a fixed period of time, whenever the current through the motor exceeds the commanded current. This action causes the motor current to vary slightly about an externally controlled average level. The duration of the Off-period is adjusted by the resistor and capacitor combination of the LM555. In this circuit the Sign/Magnitude mode of operation is implemented (see Types of PWM Signals).

FIGURE 7. Fixed Off-Time Control

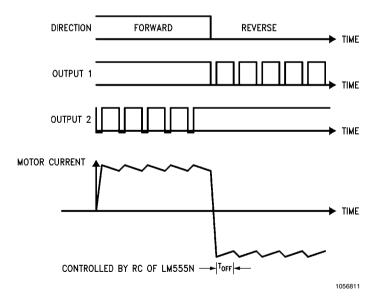

FIGURE 8. Switching Waveforms

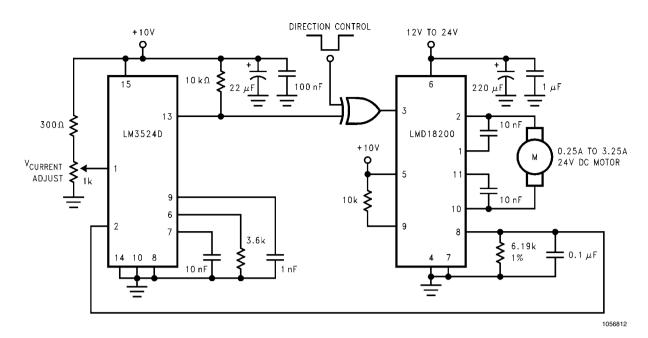

#### **TORQUE REGULATION**

Locked Anti-Phase Control of a brushed DC motor. Current sense output of the LMD18200 provides load sensing. The  $\,$

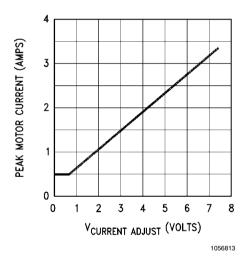

LM3524D is a general purpose PWM controller. The relationship of peak motor current to adjustment voltage is shown in *Figure 10*.

FIGURE 9. Locked Anti-Phase Control Regulates Torque

FIGURE 10. Peak Motor Current vs Adjustment Voltage

11

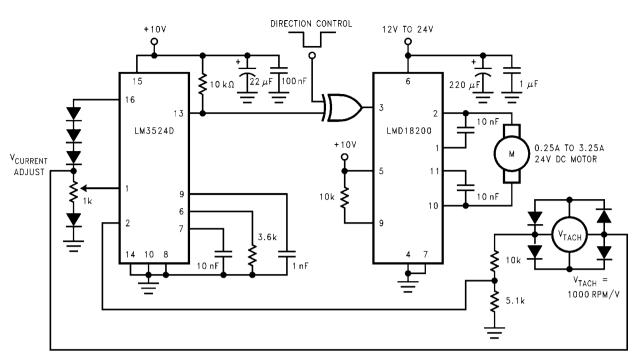

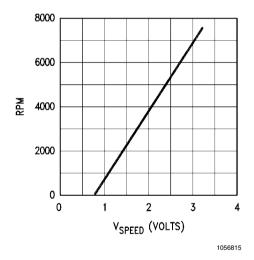

#### **VELOCITY REGULATION**

Utilizes tachometer output from the motor to sense motor speed for a locked anti-phase control loop. The relationship

of motor speed to the speed adjustment control voltage is shown in *Figure 12*.

1056814

FIGURE 11. Regulate Velocity with Tachometer Feedback

FIGURE 12. Motor Speed vs Control Voltage

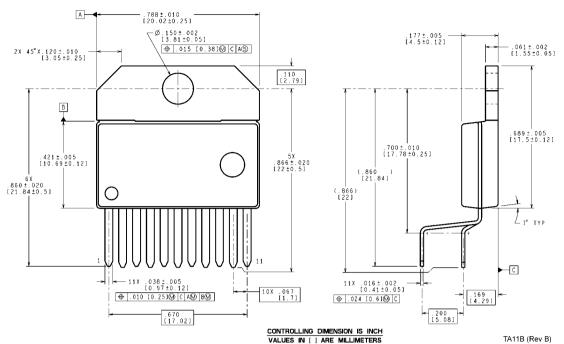

# Physical Dimensions inches (millimeters) unless otherwise noted

CONTROLLING DIMENSION IS INCH-VALUES IN [ ] ARE MILLIMETERS

11-Lead TO-220 Power Package (T)

Order Number LMD18200T

NS Package Number TA11B

### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2011 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

# Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical

Interface interface.ti.com Security www.ti.com/security

Logic Space, Avionics and Defense www.ti.com/space-avionics-defense

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers Microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connectivity www.ti.com/wirelessconnectivity

TI E2E Community Home Page <u>e2e.ti.com</u>