### Product Change Notification / SYST-06XMYM994

Date:

07-Aug-2020

**PCN Type:**

**Document Change**

### **Notification Subject:**

Data Sheet - MCP16501 Low Cost PMIC for SAMA5DX/SAM9X6 MPUs

### **Affected CPNs:**

SYST-06XMYM994\_Affected\_CPN\_08072020.pdf SYST-06XMYM994\_Affected\_CPN\_08072020.csv

### **Notification Text:**

SYST-06XMYM994

Microchip has released a new Product Documents for the MCP16501 Low Cost PMIC for SAMA5DX/SAM9X6 MPUs of devices. If you are using one of these devices please read the document located at MCP16501 Low Cost PMIC for SAMA5DX/ SAM9X6 MPUs.

**Notification Status: Final**

**Description of Change:**

1) Minor modifications to PIS section **Impacts to Data Sheet:** None

**Reason for Change:** To Improve Manufacturability **Change Implementation Status:** Complete

**Date Document Changes Effective:** 07 August 2020

**NOTE:** Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

### **Attachments:**

MCP16501 Low Cost PMIC for SAMA5DX/ SAM9X6 MPUs

| Please contact your local Microchip sales office with questions or concerns regarding this notification.                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Terms and Conditions:                                                                                                                                                                                                                                                                       |

| If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN</u> home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section. |

| If you wish to change your PCN profile, including opt out, please go to the PCN home page select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.                                                     |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

### $SYST-06XMYM994-Data\ Sheet-MCP16501\ Low\ Cost\ PMIC\ for\ SAMA5DX/SAM9X6\ MPUs$

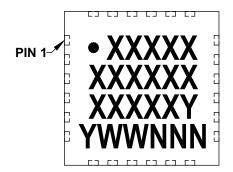

Affected Catalog Part Numbers (CPN)

MCP16501TA-E/RMB

MCP16501TB-E/RMB

MCP16501TC-E/RMB

MCP16501TD-E/RMB

MCP16501TE-E/RMB

Date: Thursday, August 06, 2020

# MCP16501

## Cost and Size Optimized PMIC for SAMA5DX/SAM9X6/ SAMA7G Series MPUs

- · Input Voltage: 2.7V to 5.5V

- Three 1A Output Current Buck Channels with 100% Maximum Duty Cycle Capability

- 2 MHz Buck Channels PWM Operation

- One Auxiliary 300 mA Low-Dropout Linear Regulator (LDO)

- ±1% Voltage Accuracy for DDR (Buck2 Output) and Core (Buck3 Output)

- Pin-Selectable Output Voltages for Buck2: 1.2V, 1.35V, 1.8V and for Buck3: 1.0V, 1.15V, 1.25V

- MPU-Specific Built-in Default Channel Sequencing and nRSTO Assertion Delay

- · Support of MPU Hibernate, Low-Power Modes

- Low Noise, Forced PWM (FPWM) and Low I<sub>Q</sub>, Light Load, High-Efficiency Mode Available

- Leakage-Free Interfacing to MPU in any Operating Condition through Optimized ESD Protection

- 250 µA Low-Power Mode Typical Quiescent Current Bucks and LDO On, No Load

- 6 µA Maximum Shutdown Current (V<sub>IN</sub> = 4.5V, T<sub>.I</sub> = +105°C)

- Separate LDO EN Input, Compatible to LV Logic

- · Cost and Size-Optimized BOM

- · Thermal Shutdown and Current Limit Protection

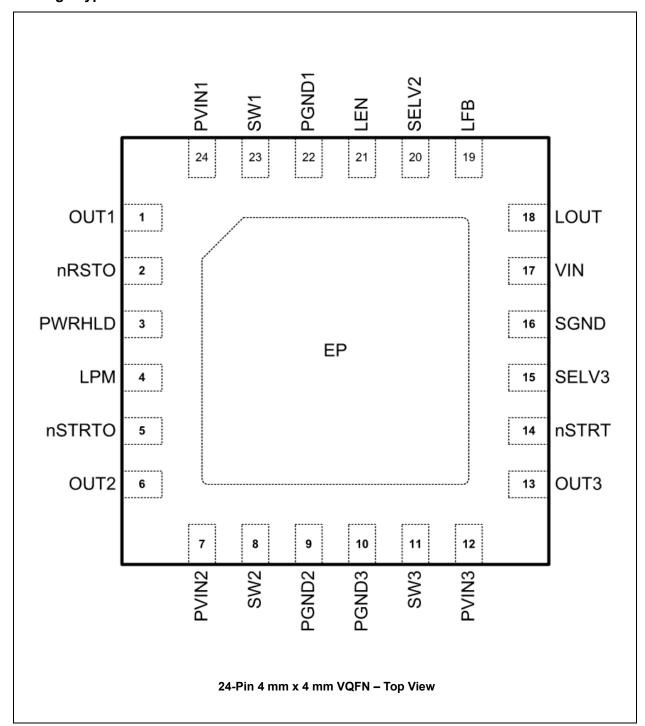

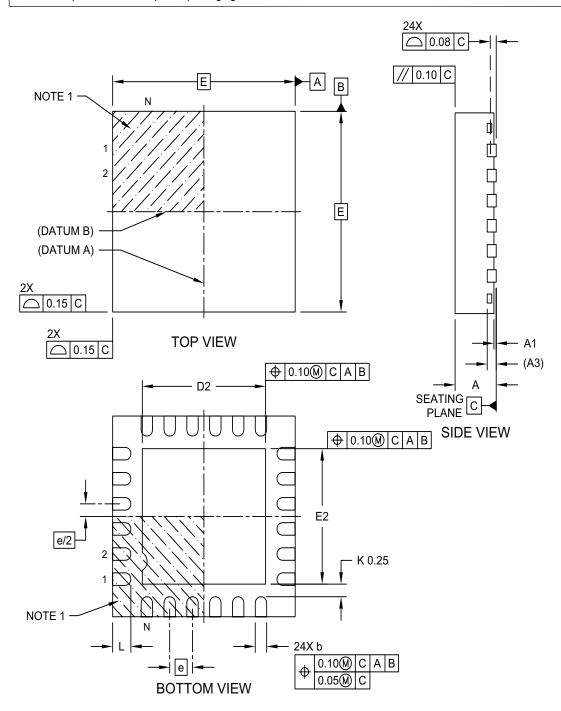

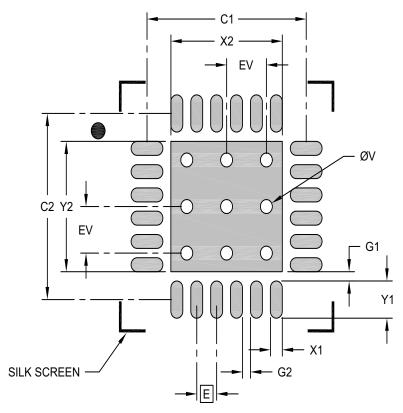

- 24-Pin 4 mm × 4 mm VQFN Package

- -40°C to +125°C Junction Temperature Range

#### **Applications**

- · High-Performance MPUs Power Supply Solutions

- μC/μP, FPGA and DSP Power

The MCP16501 is a cost and size optimized integrated PMIC, compatible with Microchip's EMPUs (Embedded Microprocessor Units) and associated DRAM Memories. It is compatible with SAMA5DX, SAM9X6 and SAMA7G MPUs, which are supported by dedicated device variants.

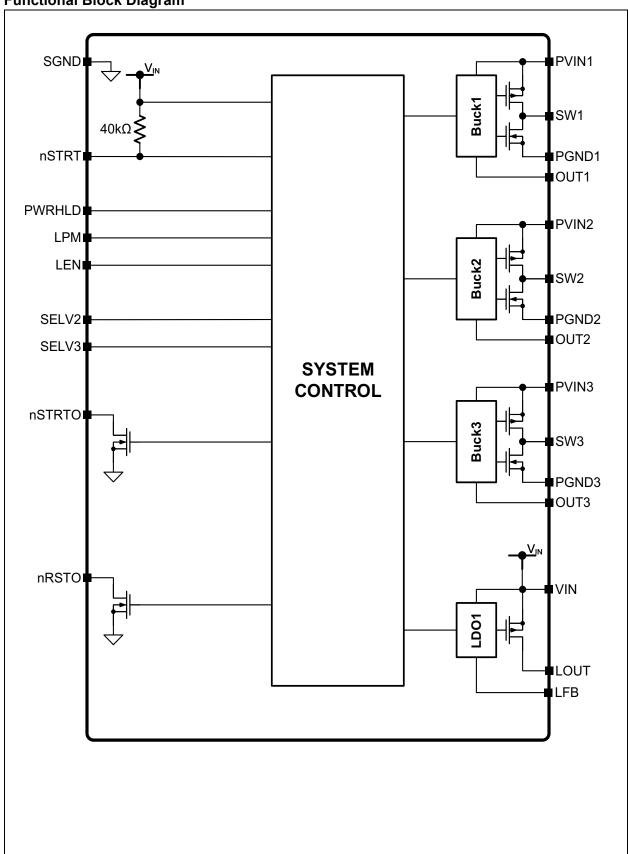

The MCP16501 integrates three DC-DC Buck regulators and one auxiliary LDO, and provides a comprehensive interface to the MPU.

All Buck channels can support loads up to 1A and are 100% duty cycle-capable.

The 300 mA LDO is provided such that sensitive analog loads can be supported.

The DDR memory voltage (Buck2 output) and MPU core voltage (Buck3 output) are selectable by means of two 3-state input pins. This method allows greater precision in the output voltage setting by eliminating inaccuracies due to external feedback resistors, while minimizing external component count. The voltage selection set allows easy migration across different generations of memory.

The default power channel sequencing is built-in according to the requirements of the MPU. A dedicated pin (LPM) facilitates the transition to Low-Power modes and the implementation of Backup mode with DDR in self-refresh (Hibernate mode).

The MCP16501 features a low no-load operational quiescent current and it draws less than 6  $\mu$ A ( $V_{IN}$  = 4.5V,  $T_{.I}$  = +105°C) in full shutdown.

Active discharge resistors are provided on each output. All Buck channels support safe start-up into pre-biased outputs.

The MCP16501 is available in a 24-pin 4 mm x 4 mm VQFN package with an operating junction temperature range from -40°C to +125°C.

### **Package Types**

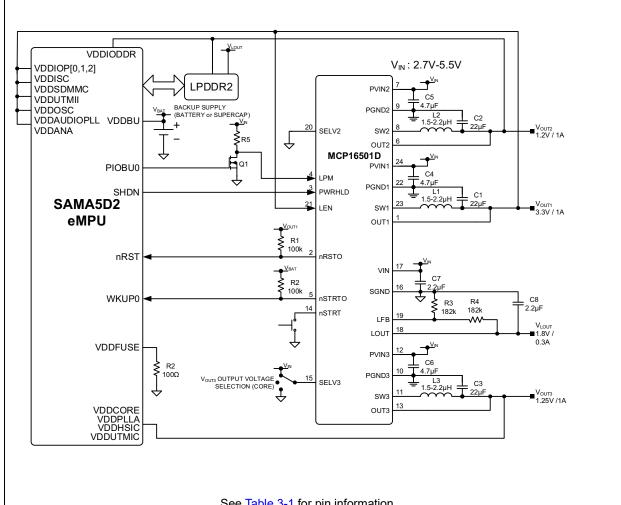

### **Typical Application Circuit**

See Table 3-1 for pin information.

Application Schematic of MCP16501D with SAMA5D2 and LPDDR2

### **Functional Block Diagram**

### 1.0 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings†

| VIN to SGND                              | 0.3V to +6V                       |

|------------------------------------------|-----------------------------------|

| Power Supply Voltage Pins PVINx to PGNDx | 0.3V to +6V                       |

| Power Supply Voltage Pins PVINx to VIN   | 0.3V to +0.3V                     |

| LOUT Pin to GND                          |                                   |

| LFB Sense Pins to SGND                   | 0.3V to V <sub>VIN</sub> + 0.3V   |

| OUTx Sense Pins to SGND                  | 0.3V to +6V                       |

| Output Switch Voltage SWx to PGNDx       | 0.3V to V <sub>PVINx</sub> + 0.3V |

| PGNDx to SGND                            | 0.3V to +0.3V                     |

| nSTRT, SELV2, SELV3 to SGND              | 0.3V to V <sub>VIN</sub> + 0.3V   |

| LPM, LEN, PWRHLD, nRSTO, nSTRTO to SGND  | 0.3V to +6V                       |

| Maximum Junction Temperature             | 150°C                             |

| Storage Temperature                      | 65°C to +150°C                    |

| ESD Protection on All Pins:              |                                   |

| HBM                                      | 2 kV                              |

| MM                                       | 100V                              |

| CDM                                      | 750V                              |

**Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

### **AC/DC CHARACTERISTICS**

**Electrical Specifications:** Unless otherwise specified:  $T_A = T_J = +25$ °C;  $V_{IN} = VIN = PVINx = 5V$ ; L1 = L2 = L3 = 2.2 μH;  $C_{OUT1}$ ,  $C_{OUT2}$ ,  $C_{OUT3} = 22$  μF. **Boldface** type applies for junction temperatures  $T_J$  of -40°C to +125°C.

| Parameters                                                          | Sym.                                 | Min. | Тур. | Max. | Units | Conditions                                                                                                                                                                  |

|---------------------------------------------------------------------|--------------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Input Supply                                                 |                                      |      |      |      |       |                                                                                                                                                                             |

| Supply Voltage Range                                                | V <sub>IN</sub>                      | 2.7  | _    | 5.5  | V     |                                                                                                                                                                             |

| Undervoltage Lockout<br>Threshold                                   | V <sub>UVLO_TH</sub>                 | 2.4  | 2.55 | 2.7  | V     | Turn-on                                                                                                                                                                     |

| Undervoltage Lockout<br>Hysteresis                                  | V <sub>UVLO_HYS</sub>                | _    | 125  | _    | mV    |                                                                                                                                                                             |

| Shutdown (Off) Current                                              | I <sub>SHDN</sub>                    | _    | 7    | 10   | μА    | PWRHLD = LPM = 0, nSTRT,<br>nRSTO, nSTRTO floating,<br>V <sub>IN</sub> = 5.5V                                                                                               |

|                                                                     | <sup>I</sup> SHDN_105 <sup>(1)</sup> | _    | 4.5  | 6    | μА    | PWRHLD = LPM = 0, nSTRT,<br>nRSTO, nSTRTO floating,<br>$V_{IN}$ = 4.5V,<br>$T_{J}$ = -40°C to +105°C                                                                        |

| Hibernate Mode<br>Non-Switching Quiescent<br>Current                | I <sub>QNS_HIB1</sub>                | _    | 110  | 150  | μА    | I <sub>OUT2</sub> = 0 mA, Buck2 on,<br>all other channels off,<br>V <sub>OUT2</sub> > V <sub>OUT2_NOM</sub> ,<br>LPM = 1, PWRHLD = 0                                        |

| Hibernate Mode Non-Switching<br>Quiescent Current<br>MCP16501D Only | I <sub>QNS_HIB2</sub>                | _    | 150  | 190  | μА    | I <sub>OUT2</sub> = 0 mA, Buck2 on, LDO on, all other channels off, V <sub>OUT2</sub> > V <sub>OUT2_NOM</sub> , V <sub>LFB</sub> > V <sub>LFB_NOM</sub> LPM = 1, PWRHLD = 0 |

**Note 1:** Maximum limit for  $T_J = -40^{\circ}C$  to  $+105^{\circ}C$  based on characterization data.

- 2: Not production tested.

- 3: Typical value from bench characterization, maximum value production tested.

## MCP16501

### AC/DC CHARACTERISTICS (CONTINUED)

Electrical Specifications: Unless otherwise specified: T<sub>A</sub> = T<sub>J</sub> = +25°C; V<sub>IN</sub> = VIN = PVINx = 5V; L1 = L2 = L3 = 2.2 µH; C<sub>OUT1</sub>, C<sub>OUT2</sub>, C<sub>OUT3</sub>= 22 μF. **Boldface** type applies for junction temperatures T<sub>.I</sub> of -40°C to +125°C. **Conditions Parameters** Units Sym. Min. Max. Typ. I<sub>OUT2</sub> = 0 mA, Buck2 on Hibernate Mode 110 μΑ IQOP\_HIB1 Operational Quiescent Current  $(V_{OUT2} = 1.2V),$ (Switching, One Buck Channel all other channels off, LPM = 1, On) (Note 2) **PWRHLD =** 0 Hibernate Mode 150  $I_{OUT2} = I_{LDO} = 0 \text{ mA},$ I<sub>QOP HIB2</sub> Operational Quiescent Current Buck2 and LDO on (Switching, One Buck Channel  $(V_{OUT2} = 1.2V, V_{LDO} = 1.8V),$ all other channels off, LPM = 1, On and the LDO Channel On) PWRHLD = 0 (Note 2)  $I_{OUTx} = 0$  mA, all channels on Low-Power Mode 205 μΑ I<sub>QOP\_LPM</sub> Operational Quiescent Current excluding LDO, default settings, PWRHLD = LPM = 1 (Switching) (Note 2)  $I_{OUTx} = 0$  mA, all channels on Low-Power Mode 250 I<sub>QOP LPM2</sub> Operational Quiescent Current including LDO, default settings, (Switching) (Note 2) PWRHLD = LPM = 1 Active Mode I<sub>OUTx</sub> = 0 mA, all channels 14 mΑ IQOP\_ACT Operational Quiescent Current enabled including LDO, default (Switching) (Note 2) settings, PWRHLD = 1, LPM = 0 SELV2 = LOW, SELV3 = HIGH Thermal Protection Overtemperature Shutdown 160 °C  $T_{TSD}$ Threshold (Note 2) Overtemperature Shutdown 20 °C T<sub>TSD HYS</sub> Hysteresis (Note 2) Buck1 ٧ Input Operating Voltage Range 2.7 5.5  $V_{PVIN1}$ **PVIN1 Shutdown Current** I<sub>PVIN1</sub> SHDN 0.05 2 μΑ Regulator disabled,  $V_{PVIN1} = 5V$ %  $I_{OUT1} = 0 \text{ mA}$ Output Voltage Accuracy, ACC OUTPWM1 -2 +2 **FPWM** Output Voltage Accuracy, ACC\_OUT<sub>PFM1</sub> -2 +2  $I_{OUT1} = 0$  mA, HCM off Auto-PFM %  $I_{OUT1} = 0 \text{ mA}, FPWM,$ Output Voltage Line Regulation LINE\_REGPWM1 0.03  $V_{IN} = PVIN1 = VIN = 3.6V \text{ to } 5.5V$ (Note 2) LINE REGPEM1 0.07  $I_{OUT1} = 0 \text{ mA}, \text{Auto-PFM},$  $V_{IN} = PVIN1 = VIN = 3.6V \text{ to } 5.5V$  $I_{OUT1} = 0A \text{ to } 1A, FPWM$ LOAD\_REG<sub>PWM1</sub> % Output Voltage Load 0.3 Regulation (Note 2) LOAD\_REG<sub>PFM1</sub>  $I_{OUT1}$  = 0A to 1A, Auto-PFM 0.5 %  $I_{OUT1} = 0 \text{ mA},$ Hysteretic Control Mode Upper HCM TH 1.7 2.9 4.3 % Regulation Threshold, PWRHLD = LPM = 1,  $VIN = PVIN1 = 1.06 \times V_{OUT1 NOM},$ Auto-PFM (MCP16501E only) OUT1 rising, % of V<sub>OUT1\_NOM</sub> Hysteretic Control Mode HCM\_DIS 11.1  $I_{OUT1} = 0 \text{ mA},$ Disable Threshold, PWRHLD = LPM = 1, Auto-PFM (MCP16501E only) VIN = PVIN1 rising, % of V<sub>OUT1\_NOM</sub>

**Note 1:** Maximum limit for  $T_J = -40^{\circ}$ C to  $+105^{\circ}$ C based on characterization data.

3: Typical value from bench characterization, maximum value production tested.

<sup>2:</sup> Not production tested.

### **AC/DC CHARACTERISTICS (CONTINUED)**

**Electrical Specifications:** Unless otherwise specified:  $T_A = T_J = +25$ °C;  $V_{IN} = VIN = PVINx = 5V$ ; L1 = L2 = L3 = 2.2 μH;  $C_{OUT1}$ ,  $C_{OUT2}$ ,  $C_{OUT3}$ = 22 μF. **Boldface** type applies for junction temperatures  $T_J$  of -40°C to +125°C.

| $C_{OUT1}$ , $C_{OUT2}$ , $C_{OUT3}$ = 22 $\mu$ F. <b>Boldface</b> type applies for junction temperatures $T_J$ of -40°C to +125°C. |                          |      |                          |      |       |                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|------|-------|------------------------------------------------------------------------------------------------------|

| Parameters                                                                                                                          | Sym.                     | Min. | Тур.                     | Max. | Units | Conditions                                                                                           |

| Hysteretic Control Mode<br>Enable Threshold,<br>Auto-PFM (MCP16501E only)                                                           | HCM_EN                   | 5    | 9                        | 13   | %     | I <sub>OUT1</sub> = 0 mA,<br>PWRHLD = LPM = 1,<br>VIN = PVIN1 falling,<br>% of V <sub>OUT1_NOM</sub> |

| Switching Frequency                                                                                                                 | f <sub>sw</sub>          | 1.8  | 2                        | 2.2  | MHz   | FPWM                                                                                                 |

| Maximum Duty Cycle                                                                                                                  | D <sub>MAX</sub>         | 100  | _                        | _    | %     | Functionality test                                                                                   |

| Minimum On Time                                                                                                                     | T <sub>ON_MIN1</sub>     | _    | 35                       | _    | ns    | FPWM                                                                                                 |

| High-Side Switch<br>On-Resistance                                                                                                   | R <sub>DSonP1</sub>      | _    | 140                      | 160  | mΩ    | PVIN1 = VIN = 3.6V                                                                                   |

| Low-Side Switch<br>On-Resistance                                                                                                    | R <sub>DSonN1</sub>      | _    | 120                      | 140  | mΩ    | PVIN1 = VIN = 3.6V                                                                                   |

| Start-up POK Bypass<br>Threshold                                                                                                    | V <sub>POKB_TH_B1</sub>  | 360  | 400                      | 440  | mV    | PVIN1 – OUT1, OUT1 rising,<br>PVIN1 = 3.0V, V <sub>OUT1_NOM</sub> = 3.3V                             |

| Start-up POK Bypass<br>Threshold Hysteresis                                                                                         | V <sub>POKB_HYS_B1</sub> | _    | 50                       | _    | mV    | OUT1 falling, PVIN1 = 3.0V                                                                           |

| Soft Start Rate                                                                                                                     | SSR                      | _    | 3.125                    | _    | V/ms  |                                                                                                      |

| High-Side Peak Current Limit (Cycle by Cycle)                                                                                       | I <sub>LIM_HS1</sub>     | 1.2  | 1.8                      | 2.4  | Α     |                                                                                                      |

| Current Limit Frequency<br>Foldback V <sub>OUT1</sub> Threshold                                                                     | V <sub>TH_FFB1</sub>     | _    | 500                      | _    | mV    |                                                                                                      |

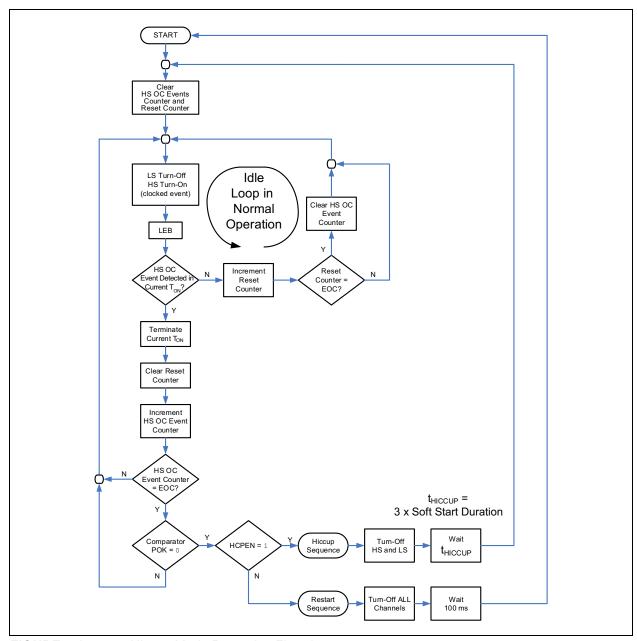

| Hiccup Mode Short-Circuit<br>Protection Wait Time                                                                                   | t <sub>HICCUP</sub>      | _    | 3x Soft<br>Start<br>Time | _    |       |                                                                                                      |

| Low-Side Negative Peak<br>Current Limit (FPWM)                                                                                      | I <sub>LIM_NEG1</sub>    | -1.4 | -1                       | -0.8 | А     |                                                                                                      |

| Zero Current Detection<br>Threshold                                                                                                 | I <sub>ZCD1</sub>        | 0    | 50                       | 110  | mA    |                                                                                                      |

| Active<br>Discharge Resistance                                                                                                      | R <sub>DISCH_OUT1</sub>  | _    | 25                       | _    | Ω     | DISCH enabled when regulator is disabled                                                             |

| Buck2, Buck3                                                                                                                        |                          |      |                          |      |       |                                                                                                      |

| Input Operating Voltage Range                                                                                                       | V <sub>PVINx</sub>       | 2.7  | _                        | 5.5  | V     |                                                                                                      |

| PVINx Shutdown Current                                                                                                              | I <sub>PVINx_SHDN</sub>  | _    | 0.05                     | 2    | μA    | Regulator disabled, PVINx = 5V                                                                       |

| Output Voltage Accuracy,                                                                                                            | ACC_OUT <sub>PWMx</sub>  | -1   | _                        | +1   | %     | $I_{OUTx} = 0 \text{ mA}, 0.9V \le V_{OUTx} \le 1.3V$                                                |

| FPWM                                                                                                                                |                          | -1.5 | _                        | +1.5 |       | $I_{OUTx}$ = 0 mA, $V_{OUTx}$ < 0.9V or $V_{OUTx}$ > 1.3V                                            |

| Output Voltage Accuracy,                                                                                                            | ACC_OUT <sub>PFMx</sub>  | -1   | _                        | +1   | %     | $I_{OUTx} = 0 \text{ mA}, 0.9V \le V_{OUTx} \le 1.3V$                                                |

| Auto-PFM                                                                                                                            |                          | -1.5 | _                        | +1.5 |       | $I_{OUTx}$ = 0 mA, $V_{OUTx}$ < 0.9V or $V_{OUTx}$ > 1.3V                                            |

| Output Voltage Line Regulation (Note 2)                                                                                             | LINE_REG <sub>PWMx</sub> | _    | 0.03                     | _    | %     | I <sub>OUT1</sub> = 0 mA, FPWM,<br>V <sub>IN</sub> = PVIN1 = VIN = 3.6V to 5.5V                      |

|                                                                                                                                     | LINE_REG <sub>PFMx</sub> | _    | 0.07                     | _    |       | $I_{OUT1}$ = 0 mA, Auto-PFM,<br>$V_{IN}$ = PVIN1 = VIN = 3.6V to 5.5V                                |

| Output Voltage Load                                                                                                                 | LOAD_REG <sub>PWMx</sub> | _    | 0.3                      | _    | %     | I <sub>OUTx</sub> = 0A to 1A, FPWM                                                                   |

| Regulation (Note 2)                                                                                                                 | LOAD_REG <sub>PFMx</sub> |      | 0.5                      | _    |       | I <sub>OUTx</sub> = 0A to 1A, Auto-PFM                                                               |

| Switching Frequency                                                                                                                 | f <sub>sw</sub>          | 1.8  | 2                        | 2.2  | MHz   | FPWM                                                                                                 |

**Note 1:** Maximum limit for  $T_J = -40^{\circ}C$  to  $+105^{\circ}C$  based on characterization data.

2: Not production tested.

3: Typical value from bench characterization, maximum value production tested.

# MCP16501

### AC/DC CHARACTERISTICS (CONTINUED)

Electrical Specifications: Unless otherwise specified: T<sub>A</sub> = T<sub>J</sub> = +25°C; V<sub>IN</sub> = VIN = PVINx = 5V; L1 = L2 = L3 = 2.2 µH;  $C_{OUT1}$ ,  $C_{OUT2}$ ,  $C_{OUT3}$ = 22  $\mu$ F. **Boldface** type applies for junction temperatures  $T_{.1}$  of -40°C to +125°C. **Parameters** Units Conditions Sym. Min. Typ. Max. Maximum Duty Cycle 100 % Functionality test  $D_{MAX}$ **FPWM** Minimum On Time 35  $T_{ON\_MINx}$ ns High-Side Switch 140 PVINx = VIN = 3.6V160  $m\Omega$ R<sub>DSonPx</sub> On-Resistance Low-Side Switch 140 PVINx = VIN = 3.6V120  $m\Omega$  $R_{DSonNx}$ On-Resistance Soft Start Rate SSR 3.125 V/ms High-Side Peak Current Limit 1.2 1.8 2.4 Α I<sub>LIM\_HSx</sub> (Cycle-by-Cycle) Current Limit Frequency 500 mV  $V_{TH FFBx}$ Foldback  $V_{OUTx}$  Threshold Hiccup Mode Short-Circuit 3x Soft **t**HICCUP **Protection Wait Time** Start Time Low-Side Negative Peak -1.4 -1 -0.8 Α I<sub>LIM\_NEGx</sub> Current Limit (FPWM) Zero Current Detection 0 33 110 mΑ  $I_{ZCDx}$ Threshold Active Discharge Resistance R<sub>DISCH\_OUTx</sub> DISCH enabled when regulator is disabled ٧ Input Operating Voltage Range 2.7  $V_{LVIN}$ 5.5 3.7 ٧ Output Voltage Range  $V_{LOUT}$ 0.9 Recommended application Stable Output Capacitor Range 2.2 20 I<sub>LOUT</sub> ≤ 150 mA – application C<sub>LOUT</sub> μF requirement (Note 2) 4.7 20 I<sub>LOUT</sub> ≤ 300 mA – application иF requirement I<sub>LOUT</sub>= 0 mA; only LDO on; Bucks Operational Quiescent 110 μΑ  $I_{VIN_Q}$ Current LDO Operation Quiescent 45 μΑ I<sub>I OUT</sub>= 0 mA; all channels on IVIN Q LDO Current including LDO, ΔVIN current when turning on LDO Feedback Voltage ACC LFB 0.8865 0.9 0.9135 V VIN = 3.6VDropout Voltage (Note 3) 170 500 mV  $I_{LOUT}$  = 300 mA  $V_{DO}$ Output Voltage Line LINE\_REG 0.024 % VIN = 3.6V to 5.5V,Regulation  $I_{LOUT} = 0.1 \text{ mA}$  $I_{LOUT}$  = 0.1 mA to 300 mA Output Voltage Load LOAD REG 0.3 % Regulation PSRR (Note 2) **PSRR** 63 dΒ  $f = 1 \text{ kHz}, I_{OUT} = 20 \text{ mA},$ V<sub>LOUT</sub> = 1.8V, VIN modulated f = 10 kHz, I<sub>OUT</sub> = 20 mA, 46 dB V<sub>LOUT</sub> = 1.8V, VIN modulated

3.125

V/ms

measured on LFB

SSR LFB Note 1: Maximum limit for  $T_1 = -40$ °C to +105°C based on characterization data.

Soft Start Rate

<sup>2:</sup> Not production tested.

Typical value from bench characterization, maximum value production tested.

### AC/DC CHARACTERISTICS (CONTINUED)

| <b>Electrical Specifications:</b> Unless otherwise specified: $T_A = T_J = +25^{\circ}\text{C}$ ; $V_{IN} = VIN = PVINx = 5V$ ; L1 = L2 = L3 = 2.2 $\mu$ H; $C_{OUT1,}$ $C_{OUT2,}$ , $C_{OUT3} = 22 \mu$ F. <b>Boldface</b> type applies for junction temperatures $T_J$ of -40°C to +125°C. |                         |                            |      |                            |       |                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|------|----------------------------|-------|---------------------------------------------------|

| Parameters                                                                                                                                                                                                                                                                                    | Sym.                    | Min.                       | Тур. | Max.                       | Units | Conditions                                        |

| Current Limit                                                                                                                                                                                                                                                                                 | I <sub>LIM_LOUT</sub>   | 310                        | 420  | 550                        | mA    | VIN = 4.5V,<br>V <sub>LOUT</sub> = 80% of nominal |

| Active Discharge Resistance                                                                                                                                                                                                                                                                   | R <sub>DISCH_LOUT</sub> | _                          | 25   |                            | Ω     | DISCH =enabled when regulator is disabled         |

| LEN Input                                                                                                                                                                                                                                                                                     |                         |                            |      | •                          |       |                                                   |

| LEN Logic High Input Voltage,<br>V <sub>IH</sub>                                                                                                                                                                                                                                              | $V_{IH\_LEN}$           | 1.15                       | _    | _                          | >     |                                                   |

| LEN Logic Low Input Voltage, V <sub>IL</sub>                                                                                                                                                                                                                                                  | $V_{IL\_LEN}$           | _                          | _    | 0.4                        | >     |                                                   |

| LEN Input leakage current                                                                                                                                                                                                                                                                     | I <sub>LK_LENT</sub>    | -1                         | _    | 1                          | μΑ    |                                                   |

| nSTRT Input                                                                                                                                                                                                                                                                                   |                         |                            |      |                            |       |                                                   |

| Logic High Input Voltage, V <sub>IH</sub>                                                                                                                                                                                                                                                     | V <sub>IH_nSTRT</sub>   | 0.66 V <sub>VIN</sub>      |      | _                          | V     | VIN = 3.6V-5.5V                                   |

| Logic Low Input Voltage, V <sub>IL</sub>                                                                                                                                                                                                                                                      | $V_{IL\_nSTRT}$         | _                          |      | 0.36 V <sub>VIN</sub>      | V     | VIN = 3.6V-5.5V                                   |

| Pull-up Resistance                                                                                                                                                                                                                                                                            | $R_{PU\_nSTRT}$         | _                          | 40   | _                          | kΩ    |                                                   |

| nSTRT Deglitch Time                                                                                                                                                                                                                                                                           | t <sub>DT_nSTRT</sub>   | _                          | 10   | _                          | μs    | Falling edge of nSTRT pin                         |

| SELV2, SELV3 Three-State Inp                                                                                                                                                                                                                                                                  | outs (x = 2, 3)         |                            |      |                            |       |                                                   |

| High State Threshold<br>Voltage, V <sub>IHT</sub>                                                                                                                                                                                                                                             | $V_{IHT\_SELVx}$        | V <sub>VIN</sub> –<br>0.9V | _    | V <sub>VIN</sub> –<br>0.4V | ٧     |                                                   |

| Low State Threshold<br>Voltage, V <sub>ILT</sub>                                                                                                                                                                                                                                              | $V_{ILT\_SELVx}$        | 0.5                        | _    | 1.0                        | V     |                                                   |

| Input Leakage Current High                                                                                                                                                                                                                                                                    | I <sub>lkgH_SELVx</sub> | _                          | 0.7  | 1                          | μΑ    | SELVx = VIN – 0.4V                                |

| Input Leakage Current Low                                                                                                                                                                                                                                                                     | I <sub>lkgL_SELVx</sub> | -1                         | 0.7  | _                          | μΑ    | SELVx = 0.4V                                      |

| PWRHLD, LPM Logic Inputs (>                                                                                                                                                                                                                                                                   | c= PWRHLD, LPM          | )                          |      |                            |       |                                                   |

| Logic High Input Voltage, V <sub>IH</sub>                                                                                                                                                                                                                                                     | $V_{IH_{L^X}}$          | 1.5                        | _    | _                          | V     | VIN = 3.6V-5.5V                                   |

| Logic Low Input Voltage, V <sub>IL</sub>                                                                                                                                                                                                                                                      | $V_{IL_{X}}$            | _                          | _    | 0.4                        | V     | VIN = 3.6V-5.5V                                   |

| Input Leakage Current                                                                                                                                                                                                                                                                         | I <sub>lkg_x</sub>      | -1                         | _    | 1                          | μΑ    |                                                   |

| Deglitch Time                                                                                                                                                                                                                                                                                 | t <sub>DT_x</sub>       | _                          | 10   | _                          | μs    |                                                   |

| nRSTO, nSTRTO Logic Output                                                                                                                                                                                                                                                                    |                         | TRTO)                      |      |                            |       |                                                   |

| Output Voltage Low, V <sub>OL</sub>                                                                                                                                                                                                                                                           | $V_{OL\_x}$             | _                          | _    | 0.4                        | V     | VIN = 3.6V-5.5V, I <sub>OL</sub> = 2 mA           |

| Leakage Current                                                                                                                                                                                                                                                                               | I <sub>lkg_x</sub>      | _                          | _    | 1                          | μΑ    | 5.5V applied, output driver off                   |

**Note 1:** Maximum limit for  $T_J = -40^{\circ}C$  to  $+105^{\circ}C$  based on characterization data.

2: Not production tested.

**3:** Typical value from bench characterization, maximum value production tested.

### TEMPERATURE SPECIFICATIONS(1)

| Parameters                           | Sym.           | Min. | Тур. | Max. | Units | Conditions   |

|--------------------------------------|----------------|------|------|------|-------|--------------|

| Temperature Ranges                   |                |      |      |      |       |              |

| Operating Junction Temperature Range | T <sub>J</sub> | -40  | _    | +125 | °C    | Steady state |

| Maximum Junction Temperature         | $T_{J\_MAX}$   | _    | _    | +150 | °C    | Transient    |

| Package Thermal Resistance           | $\theta_{JA}$  | _    | 38   | _    | °C/W  |              |

Note 1:  $T_A = +25^{\circ}C$ ;  $V_{IN} = PVINx = 5V$ ; unless otherwise specified. Bold values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$ .

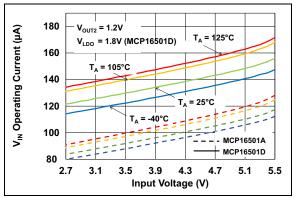

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

Note: Unless otherwise specified:  $V_{IN}$  = VIN= PVINx = 5V; L1 = L2 = L3 =  $2.2 \mu H$ ;  $C_{OUT1}$  =  $C_{OUT2}$  =  $C_{OUT3}$  =  $22 \mu F$ ,  $T_{A}$  =  $+25^{\circ}C$

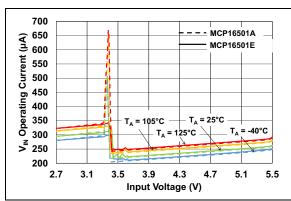

**FIGURE 2-1:**  $V_{IN}$  Operating Current vs. Input Voltage and Temperature – Hibernate Mode (LPM = High, PWRHLD = Low).

**FIGURE 2-2:**  $V_{IN}$  Quiescent Current vs. Input Voltage and Temperature – Low-Power Mode (LPM = PWRHLD = High).

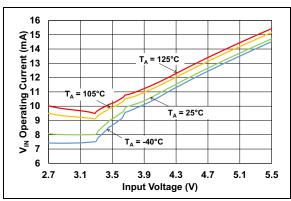

**FIGURE 2-3:**  $V_{IN}$  Quiescent Current vs. Input Voltage and Temperature – Active Mode (LPM = Low, PWRHLD = High).

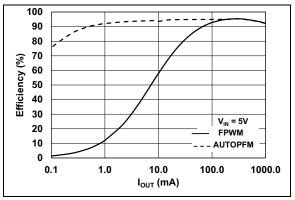

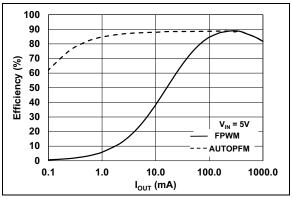

FIGURE 2-4: Buck1 Efficiency vs. Load Current Measured on PVIN1 ( $V_{OUT1} = 3.3V$ ).

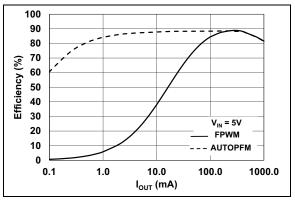

**FIGURE 2-5:** Buck2 Efficiency vs. Load Current Measured on PVIN2 ( $V_{OUT2} = 1.2V$ ).

**FIGURE 2-6:** Buck3 Efficiency vs. Load Current Measured on PVIN3 ( $V_{OUT3} = 1.25V$ ).

Note: Unless otherwise specified:  $V_{IN}$  = VIN= PVINx = 5V; L1 = L2 = L3 = 2.2  $\mu$ H;  $C_{OUT1}$  =  $C_{OUT2}$  =  $C_{OUT3}$  = 22  $\mu$ F,  $T_{A}$  = +25°C

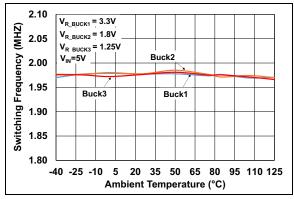

FIGURE 2-7: Switching Frequency vs.

Temperature – Active Mode (LPM = Low,

PWRHLD = High).

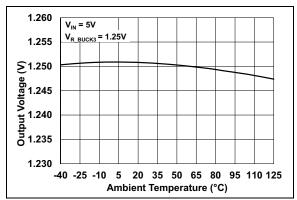

**FIGURE 2-8:** Buck3 Output Voltage vs. Temperature –  $V_{OUT3}$  = 1.25V, Active Mode (LPM = Low, PWRHLD = High).

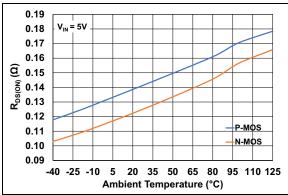

**FIGURE 2-9:** MOSFET  $R_{DS(ON)}$  vs. Temperature.

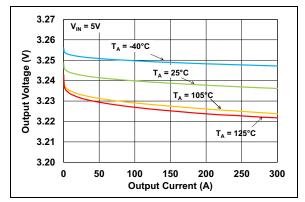

**FIGURE 2-10:** LDO Output Voltage vs. Output Current and Temperature (Load Regulation –  $V_{LOUT}$  = 3.3V).

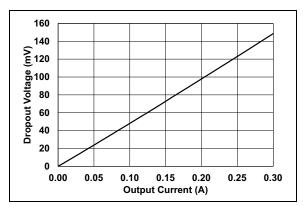

**FIGURE 2-11:** LDO Dropout Voltage vs. Load Current.

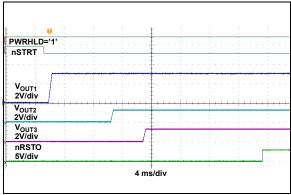

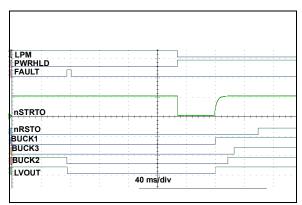

FIGURE 2-12: nSTRT Start-up Sequence.

Note: Unless otherwise specified:  $V_{IN}$  = VIN= PVINx = 5V; L1 = L2 = L3 = 2.2  $\mu$ H;  $C_{OUT1}$  =  $C_{OUT2}$  =  $C_{OUT3}$  = 22  $\mu$ F,  $T_{A}$  = +25°C

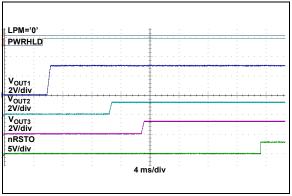

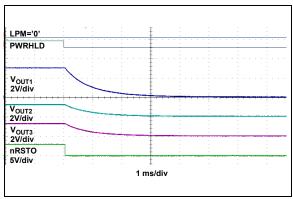

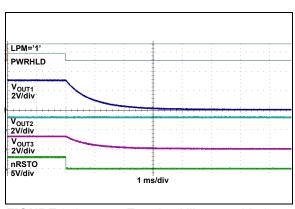

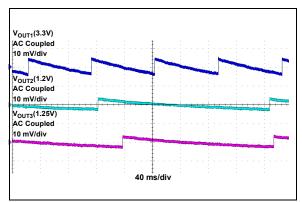

FIGURE 2-13: PWRHLD Start-up Sequence.

FIGURE 2-14: PWRHLD Shutdown Sequence.

FIGURE 2-15: Entering Hibernate Mode.

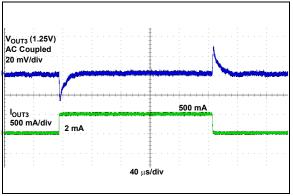

**FIGURE 2-16:** Buck3 Transient Response (Active Mode,  $V_{OUT3} = 1.25V$ ).

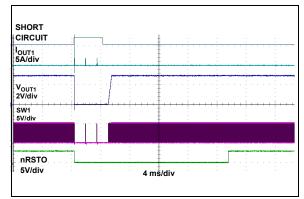

**FIGURE 2-17:** Output Short Circuit on V<sub>OUT1</sub>.

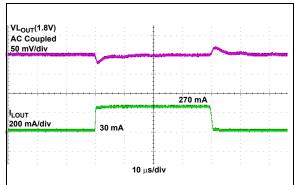

FIGURE 2-18: LDO Load Transient Response.

Note: Unless otherwise specified:  $V_{IN}$  = VIN= PVINx = 5V; L1 = L2 = L3 = 2.2  $\mu$ H;  $C_{OUT1}$  =  $C_{OUT2}$  =  $C_{OUT3}$  = 22  $\mu$ F,  $T_{A}$  = +25°C

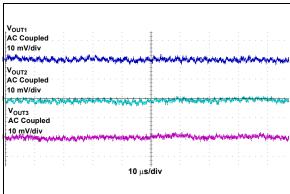

FIGURE 2-19: Buck Channels Output Voltage Ripple, Active (FPWM) Mode.

**FIGURE 2-20:** Buck Channels Output Voltage Ripple, Low-Power (Auto-PFM) Mode.

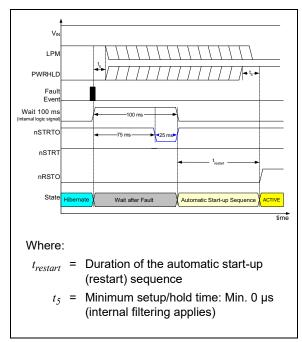

**FIGURE 2-21:** MCP16501D Automatic Wake-up Pulse upon Fault on Active Channels, Hibernate Mode.

### 3.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| Pin Number | Pin Name | Description                                                                                                                                                                                                           |  |  |  |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1          | OUT1     | Output Sensing for Buck Channel 1. Connect to the regulation point for V <sub>OUT1</sub> .                                                                                                                            |  |  |  |

| 2          | nRSTO    | Active-Low, Open-Drain Reset Output.                                                                                                                                                                                  |  |  |  |

| 3          | PWRHLD   | Power Hold Input. Typically asserted as high by the MPU to maintain power after the initial start-up is triggered by nSTRT. PWRHLD is to be asserted as low by the MPU to initiate a PMIC shutdown sequence.          |  |  |  |

| 4          | LPM      | Low-Power Mode Input Pin. In combination with PWRHLD, this pin defines the power mode status of the MCP16501.                                                                                                         |  |  |  |

| 5          | nSTRTO   | Active-Low, Open-Drain Start Event Output. nSTRTO is asserted low whenever nSTRT is low.                                                                                                                              |  |  |  |

| 6          | OUT2     | Output Sensing for Buck Channel 2. Connect to the regulation point for V <sub>OUT2</sub> .                                                                                                                            |  |  |  |

| 7          | PVIN2    | Power Input Voltage of Buck Channel 2. Connect a ceramic capacitor from PVIN2 to the PGND2 pin to localize pulsed current loops and decouple switching noise.                                                         |  |  |  |

| 8          | SW2      | Switch Node of Buck Channel 2. Internal power MOSFET switches and external inductor connection.                                                                                                                       |  |  |  |

| 9          | PGND2    | Power Ground of Buck Channel 2.                                                                                                                                                                                       |  |  |  |

| 10         | PGND3    | Power Ground of Buck Channel 3.                                                                                                                                                                                       |  |  |  |

| 11         | SW3      | Switch Node of Buck Channel 3. Internal power MOSFET switches and external inductor connection.                                                                                                                       |  |  |  |

| 12         | PVIN3    | Power Input Voltage of Buck Channel 3. Connect a ceramic capacitor from PVIN3 to the PGND3 pin to localize pulsed current loops and decouple switching noise.                                                         |  |  |  |

| 13         | OUT3     | Output Sensing for Buck Channel 3. Connect to the regulation point for V <sub>OUT3</sub> .                                                                                                                            |  |  |  |

| 14         | nSTRT    | Start Event Input. Drive nSTRT to low to initiate a start-up sequence. nSTRT is pulled up internally. A capacitor can be connected to nSTRT to automatically initiate a power-up sequence when the main supply rises. |  |  |  |

| 15         | SELV3    | Buck Channel 3 Output Voltage Selection Pin. Three-state input.                                                                                                                                                       |  |  |  |

| 16         | SGND     | Signal Ground. Connect to reference ground plane.                                                                                                                                                                     |  |  |  |

| 17         | VIN      | Input voltage for the LDO and for the analog control circuitry. Decouple VIN to SGND with a 2.2uF (minimum) ceramic capacitor.                                                                                        |  |  |  |

| 18         | LOUT     | LDO Output. Decouple LOUT to ground with a 2.2 µF (minimum) ceramic capacitor.                                                                                                                                        |  |  |  |

| 19         | LFB      | LDO FB pin. Connect to an external resistor divider to LOUT for output voltage adjustment.                                                                                                                            |  |  |  |

| 20         | SELV2    | Buck Channel 2 Output Voltage Selection Pin. Three-state input.                                                                                                                                                       |  |  |  |

| 21         | LEN      | LDO Enable input.                                                                                                                                                                                                     |  |  |  |

| 22         | PGND1    | Power Ground of Buck Channel 1.                                                                                                                                                                                       |  |  |  |

| 23         | SW1      | Switch Node of Buck Channel 1. Internal power MOSFET switches and external inductor connection.                                                                                                                       |  |  |  |

| 24         | PVIN1    | Power Input Voltage of Buck Channel 1. Connect a ceramic capacitor from PVIN1 to the PGND1 pin, to localize pulsed current loops and decouple switching noise.                                                        |  |  |  |

| -          | EP       | Exposed Pad. Connect to ground plane with vias to ensure good thermal properties.                                                                                                                                     |  |  |  |

### 4.0 DEVICE OPTIONS

The MCP16501 is offered in different options, depending on the target I/O voltage needed external memory type and behavior in bypass situations. The options currently available, also shown in Table 4-1, are the following:

Note:

All device variants are generated at the factory with One-Time-Programmable memory, which configures default settings at power-up. Please contact your nearest Microchip Sales Office for further assistance on the development of customized device variants.

TABLE 4-1: DEFAULT CONFIGURATIONS

| Device Options                | MCP16501A     | MCP16501B     | MCP16501C     | MCP16501D     | MCP16501E     |

|-------------------------------|---------------|---------------|---------------|---------------|---------------|

| V <sub>OUT1</sub>             | 3.3V          | 2.8V          | 3V            | 3.3V          | 3.3V          |

| LPDDR2/3                      | Not supported | Not supported | Not supported | Supported     | Not supported |

| Hysteretic Control Mode (HCM) | Not supported | Not supported | Not supported | Not supported | Supported     |

# 4.1 Buck Channels and Related External Components

The MCP16501 Buck channels are based on Peak Current mode control architecture and have internal frequency compensation for the voltage regulation loop. The slope compensation is optimized for inductors in the 1.5  $\mu$ H to 2.2  $\mu$ H range. A minimum output capacitor of 22  $\mu$ F is required for stability. Output capacitance can be increased if necessary; however, the maximum output capacitance value should be limited to avoid engaging the Hiccup mode overcurrent protection during the initial soft start ramp. Further details are given in Section 5.5 "Maximum Simultaneous Capacitive and DC Loading in Soft Start".

The recommended input decoupling capacitance on each Buck channel is 4.7  $\mu F$ .

The Buck channels can operate in either Forced PWM mode (Continuous Inductor Current mode), where the inductor current is allowed to go negative, or in Automatic PFM mode, where the inductor current is prevented from going negative through Zero-Current Detection (ZCD) and diode emulation of the low-side MOSFET.

The switching frequency in Forced PWM Mode is nominally 2 MHz.

# 4.2 LDO Channel and Related External Components

The MCP16501 LDO is designed for operation with low-ESR ceramic output capacitors of 2.2  $\mu$ F (minimum value) for loads up to 150 mA, and of 4.7  $\mu$ F (minimum value) for loads up to 300 mA. The total output capacitance should not exceed 20  $\mu$ F. Recommended capacitor part numbers are given in Section 5.1 "Recommended External Components".

### 4.3 Control Signals and Power States

#### 4.3.1 INTERFACING SIGNALS

The MCP16501 is interfaced to the host MPU by means of the following signals: nSTRTO (open-drain output), nRSTO (open-drain output), PWRHLD (input) and LPM (input). The ESD protection on each interfacing signal is purposely designed to prevent any leakage from the MPU I/Os, even in the case where the main input power is removed from the MCP16501.

# 4.3.2 nSTRT, nSTRTO, PWRHLD FUNCTIONALITY

The nSTRT (push button input) serves as an external wake-up input to the PMIC+MPU system. nSTRT is internally pulled up to VIN and monitored. When the nSTRT is pulled/detected as low (e.g., by means of a push button or any other pull-down device) for longer than a minimum debouncing time, the MCP16501 initiates the turn-on sequence.

The nSTRTO signal is asserted low whenever the nSTRT is detected to be low; otherwise, it is High-Z (typically, nSTRTO has an external pull-up resistor). The only exception to this input (nSTRT)/output (nSTRTO) relationship is the so called Automatic Wake-up Pulse (AWKP) that is described in Section 4.4.6 "Restart Sequence After Fault and Automatic Wake-up Pulse (AWKP) Generation-MCP16501D only" (applicable to MCP16501D only).

After the start-up sequence has been initiated, the MCP16501 expects the assertion of the PWRHLD signal (Power-Hold) from the MPU to validate the start-up. PWRHLD could already be high in a typical application using a backup supply. If PWRHLD has not been asserted high by the MPU before the completion of the start-up sequence (i.e., when nRSTO is about to be asserted high), the MCP16501 will automatically initiate a turn-off sequence.

During run time (PWRHLD = high), the nSTRT (thus nSTRTO) can again be asserted low. No automatic action is taken by the MCP16501 in this case.

# 4.3.3 nSTRT/PWRHLD TYPICAL USE CASES

Depending on the presence of a backup supply and the availability of an external wake-up signal connected at nSTRT ("Button"), four different scenarios can be defined for the turn-on of the MCP16501, as described in Figure 4-1.

#### **Applications With a Backup Supply Applications Without a Backup Supply** PVINx, VIN PVINx, VIN VDDCORE VDDCORE nSTRT VDDIODDR nSTRT VDDIODDR С MCP16501 MCP16501 Applications Without Start-up Push Button MPU MPU PWRHLD SHDN I PM I PM nSTRTO nSTRTC WKUF The application starts when $V_{IN}$ ramps up because of the capacitor C, which delays the rise of nSTRT with respect to $V_{IN}$ and causes nSTRT The application starts when V<sub>IN</sub> ramps up because of the capacitor C, which delays the rise of nSTRT with respect to $V_{\mbox{\scriptsize IN}}$ and causes nSTRT to appear low to appear low as soon as the MCP16501 is powered. as soon as the MCP16501 is powered. Note that PWRHLD (= SHDN from MPU) was set to '1' at the time the PWRHLD (= SHDN from MPU) is set to '1' as soon as VBAT (= VDDIO) is above battery was mounted on the PCB (i.e., at the time of manufacturing). its internal POR threshold (around 1.5V). The power channels of MCP16501 are turned off by the MPU by setting The power channels of MCP16501 are turned off by the MPU by setting SHDN = 0. The MPU is then in Backup mode. SHDN = 0. In this case, the MPU is not in Backup mode; it is simply completely off. LPM cannot be used, nor can SHDN be set to '1' because the supply voltage If supported, the DDR can also be placed in Backup Self-Refresh of the SHDWC controller is missing. From the OFF state, the application can (BSR) mode by setting LPM = 1 before SHDN = 0. only be restarted by cycling power on V<sub>IN</sub>. To wake up the application from Backup mode, a wake-up event must be generated for the SHDWC (Shutdown and Wake-up Controller) of the MPU. This can be an internal event (e.g., RTC, RTT alarm, TAMPER detection) or an event on an I/O of the SHDWC (e.g., wake-up from a wireless module). The MPU will then set SHDN = 1 and the low-to-high transition of PWRHLD will cause the MCP16501 to restart. If $V_{\rm IN}$ is cycled while the MPU is in Backup mode (SHDN = 0), the MCP16501 restarts automatically and sends a wake-up event to the MPU on nSTRTO (WKUP). If this wake-up event was not enabled in the MPU SHDWC configuration, SHDN will stay low and the MCP16501 will turn off at the end of the start-up sequence, because PWRHLD has not been set high. If this wake-up event is enabled, SHDN will immediately go high, thus confirming the start-up sequence for the MCP16501 and the application will restart. PVINx, VIN VDDIC PVINx, VIN VDDCORE VDDCORE nSTRT VDDIODDE nSTRT VDDIODDF Applications With Start-up Push Button MCP16501 MCP16501 MPU MPU PWRHLD LPM LPM I PM I PM nSTRTC nSTRTO The application does not immediately start when V<sub>IN</sub> ramps up. The application does not immediately start when V<sub>IN</sub> ramps up. The button must be pressed to start the MCP16501. The button must be pressed (nSTRT = Low) to start the MCP16501. PWRHLD (= SHDN from MPU) is set to '1' as soon as VBAT (= VDDIO) is above Note that PWRHLD (= SHDN from MPU) was set to '1' at the time the at nSTRT its internal POR threshold (around 1.5V). battery was mounted on the PCB (i.e., at the time of manufacturing). The power channels of MCP16501 are turned off by the MPU by setting The power channels of MCP16501 are turned off by the MPU by setting SHDN = 0. In this case, the MPU is not in Backup mode; it is simply completely SHDN = 0. The MPU is then in Backup mode. off. LPM cannot be used, nor can SHDN be set to '1' because the supply voltage If supported, the DDR can also be placed in backup self-refresh mode of the SHDWC controller is missing (BSR) by setting LPM = 1 before SHDN = 0. To restart the application, the push button must be pressed. To wake up the application from Backup mode, a wake-up event must be generated for the SHDWC (Shutdown and Wake-up Controller) of the MPU. This can be an internal event (e.g., RTC, RTT alarm, TAMPER detection) or an event on an I/O of the SHDWC (e.g., wake-up from a wireless module). The MPU will then set SHDN = 1 and the low-to-high transition of PWRHLD will cause the MCP16501 to restart. If $\rm V_{IN}$ is cycled while the MPU is in Backup mode (SHDN = 0), the MCP16501 does not restart automatically. To restart the application, the button must be pressed and nSTRTO (WKUP) be an enabled wake-up event. The DDR supply loss, due to an input power loss while in BSR mode, will be managed by software (i.e., by reloading the contents of the DDR).

FIGURE 4-1: Illustration of Start-up Mechanisms for Various MPU Configurations.

# 4.3.4 PWRHLD, LPM, LEN AND POWER STATES DEFINITIONS

PWRHLD and LPM define different power states which are illustrated in Table 4-2. These are default definitions for the MCP16501A. Other default definitions are possible for different or customized product variants.

The LDO operation is completely independent of the power states and is controlled by the LEN pin. The only exception to this is in the case of MCP16501D, used in LPDDR2 applications where the LDO is used to power the memory alongside Buck2. For more details on this see Section 5.3, LPDDR2 Support with Hibernate Mode-MCP16501D Only.

| TABLE 4-2: DEFAULT POWER STATES DEFINITION (MCP16501A |

|-------------------------------------------------------|

|-------------------------------------------------------|

| PWRHLD | LPM | Buck1          | Buck2          | Buck3          | LDO            | nRSTO  | Power State    |

|--------|-----|----------------|----------------|----------------|----------------|--------|----------------|

| 0      | 0   | Off            | Off            | Off            | LEN Controlled | Low    | Off            |

| 0      | 1   | Off            | On<br>Auto-PFM | Off            | LEN Controlled | Low    | Hibernate mode |

| 1      | 1   | On<br>Auto-PFM | On<br>Auto-PFM | On<br>Auto-PFM | LEN Controlled | High-Z | Low-Power mode |

| 1      | 0   | On<br>FPWM     | On<br>FPWM     | On<br>FPWM     | LEN Controlled | High-Z | Active mode    |

Other logic combinations of PWRHLD and LPM are forbidden. The initial state is the OFF state (shutdown).

The process by which the MCP16501 abandons the OFF state and enters the other possible power states is defined as the power-up sequence, which is described

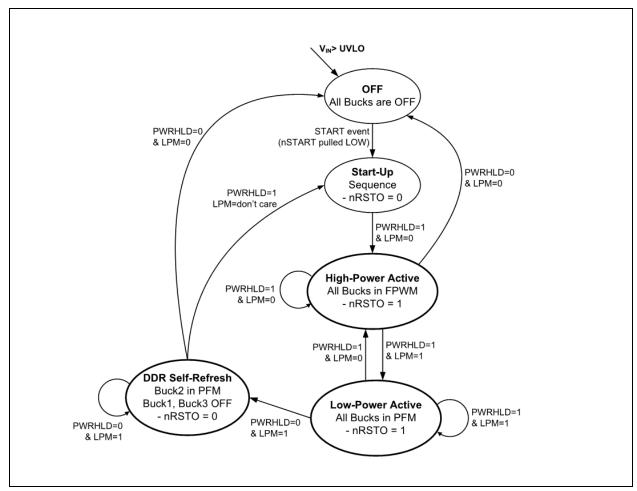

in Section 4.4.1 "Typical Power-up Sequence and Timing". The following state diagram in Figure 4-2 illustrates the power states of MCP16501 and their typical and/or permissible dynamic transitions.

FIGURE 4-2: Finite State Machine (FSM) States Diagram for MCP16501.

#### 4.3.5 SELV2 AND SELV3 PINS

Pins SELV2 and SELV3 are meant to program the default settings of some rails that must be activated during the power-up sequence, but whose voltage values are application-dependent. These are Buck2 and Buck3, the first being dedicated to DDRx/LPDDRx power, while the latter being dedicated to core power.

The default values are selectable among three options, corresponding to three different states of the relevant pin: connected to ground (Low), connected to input supply (High) or left unconnected (High-Z).

The Buck2 default voltage can be selected by means of the SELV2 pin as follows:

TABLE 4-3: V<sub>OUT2</sub> DEFAULT VOLTAGE VS. SELV2 PIN

| SELV2 Status | V <sub>OUT2</sub> Voltage | DDR Type          |

|--------------|---------------------------|-------------------|

| Low          | 1.2V                      | LPDDR2,<br>LPDDR3 |

| High-Z       | 1.35V                     | DDR3L             |

| High         | 1.8V                      | DDR2              |

The Buck3 default voltage can be selected by means of the SELV3 pin as follows:

TABLE 4-4: V<sub>OUT3</sub> DEFAULT VOLTAGE VS. SELV3 PIN

| SELV3 Status | V <sub>OUT3</sub> Voltage | eMPU Type            |

|--------------|---------------------------|----------------------|

| Low          | 1V                        | SAM9-5               |

| High-Z       | 1.15V                     | SAM9-6 and<br>SAMA7G |

| High         | 1.25V                     | SAMA5D2x             |

Note: SELV2 and SELV3 are always hardwired in the final application and they cannot be changed on-the-fly during operation.

The statuses of SELV2 and SELV3 are frozen in a snapshot as soon as the VIN voltage exceeds the turn-on Undervoltage Lockout Threshold (UVLO), as specified in the "Electrical Characteristics" table. Any changes of the SELV2 and SELV3 pins will have no effect after the snapshot, and VIN must fall under the turn-off (lower) UVLO threshold to unfreeze the snapshot.

Both pins are intended to be connected to GND (0V), to VIN or left floating in the application. When left floating, internal circuitry is initially activated to bias SELV2 and SELV3 at start-up for proper three-state (floating state) detection.

For "Electrical Characteristics" table specification purposes, the High State Threshold Voltage ( $V_{ILT}$ ) and Low State Threshold Voltage ( $V_{ILT}$ ) of pins SELV2 and SELV3 are given. They have both a minimum and a maximum value specification.

At the time the snapshot is taken, those Min. and Max. values should be used and interpreted as follows:

- If V<sub>IHT</sub>(MAX) < V(SELVx) ≤ V(VIN) → SELVx is considered HIGH

- If 0V ≤ V(SELVx) < V<sub>ILT</sub>(MIN) → SELVx is considered LOW

- If V<sub>ILT</sub>(MAX) < V(SELVx) < V<sub>IHT</sub>(MIN) → SELVx is considered floating

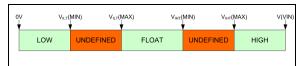

If  $V_{IHT}(MIN) \leq V(SELVx) \leq V_{IHT}(MAX)$  or  $V_{ILT}(MIN) \leq V(SELVx) \leq V_{ILT}(MAX)$ , then the logic status of SELVx may not be interpreted correctly. Therefore, if the end user chooses a connection different than the recommended connection to GND, VIN or no connection, then any usage of the SELVx pins within those boundaries should be avoided. This is also illustrated in Figure 4-3 shown below:

FIGURE 4-3: SELVx High, Low and Float States Threshold.

#### 4.3.6 nRSTO (RESET OUTPUT) PIN

Pin nRSTO is an active-low, open-drain output pin that keeps the MPU in a Reset state. The nRSTO pin is released (i.e., goes High-Z) with a 16ms delay upon successful completion of a start-up sequence. nRSTO is immediately asserted low when either the VIN voltage falls below the UVLO threshold, or a Fault condition is detected at system level (such as a Thermal Shutdown) or an overcurrent condition is detected on the Buck channels. Please see **Section 5.4 "Protections"** for more details on the Faults that would cause the nRSTO signal low assertion. nRSTO also goes low when the Hibernate mode is entered.

# 4.4 Power-up/Power-Down/Hibernate Sequences and Timings

# 4.4.1 TYPICAL POWER-UP SEQUENCE AND TIMING

The typical scenario applies to MPU applications, where:

I/O voltage (VDDIO) and, if applicable, auxiliary

## MCP16501

LDO rail is started first (at time t<sub>1</sub>), by connecting LEN to the VDDIO output (MCP16501D only).

- DDR supply/DDRIO voltage (VDDIODDR) is started next after delay t<sub>2</sub>. From the MPU perspective, t<sub>2</sub> is not mandatory, but it facilitates the use of an external 1.8V DC-DC or LDO for LPDDR2/3 (VDDIODDR being the 1.2V supply of the LPDDR2/3). This DC-DC can be initially sequenced to VDDIO at start-up and maintained on by VDDIODDR for Hibernate mode (backup self-refresh).

- VDDCORE (and VDDCPU for other MPUs) voltages are started last, after a delay of t<sub>3</sub>.

- Upon successful start-up of all the rails in the power-up sequence, after delay t<sub>4</sub>, the Reset signal (nRSTO) is deasserted and software execution can start

The start-up sequence can be initiated in two different ways, also depending on the presence of a back-up supply in the application:

- nSTRT event (nSTRT pin pulled low), maintained by PWRHLD assertion. In applications with a backup battery, the PWRHLD signal is typically already high before the nSTRT event

- A low-to-high transition of the PWRHLD signal, regardless of the nSTRT event. This is only possible in applications with backup supply. This mode is typically originated by an external wake-up event asserted by a peripheral device to the MPU Shutdown and Wake-up Controller (SHDWC), which is still powered in Backup mode.

Note: The nSTRT event needs the assertion of PWRHLD to have the power-up sequence completed successfully. If PWRHLD is not yet high at the time nRSTO is to be asserted, the MCP16501 automatically initiates a turn-off sequence without any positive glitches on nRSTO.

Delay  $t_1$  acts as a debouncing delay of the nSTRT event. Therefore, nSTRT must be detected as low continuously during  $t_1$  to validate the start-up event and initiate the first sequence step. After the first sequence step is started (at  $t_1$ ), nSTRT can be released to its high level at any time. Also, subsequent high-low-high toggling of nSTRT during the execution of the start-up sequence, while visible at the nSTRTO output, will be ignored by the sequencer and it will NOT reset the start-up sequence under execution.

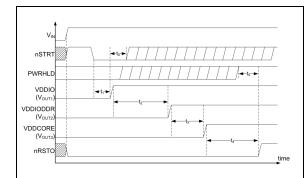

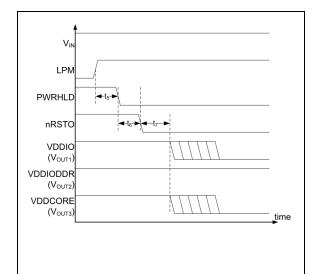

The following timing diagram in Figure 4-4 shows the typical sequence for Case 1:

#### Where:

- $t_I$  = Delay from nSTRT falling to first output  $V_{OUT1}$  starting (default 0.5 ms + device wake-up time, about 100 µs)

- t<sub>2</sub> = Time from V<sub>OUT1</sub> established to V<sub>OUT2</sub> starting (default 8 ms)

- t<sub>3</sub> = Time from V<sub>OUT2</sub> established to V<sub>OUT3</sub> starting (default 4 ms)

- t<sub>4</sub> = Time from V<sub>OUT3</sub> established to nRSTO deassertion (default 16 ms)

- f = Setup/hold times, min. 0 μs (internal filtering applies)

**FIGURE 4-4:** Start-Up from nSTRT Timing Diagram.

For the different OTP options for the  $t_1$  to  $t_4$  timings see the respective values in "Configuration Options".

For power supplies starting at t<sub>1</sub>, additional delay time interval is added to the device wake-up time.

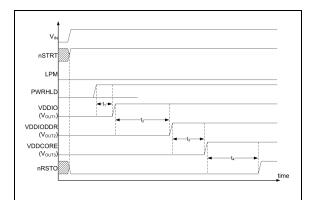

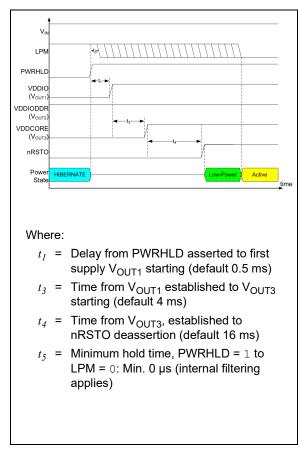

The following timing diagram in Figure 4-5 shows the typical sequence for Case 2:

#### Where:

- $t_I$  = Delay from PWRHLD asserted to first output V<sub>OUT1</sub> starting (default 0.5 ms + device wake-up time, about 100 µs)

- $t_2$  = Time from V<sub>OUT1</sub> established to V<sub>OUT2</sub> starting (default 8 ms)

- t<sub>3</sub> = Time from V<sub>OUT2</sub> established to V<sub>OUT3</sub> starting (default 4 ms)

- $t_4$  = Time from V<sub>OUT3</sub> established to nRSTO deassertion (default 16 ms)

# FIGURE 4-5: Start-Up from PWRHLD Timing Diagram.

For all sequences described above, LPM can be assumed to be low. The MPU will assert LPM after some time, based on software decision, to enter the Low-Power mode.

# MCP16501

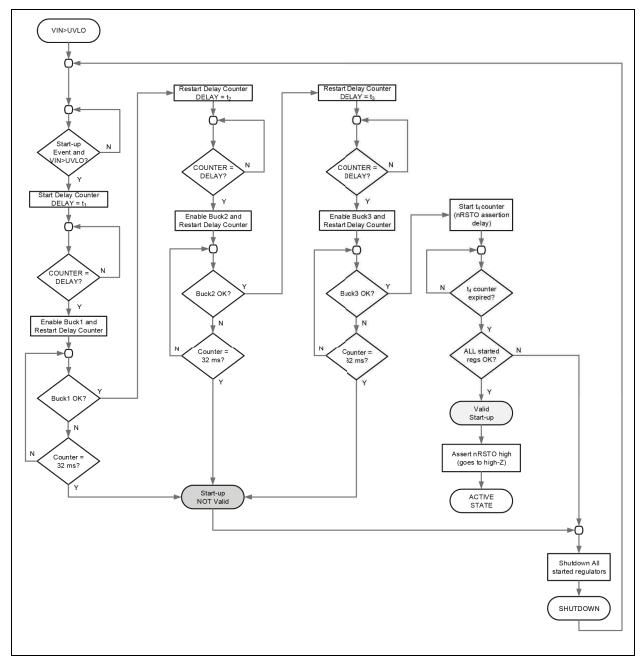

# 4.4.2 POWER-UP SEQUENCE FLOWCHART

The start-up sequence is divided into three steps and each Buck regulator is assigned to a specific sequence step:

- Step 1 (Buck1) regulator is started after a delay (t<sub>1</sub>) from the start-up event. If the start-up event is no longer valid as the instant t<sub>1</sub> expires, the start-up sequence is aborted before the first regulator is started.

- Step 2 (Buck2) regulator is started after a delay (t<sub>2</sub>) since the completion of the sequence Step 1 (regulator enabled at Step 1 has been powered up correctly).

- Step 3 (Buck3) regulator is started after a delay (t<sub>3</sub>) from the completion of the sequence Step 2 (regulator enabled at Step 2 has been powered up correctly).

The subsequent assertion of nRSTO is determined by the status of all regulators that have been turned on during the power-up sequence Their status is checked before starting counter  $t_4$  and again checked at the expiration of  $t_4$  to have nRSTO deasserted.

After the completion of the power-up sequence (i.e., at the time instant nRSTO is deasserted), the MCP16501 will enter the Power Modes state machine operation defined by the LPM and PWRHLD signals, and the corresponding device setting.

Some regulators which are supposed to turn on in the power-up sequence may fail to power up correctly.

In this case, the sequencing engine adds a 32 ms waiting time to allow the affected regulators to recover. After the expiration of the 32 ms period, if the affected regulators have still not recovered, the start-up sequence is aborted and the MCP16501 returns to its OFF state.

The start-up sequence flowchart is described in Figure 4-6 on the next page.

FIGURE 4-6: Start-up Sequence Flowchart.

# 4.4.3 DROPOUT SAFE START-UP SEQUENCE FEATURE

The start-up sequence management of MCP16501 ensures predictable timing between subsequent steps, even if some power channels may operate in dropout conditions with moderate loading.

This situation might occur for Buck1 because its output voltage range (up to 3.7V) is overlapping the input supply range (2.7V-5.5V).

This operating condition is frequently encountered in battery-powered applications. For example, some loads designed for a 3.3V nominal supply voltage may not be able to withstand the fully replenished battery voltage (around 4.2V), and therefore, they would require a front-end regulator. However, they could still operate when the battery voltage has decreased low enough to push their front-end regulator into dropout.

For example, if the battery voltage is around 3.1V and the Buck1 output voltage is also set to 3.3V, it is still desirable to start Buck1 and proceed throughout the start-up sequence, even if the POK (Power OK) threshold for Buck1 may not be reached, since Buck1 is still delivering a voltage within the I/O operating voltage range. This would allow a better exploitation of the battery because the cutoff voltage is no longer dictated by the onset of the dropout of the 3.3V regulator (Buck1) and by its POK threshold.

By means of a dedicated circuit that monitors the input-output differential during start-up of the potentially affected regulators, the MCP16501 can still ensure a proper start-up. The MPU can then detect the anomaly (e.g. by measuring the output of Buck1) and decide either to continue operation or to shut down the system.

The Start-up POK Bypass Threshold is the relevant "Electrical Characteristics" table parameter that defines the acceptable level of input-output differential, to continue through the start-up sequence, in lack of the normal POK.

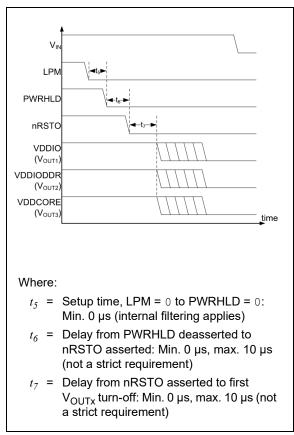

# 4.4.4 TYPICAL POWER-DOWN SEQUENCE AND TIMING

The power-down (shutdown) sequence can be initiated by the MPU by deasserting PWRHLD (LPM being already low or deasserted simultaneously). This method assumes that the MCP16501 is in any operating state (i.e., is outside the start-up sequence).

After PWRHLD has been deasserted nRSTO will immediately be asserted low by the MCP16501. After that, all active channels will be turned off, with the exception of the LDO which is controlled by LEN. For the MCP16501D, the LDO will be turned off by virtue of the connection of LEN to VOUT1.

The turn-off of each channel also activates the active discharge (if enabled) on the same channel.

The timing diagram in Figure 4-7 shows the typical sequence for the power down