# Real-Time Ethernet Multiprotocol (REM) Switch

#### **FEATURES**

- 2 independent Ethernet ports: 1 MII and 1 RMII interface per port

- ▶ Support for all industrial protocols

- ▶ PROFINET Class B and Class C

- ▶ EtherNet/IP, CIP Sync, and CIP Motion

- Modbus TCP

- ▶ EtherCAT

- ▶ Host interface transfer rate: 32 bits per 28 ns

- ▶ PI Net Load Class III capable

- ▶ DLR MRP

- ▶ IEEE 802.3, 10 Mbps/100 Mbps, half and full duplex, IPv6 and IPv4 communication

- IEEE 1588 Version 2 support: ordinary clock; both peer to peer and end to end transparent clocks, raw frames, and UDP

- 8 independent timer signals synchronized with an internal precision timer

- 4 independently programmable timer signals for timer capture events or timer output events

- 4 timer signals create programmable periodic waveforms synchronized to the internal precision timer

- ▶ DCP, LLDP, DHCP, RSTP, VLAN, IGMP snooping support

- Forwarding table with aging and learning

- ▶ Drive LEDs for link activity

- ► -40°C to +105°C industrial temperature range rating

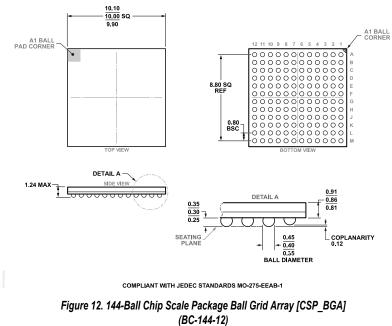

- ▶ 144-lead CSP\_BGA RoHS compliant package

#### **APPLICATIONS**

- Industrial automation

- Process control

- Instrumentation

- Intelligent buildings

#### **GENERAL DESCRIPTION**

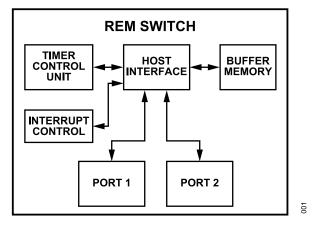

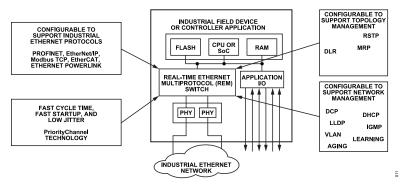

The fido5100 and fido5200 are real-time Ethernet, multiprotocol (REM), two-port switches. The REM switches provide customers the flexibility to select processors that best fit the application. The switches offer 10 Mbps/100 Mbps throughput and support most Layer 2 or Layer 3 protocols.

The fido5100 supports PROFINET real-time (RT) and isochronous real-time (IRT), EtherNet/IP with and without device level ring (DLR), Modbus TCP, and POWERLINK. The fido5200 supports EtherCAT and all protocols defined for the fido5100. The switches contain software drivers for each protocol. The software drivers provide an API for integration with any field device or protocol stack.

The REM switch architecture incorporates Analog Devices, Inc. PriorityChannel<sup>™</sup> technology for efficient data transfers. Data is transferred to and from the switch using PriorityChannel queues. Thus, real-time data transfers can interrupt non-real-time data transfers to ensure timely delivery of critical data. These queues are managed by the switch driver and interface to the protocol stack to achieve the most efficient data transfers without application software involvement.

Additionally, PriorityChannel technology allows the switches to be immune to network loading effects. The REM switches automatically filter packets to prevent unwanted traffic from the processor, manage low priority traffic based on processor loading, and guarantee the timely delivery of high priority packets regardless of overall packet load.

The software drivers include a standard set of interfaces to support standard, low priority, TCP/IP communications, basic switch initialization, timer configuration, and interrupt management. This interface is common to all REM switch drivers, easing the porting of the application to each supported protocol. Each protocol has its own interface that configures the REM switch for optimal operation. This configuration is transparent to the user and can be performed at any time, including a soft-boot to change protocols without resetting the host processor or PHYs.

Rev. G

DOCUMENT FEEDBACK

**TECHNICAL SUPPORT**

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                    | 1 |

|---------------------------------------------|---|

| Applications                                | 1 |

| General Description                         | 1 |

| Functional Block Diagram                    |   |

| Specifications                              | 4 |

| REM Switch Characteristics                  | 4 |

| Timing Specifications—Nonmultiplexed        |   |

| Address Data Bus                            | 4 |

| Timing Specifications—Multiplexed Address   |   |

| Data Bus                                    | 5 |

| Absolute Maximum Ratings                    | 7 |

| ESD Caution                                 | 7 |

| Pin Configuration and Function Descriptions | 8 |

| Theory of Operation1                        | 2 |

| Device Interfaces1                          |   |

| Internal Precision Timer               |    |

|----------------------------------------|----|

| Host Interface                         | 12 |

| Ethernet Interface                     | 16 |

| Applications Information               | 18 |

| REM Switch Hardware                    |    |

| Board Layout                           |    |

| Design Considerations                  |    |

| RapID Platform Generation 2 (RPG2)     |    |

| Solution                               | 19 |

| Silicon Anomaly                        |    |

| fido5100/fido5200 Functionality Issues |    |

| Functionality Issues                   | 20 |

| Outline Dimensions                     | 21 |

| Ordering Guide                         | 21 |

| -                                      |    |

#### **REVISION HISTORY**

| 1/2024—Rev. F to Rev. G                                                                    |    |

|--------------------------------------------------------------------------------------------|----|

| Changes to Features Section                                                                | 1  |

| Changes to Applications Section                                                            |    |

| Changes to General Description Section                                                     | 1  |

| Moved Figure 1                                                                             |    |

| Deleted Note 1, Table 1                                                                    | 4  |

| Changes to TIMER0 to TIMER3 Inputs/Outputs Section                                         | 12 |

| Changes to Endianness Section                                                              | 13 |

| Changes to Register and Data Access Section                                                |    |

| Changes to Interrupts Section                                                              | 16 |

| Changes to Figure 11                                                                       | 18 |

| Changes to REM Switch Hardware Section                                                     | 18 |

| Changes to REM Switch Drivers Section                                                      | 18 |

| Added Silicon Anomaly Section                                                              | 20 |

| Added fido5100/fido5200 Functionality Issues Section and Table 18; Renumbered Sequentially | 20 |

| Added Functionality Issues Section and Table 19                                            | 20 |

|                                                                                            |    |

#### 8/2022—Rev. E to Rev. F

| Changes to Operating Temperature Range (T <sub>A</sub> ) Industrial Parameter, Table 4 | 7 |

|----------------------------------------------------------------------------------------|---|

| Changes to Figure 6 and Table 5                                                        |   |

| Changes to Physical Layer (PHY) Section                                                |   |

| Added RapID Platform Generation 2 (RPG2) Solution Section                              |   |

| Changes to Ordering Guide                                                              |   |

|                                                                                        |   |

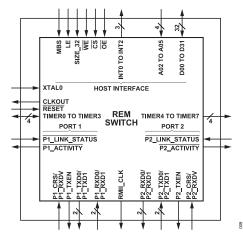

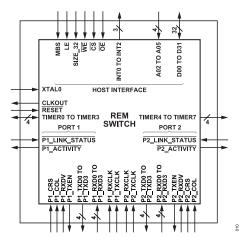

#### FUNCTIONAL BLOCK DIAGRAM

### **SPECIFICATIONS**

#### **REM SWITCH CHARACTERISTICS**

#### Table 1.

| Parameter                                   | Min  | Тур  | Max   | Unit | Test Conditions/Comments                                  |

|---------------------------------------------|------|------|-------|------|-----------------------------------------------------------|

| OPERATING CONDITIONS                        |      |      |       |      |                                                           |

| Core Voltage                                | 1.08 | 1.2  | 1.32  | V    |                                                           |

| Core Current                                |      |      | 48    | mA   | At T <sub>A</sub> = 85°C                                  |

| Input/Output (I/O) Buffers                  | 2.97 | 3.3  | 3.63  | V    | 3.3 V power supply                                        |

| I/O Current                                 |      |      | 0.035 | mA   | At T <sub>A</sub> = 85°C                                  |

| PLL Analog Voltage Regulator Power Supply   | 1.08 | 1.2  | 1.32  | V    |                                                           |

| DC Input Voltage                            | -0.5 |      | +3.8  | V    |                                                           |

| Output Voltage                              | -0.5 |      | +3.8  | V    |                                                           |

| Operating Junction Temperature (Industrial) | -40  |      | +125  | °C   |                                                           |

| DC CHARACTERISTICS (I/O STANDARD)           |      |      |       |      |                                                           |

| 3.3 V LVCMOS                                |      |      |       |      |                                                           |

| VCC+3V3                                     | 2.97 | 3.3  | 3.63  | V    | Voltage level applied to the VCC+3V3 signal               |

| Input Voltage                               |      |      |       |      |                                                           |

| Low (V <sub>IL</sub> )                      | -0.3 |      | +0.8  | V    |                                                           |

| High (V <sub>IH</sub> )                     | 2.0  |      | 3.6   | V    |                                                           |

| Output Voltage                              |      |      |       |      |                                                           |

| Low (V <sub>OL</sub> )                      |      |      | 0.4   | V    |                                                           |

| High (V <sub>OH</sub> )                     | 2.4  |      |       | V    |                                                           |

| Output Current                              |      |      |       |      |                                                           |

| Low (I <sub>OL</sub> )                      | 8.2  | 13.0 | 16.1  | mA   |                                                           |

| High (I <sub>OH</sub> )                     | 9.2  | 19.2 | 30.7  | mA   |                                                           |

| LEAKAGE CURRENT                             |      |      |       |      |                                                           |

| Input Pin                                   | -10  |      | +10   | μA   | Input voltage (V <sub>IN</sub> ) = 0 V to 3.3 V maximum   |

| Tristated I/O Pin                           | -10  |      | +10   | μA   | Output voltage (V <sub>OUT</sub> ) = 0 V to 3.3 V maximum |

| HOST INTERFACE TRANSFER RATE                |      | 32   |       | Bits | Per 28 ns                                                 |

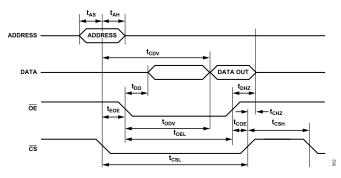

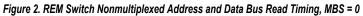

### TIMING SPECIFICATIONS—NONMULTIPLEXED ADDRESS DATA BUS

| Parameter         | Min | Тур | Max | Unit | Description                                |

|-------------------|-----|-----|-----|------|--------------------------------------------|

| t <sub>AS</sub>   | 2   |     |     | ps   | Address setup time                         |

| t <sub>AH</sub>   | 370 |     |     | ps   | Address hold time                          |

| t <sub>CDV</sub>  |     |     | 20  | ns   | CS to data valid time                      |

| t <sub>ODV</sub>  |     |     | 20  | ns   | Output enable to data valid time           |

| t <sub>OEL</sub>  | 20  |     |     | ns   | Output enable low time                     |

| t <sub>CSH</sub>  | 8   |     |     | ns   | CS high time                               |

| t <sub>CSL</sub>  | 20  |     |     | ns   | CS low time                                |

| t <sub>EOE</sub>  | 0   |     |     | ns   | CS to output enable time                   |

| t <sub>COE</sub>  | 0   |     |     | ns   | Output enable high to $\overline{CS}$ high |

| t <sub>DO</sub>   | 150 |     |     | ps   | Output enable to data drive time           |

| t <sub>DHZ</sub>  |     |     | 110 | ps   | Output disable to high-Z time              |

| t <sub>CHZ</sub>  |     |     | 110 | ps   | CS high to high-Z time                     |

| t <sub>WES</sub>  | 0   |     |     | ns   | CS to write enable                         |

| t <sub>WEWC</sub> | 16  |     |     | ns   | Write enable to write complete             |

| t <sub>WECS</sub> | 0   |     |     | ns   | Write enable high to $\overline{CS}$ high  |

| t <sub>DS</sub>   | 30  |     |     | ps   | Data setup to WE high                      |

#### **SPECIFICATIONS**

#### Table 2. Nonmultiplexed Address Data Bus—Read and Write Cycle Timing<sup>1, 2, 3</sup> (Continued)

| Parameter       | Min | Тур | Max | Unit | Description                   |

|-----------------|-----|-----|-----|------|-------------------------------|

| t <sub>DH</sub> | 30  |     |     | ps   | Input data hold after WE high |

<sup>1</sup> The MBS pin determines whether the host interfaced has multiplexed or separate address and data lines. When MBS = 0, the interface is nonmultiplexed.

<sup>2</sup> OE can be taken low before CS. Therefore, t<sub>EOE</sub> can be a negative value. In this case, a board designer must closely monitor t<sub>DO</sub> and t<sub>CDV</sub> to avoid bus contention and ensure proper data transfer.

<sup>3</sup> The read bus cycle terminates when either  $\overline{CS}$  or  $\overline{OE}$  is taken high. Therefore, a negative value for t<sub>COE</sub> is acceptable in some circumstances.

#### Timing Diagrams, Nonmultiplexed REM Switch

Figure 3. REM Switch Nonmultiplexed Address and Data Bus Write Timing, MBS = 0

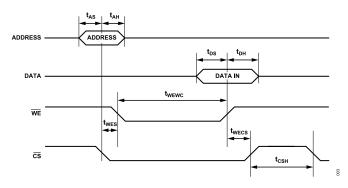

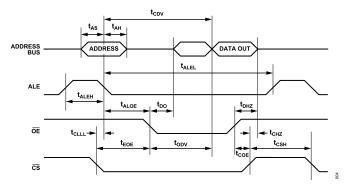

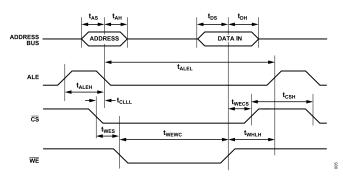

#### TIMING SPECIFICATIONS—MULTIPLEXED ADDRESS DATA BUS

| Table 3. Multiplexed Address Data Bus—Read and Write Cycle Timing <sup>1</sup> |     |     |     |      |                               |  |

|--------------------------------------------------------------------------------|-----|-----|-----|------|-------------------------------|--|

| Parameter                                                                      | Min | Тур | Max | Unit | Description                   |  |

| t <sub>ALEH</sub>                                                              | 8   |     |     | ns   | ALE high time                 |  |

| t <sub>ALEL</sub>                                                              | 16  |     |     | ns   | ALE low time                  |  |

| t <sub>AS</sub>                                                                | 170 |     |     | ps   | Address setup time            |  |

| t <sub>AH</sub>                                                                | 170 |     |     | ps   | Address hold time             |  |

| t <sub>CDV</sub>                                                               |     |     | 20  | ns   | ALE to valid data             |  |

| t <sub>ALOE</sub>                                                              | 2   |     |     | ns   | ALE to output enable          |  |

| t <sub>ODV</sub>                                                               |     |     | 20  | ns   | Output enable to data valid   |  |

| t <sub>DHZ</sub>                                                               |     |     | 150 | ps   | Output disable to high-Z time |  |

| t <sub>CHZ</sub>                                                               |     |     | 150 | ps   | CS high to high-Z time        |  |

| t <sub>CLLL</sub>                                                              | 0   |     |     | ns   | CS low to ALE low             |  |

| t <sub>CSH</sub>                                                               | 8   |     |     | ns   | CS high time                  |  |

### **SPECIFICATIONS**

| Parameter         | Min | Тур | Max | Unit | Description                        |

|-------------------|-----|-----|-----|------|------------------------------------|

| t <sub>EOE</sub>  | 2   |     |     | ns   | CS to output enable                |

| t <sub>DO</sub>   | 2   |     | 110 | ps   | Output enable to output drive time |

| t <sub>COE</sub>  | 0   |     |     | ns   | Output disable to CS high          |

| t <sub>WES</sub>  | 0   |     |     | ns   | CS to write enable                 |

| t <sub>WEWC</sub> | 16  |     |     | ns   | Write enable to write complete     |

| t <sub>WECS</sub> | 0   |     |     | ns   | Write enable high to CS high       |

| t <sub>WHLH</sub> | 0   |     |     | ns   | WE high to next ALE high           |

| t <sub>DS</sub>   | 60  |     |     | ps   | Data setup to WE high              |

| t <sub>DH</sub>   | 60  |     |     | ps   | Input data hold after WE high      |

<sup>1</sup> The MBS pin determines whether the host interfaced has multiplexed or separate address and data lines. When MBS = 1, the interface is multiplexed.

#### **Timing Diagrams, Multiplexed REM Switch**

Figure 4. REM Switch Multiplexed Address and Data Bus Read Timing, MBS = 1

#### **ABSOLUTE MAXIMUM RATINGS**

#### Table 4.

| Parameter                                                  | Rating             |

|------------------------------------------------------------|--------------------|

| Power Supply                                               |                    |

| Core Voltage and Periphery Circuitry                       | 1.08 V to 1.32 V   |

| I/O (VCC+3V3)                                              | 2.97 V to 3.63 V   |

| PLL Analog                                                 | 1.08 V to 1.32 V   |

| DC Input Voltage                                           | -0.5 V to +3.8 V   |

| Operating Temperature Range (T <sub>A</sub> ) Industrial   | -40°C to +105°C    |

| Storage Temperature (No Bias) Range                        | -65°C to +150°C    |

| Electrostatic Discharge (ESD) Voltage, Human Body<br>Model | -2000 V to +2000 V |

| Lead Temperature (Soldering)                               | J-STD-020C1        |

| Power Dissipation                                          | 172.6 mW           |

<sup>1</sup> Compliant with JEDEC Standard J-STD-020C and restriction of hazardous substances (RoHS), Directive 2002/95/EU. Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### ESD CAUTION

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

|   |            |            |            |         |         | TOP      | WITCH<br>VIEW<br>Scale) |         |         |          |         |                    |

|---|------------|------------|------------|---------|---------|----------|-------------------------|---------|---------|----------|---------|--------------------|

|   | 1          | 2          | 3          | 4       | 5       | 6        | 7                       | 8       | 9       | 10       | 11      | 12                 |

| A | D02/AD02   | D04/AD04   | D07        | D11     | D15     | D18      | D19                     | D22     | D25     | D27      | D30     | D31                |

| в | D01        | D03/AD03   | D06        | D10     | D14     | D17      | D20                     | D23     | D26     | D29      | ŌĒ      | WE                 |

| с | A04/UNUSED | D00        | D05/AD05   | D09     | D13     | D16      | D21                     | D24     | D28     | INT2     | INT1    | INTO               |

| D | A02/ALE    | A03/UNUSED | A05/UNUSED | D08     | D12     | VCC+1V2  | GND                     | VCC+3V3 | GND     | TIMER7   | TIMER6  | cs                 |

| Е | RESET      | LE         | SIZE_32    | GND     | VCC+1V2 | GND      | VCC+1V2                 | GND     | VCC+3V3 | TIMER5   | TIMER4  | TIMER3             |

| F | GND        | MBS        | GND        | VCC+3V3 | GND     | VCC+1V2  | GND                     | GND     | GND     | TIMER2   | TIMER1  | TIMER0             |

| G | XTAL0      | XTAL1      | VCC+1V2A   | GND     | VCC+1V2 | GND      | GND                     | VCC+1V2 | GND     | RMILCLK  | CLKOUT  | P2_ACTIVITY        |

| н | GND        | VCC+3V3    | GND        | VCC+3V3 | GND     | VCC+1V2  | GND                     | GND     | VCC+3V3 | P2_CRS   | P2_COL  | P2_LINK_<br>STATUS |

| J | P1_TXEN    | P1_TXCLK   | NC         | GND     | VCC+3V3 | GND      | VCC+1V2                 | NC      | NC      | GND      | P2_RXDV | P2_RXCLK           |

| к | P1_TXD0    | NC         | NC         | GND     | GND     | P1_RXDV  | P1_LINK_<br>STATUS      | P2_TXD1 | NC      | P2_RXD0  | GND     | GND                |

| L | P1_TXD1    | P1_TXD2    | P1_RXD0    | P1_RXD3 | GND     | P1_CRS   | Ρ1_ΑΟΤΙΥΙΤΥ             | P2_TXD0 | P2_TXD3 | NC       | P2_RXD2 | GND                |

| м | P1_TXD3    | NC         | P1_RXD1    | P1_RXD2 | GND     | P1_RXCLK | P1_COL                  | P2_TXEN | P2_TXD2 | P2_TXCLK | P2_RXD1 | P2_RXD3            |

|   |            |            |            | VCC+1V2 | vcc·    | +3V3     | VCC+1V2                 |         | GND     | ] 1/0    |         |                    |

Figure 6. Pin Configuration

#### Table 5. Pin Function Descriptions

**Data Sheet**

| Pin No. | Mnemonic | Direction <sup>1</sup> | Description                                                                                                               |

|---------|----------|------------------------|---------------------------------------------------------------------------------------------------------------------------|

| A1      | D02/AD02 | I/O                    | Data Bus Bit 02 Nonmultiplexed/Data Bus Bit 02 Multiplexed. This is a multifunction pin.                                  |

|         |          |                        | When MBS = 0, Pin A1 (D02) is Data Bus Bit 02 to and from the REM switch for the nonmultiplexed address data bus.         |

|         |          |                        | When MBS = 1, Pin A1 (AD02) is for the multiplexed address data bus, Bit 02 of the address (LSB), and Bit 02 of the data. |

| A2      | D04/AD04 | I/O                    | Data Bus Bit 04 Nonmultiplexed/Data Bus Bit 04 Multiplexed. This is a multifunction pin.                                  |

|         |          |                        | When MBS = 0, Pin A2 (D04) is Data Bus Bit 04 to and from the REM switch for the nonmultiplexed address data bus.         |

|         |          |                        | When MBS = 1, Pin A2 (AD04) is for the multiplexed address data bus, Bit 04 of the address, Bit 04 of the data.           |

| A3      | D07      | I/O                    | Data Bus Bit 07. Pin A3 is Data Bus Bit 07 to and from the REM switch.                                                    |

| A4      | D11      | I/O                    | Data Bus Bit 11. Pin A4 is Data Bus Bit 11 to and from the REM switch.                                                    |

| A5      | D15      | I/O                    | Data Bus Bit 15. Pin A5 is Data Bus Bit 15 to and from the REM switch.                                                    |

| A6      | D18      | I/O                    | Data Bus Bit 18. Pin A6 is Data Bus Bit 18 to and from the REM switch.                                                    |

| A7      | D19      | I/O                    | Data Bus Bit 19. Pin A7 is Data Bus Bit 19 to and from the REM switch.                                                    |

| A8      | D22      | I/O                    | Data Bus Bit 22. Pin A8 is Data Bus Bit 22 to and from the REM switch.                                                    |

| A9      | D25      | I/O                    | Data Bus Bit 25. Pin A9 is Data Bus Bit 25 to and from the REM switch.                                                    |

#### Table 5. Pin Function Descriptions (Continued)

| Pin No. | Mnemonic                        | Direction <sup>1</sup> | Description                                                                                                                                                                                              |

|---------|---------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10     | D27                             | I/O                    | Data Bus Bit 27. Pin A10 is Data Bus Bit 27 to and from the REM switch.                                                                                                                                  |

| A11     | D30                             | I/O                    | Data Bus Bit 30. Pin A11 is Data Bus Bit 30 to and from the REM switch.                                                                                                                                  |

| A12     | D31                             | I/O                    | Data Bus Bit 31. Pin A12 is Data Bus Bit 31 to and from the REM switch.                                                                                                                                  |

| B1      | D01                             | I/O                    | Data Bus Bit 01. Pin B1 is Data Bus Bit 01 to and from the REM switch.                                                                                                                                   |

| B2      | D03/AD03                        | 1/0                    | Data Bus Bit 03 Nonmultiplexed/Data Bus Bit 03 Multiplexed. This is a multifunction pin.                                                                                                                 |

| 52      | 200/1/200                       |                        | When MBS = 0, Pin B2 (D03) is Data Bus Bit 03 to and from the REM switch for the                                                                                                                         |

|         |                                 |                        | nonmultiplexed address data bus.                                                                                                                                                                         |

|         |                                 |                        | When MBS = 1, Pin B2 (AD03) is for the multiplexed address data bus, Bit 03 of the address, Bit 03 of the data.                                                                                          |

| B3      | D06                             | I/O                    | Data Bus Bit 06. Pin B3 is Data Bus Bit 06 to and from the REM switch.                                                                                                                                   |

| B4      | D10                             | I/O                    | Data Bus Bit 10. Pin B4 is Data Bus Bit 10 to and from the REM switch.                                                                                                                                   |

| B5      | D14                             | I/O                    | Data Bus Bit 14. Pin B5 is Data Bus Bit 14 to and from the REM switch.                                                                                                                                   |

| B6      | D17                             | I/O                    | Data Bus Bit 17. Pin B6 is Data Bus Bit 17 to and from the REM switch.                                                                                                                                   |

| B7      | D20                             | 1/0                    | Data Bus Bit 20. Pin B7 is Data Bus Bit 20 to and from the REM switch.                                                                                                                                   |

| B8      | D23                             | 1/0                    | Data Bus Bit 23. Pin B8 is Data Bus Bit 23 to and from the REM switch.                                                                                                                                   |

| B9      | D26                             | 1/0                    | Data Bus Bit 26. Pin B9 is Data Bus Bit 26 to and from the REM switch.                                                                                                                                   |

| B10     | D29                             | 1/0                    | Data Bus Bit 29. Pin B10 is Data Bus Bit 29 to and from the REM switch.                                                                                                                                  |

| B10     | <del>DZ3</del><br><del>OE</del> | 1                      | Output Enable. Setting Pin B11 low allows the REM switch to drive data lines.                                                                                                                            |

| B12     | WE                              |                        |                                                                                                                                                                                                          |

| C1      | A04/UNUSED                      |                        | Write Enable. Setting Pin B12 low enables a write; setting Pin B12 high enables a read.                                                                                                                  |

| CT CT   | AU4/UNUSED                      |                        | Address Line 04/Multiplexed Address Bus (UNUSED). This is a multifunction pin.                                                                                                                           |

|         |                                 |                        | Pin C1 is Address Line 04 when MBS = 0 for the nonmultiplexed address data bus. When MBS = 1, Pin C1 is Bit 04 of the address bus. Line A04 is sampled on the falling edge of $\overline{CS}$ (Pin D12). |

|         |                                 |                        | Pin C1 is unused when MBS = 1 for the multiplexed address data bus.                                                                                                                                      |

| C2      | D00                             | I/O                    | Data Bus Bit 00. C2 is Data Bus Bit 00 to and from the REM switch.                                                                                                                                       |

| C3      | D05/AD05                        | I/O                    | Data Bus Bit 05 Nonmultiplexed/Data Bus Bit 05 Multiplexed. This is a multifunction pin.                                                                                                                 |

|         |                                 |                        | When MBS = 0, Pin C3 (D05) is Data Bus Bit 05 to and from the REM switch for the<br>nonmultiplexed address data bus.                                                                                     |

|         |                                 |                        | When MBS = 1, Pin C3 (AD05) is for the multiplexed address data bus, Bit 05 of the address, Bit 05 of the data.                                                                                          |

| C4      | D09                             | I/O                    | Data Bus Bit 09. Pin C4 is Data Bus Bit 09 to and from the REM switch.                                                                                                                                   |

| C5      | D13                             | I/O                    | Data Bus Bit 13. Pin C5 is Data Bus Bit 13 to and from the REM switch.                                                                                                                                   |

| C6      | D16                             | I/O                    | Data Bus Bit 16. Pin C6 is Data Bus Bit 16 to and from the REM switch.                                                                                                                                   |

| C7      | D21                             | I/O                    | Data Bus Bit 21. Pin C7 is Data Bus Bit 21 to and from the REM switch.                                                                                                                                   |

| C8      | D24                             | I/O                    | Data Bus Bit 24. Pin C8 is Data Bus Bit 24 to and from the REM switch.                                                                                                                                   |

| C9      | D28                             | I/O                    | Data Bus Bit 28. Pin C9 is Data Bus Bit 28 to and from the REM switch.                                                                                                                                   |

| C10     | INT2                            | 0                      | Interrupt 2 Output to Host Processor. Pin C10 can be configured to respond to one or more internal events.                                                                                               |

| C11     | INT1                            | 0                      | Interrupt 1 Output to Host Processor. Pin C11 can be configured to respond to one or more internal events.                                                                                               |

| C12     | INTO                            | 0                      | Interrupt 0 Output to Host Processor. Pin C12 can be configured to respond to one or more internal events.                                                                                               |

| D1      | A02/ALE                         | 1                      | Address Line 02/Address Latch Enable. This is a multifunction pin.                                                                                                                                       |

|         |                                 | N/A                    | Pin D1 is Address Line 02 when MBS = 0 for the nonmultiplexed address data bus. When MBS =                                                                                                               |

|         |                                 |                        | 0, Pin D1 is Bit 02 of the address bus. Line A02 is sampled on the falling edge of $\overline{CS}$ (Pin D12). The addresses are 32-bit aligned/addressable.                                              |

|         |                                 |                        | When MBS = 1, this pin is the address latch enable pin.                                                                                                                                                  |

| D2      | A03/UNUSED                      | 1                      | Address Line 03/Multiplexed Address Bus. This is a multifunction pin.                                                                                                                                    |

|         |                                 |                        | Pin D2 is Address Line 03 when MBS = 0 for the nonmultiplexed address data bus. When MBS =                                                                                                               |

|         |                                 |                        | 0, Pin D2 is Bit 03 of the address bus. Line A03 is sampled on the falling edge of CS (Pin D12).<br>The addresses are 32-bit aligned/addressable.                                                        |

#### Table 5. Pin Function Descriptions (Continued)

| Pin No.                                                                                                                                | Mnemonic       | Direction <sup>1</sup> | Description                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                        |                |                        | Pin D2 is unused when MBS = 1 for the multiplexed address data bus.                                                                                                                                                                                    |

| D3                                                                                                                                     | A05/UNUSED     | 1                      | Address Line 05/Multiplexed Address Bus. This is a multifunction pin.                                                                                                                                                                                  |

|                                                                                                                                        |                |                        | Pin D3 is Address Line 05 when MBS = 0 for the nonmultiplexed address data bus. When MBS = 0, Pin D3 is Bit 05 of the address bus. Line A05 is sampled on the falling edge of $\overline{CS}$ (Pin D12). The addresses are 32-bit aligned/addressable. |

|                                                                                                                                        |                |                        | Pin D3 is unused when MBS = 1 for the multiplexed address data bus.                                                                                                                                                                                    |

| D4                                                                                                                                     | D08            | I/O                    | Data Bus Bit 08. Pin D4 is Data Bus Bit 08 to and from the REM switch.                                                                                                                                                                                 |

| D5                                                                                                                                     | D12            | I/O                    | Data Bus Bit 12. Pin D5 is Data Bus Bit 12 to and from the REM switch.                                                                                                                                                                                 |

| D6, E5, E7, F6, G5, G8, H6, J7                                                                                                         | VCC+1V2        | N/A                    | 1.2 V Power Supply.                                                                                                                                                                                                                                    |

| D7, D9, E4, E6, E8, F1, F3,<br>F5, F7, F8, F9, G4, G6, G7,<br>G9, H1, H3, H5, H7, H8, J4,<br>J6, J10, K4, K5, K11, K12, L5,<br>L12, M5 | GND            | N/A                    | Ground.                                                                                                                                                                                                                                                |

| D8, E9, F4, H2, H4, H9, J5                                                                                                             | VCC+3V3        | N/A                    | 3.3 V Power Supply.                                                                                                                                                                                                                                    |

| D10                                                                                                                                    | TIMER7         | 0                      | Internal Precision Timer Clock 7 Synchronized. Pin D10 is a programmable output.                                                                                                                                                                       |

| D11                                                                                                                                    | TIMER6         | 0                      | Internal Precision Timer Clock 6 Synchronized. Pin D11 is a programmable output.                                                                                                                                                                       |

| D12                                                                                                                                    | CS             | 1                      | Address Bus Chip Select. The address bus is sampled on the falling edge of $\overline{CS}$ . A rising edge on $\overline{CS}$ terminates the current read or write cycle.                                                                              |

| E1                                                                                                                                     | RESET          | I                      | Reset. When Pin E1 is asserted low, all internal registers initialize and bus configuration pins<br>enable for sampling.                                                                                                                               |

| E2                                                                                                                                     | LE             | I                      | System Endianness. When Pin E2 is set high, the data format is little endian. When Pin E2 is set low, the data format is big endian. The value is captured on the rising edge of RESET.                                                                |

| E3                                                                                                                                     | SIZE_32        | I                      | Data Bus Size. The data bus size is 32 bits when Pin E3 is set high and 16 bits when Pin E3 is set low. The value is captured on the rising edge of RESET.                                                                                             |

| E10                                                                                                                                    | TIMER5         | 0                      | Internal Precision Timer Clock 5 Synchronized. Pin E10 is a programmable output.                                                                                                                                                                       |

| E11                                                                                                                                    | TIMER4         | 0                      | Internal Precision Timer Clock 4 Synchronized. Pin E11 is a programmable output.                                                                                                                                                                       |

| E12                                                                                                                                    | TIMER3         | I/O                    | Internal Precision Timer 3 Clock Synchronized. Pin E12 is a programmable output or input.                                                                                                                                                              |

| F2                                                                                                                                     | MBS            | 1                      | Multiplex Bus Select. When Pin F2 is set high, the host interface bus operates as a multiplexed bus. The host interface operates as a nonmultiplexed bus when Pin F2 is set low. The value is captured on the rising edge of Pin E1, RESET.            |

| F10                                                                                                                                    | TIMER2         | I/O                    | Internal Precision Timer Clock 2 Synchronized. Pin F10 is a programmable output or input.                                                                                                                                                              |

| F11                                                                                                                                    | TIMER1         | I/O                    | Internal Precision Timer Clock 1 Synchronized. Pin F11 is a programmable output or input.                                                                                                                                                              |

| F12                                                                                                                                    | TIMER0         | I/O                    | Internal Precision Timer Clock 0 Synchronized. Pin F12 is a programmable output or input.                                                                                                                                                              |

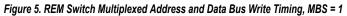

| G1                                                                                                                                     | XTAL0          |                        | Clock Input. This pin has a frequency of 25 MHz.                                                                                                                                                                                                       |

| G2                                                                                                                                     | XTAL1          |                        | Output Pair for XTAL0. Pin G2 is required for use with a crystal clock source.                                                                                                                                                                         |

| G3                                                                                                                                     | VCC+1V2A       |                        | Analog 1.2 V Power Supply. This pin must be isolated from VCC+1V2.                                                                                                                                                                                     |

| G10                                                                                                                                    | RMII_CLK       | 0                      | 50 MHz Reduced Media Independent Interface (RMII) Transmit and Receive Clock Reference for<br>Port 1 and Port 2.                                                                                                                                       |

| G11                                                                                                                                    | CLKOUT         | 0                      | Output Clock. Pin G11 has the same frequency as XTAL0 (25 MHz).                                                                                                                                                                                        |

| G12                                                                                                                                    | P2_ACTIVITY    | 0                      | Port 2 Activity LED Output Driver. The LED turns on when G12 is asserted low.                                                                                                                                                                          |

| H10                                                                                                                                    | P2_CRS         | 1                      | Port 2 Carrier Sense. When H10 is asserted high, a carrier has been sensed on Port 2.                                                                                                                                                                  |

| H11                                                                                                                                    | P2_COL         | 1                      | Port 2 Media Independent Interface (MII) Collision. Pin H11 asserting high indicates a collision on Port 2.                                                                                                                                            |

| H12                                                                                                                                    | P2_LINK_STATUS | 1                      | Port 2 Link Status from Physical Layer (PHY). When H12 is asserted low, the link on Port is active.                                                                                                                                                    |

| J1                                                                                                                                     | P1_TXEN        | 0                      | Port 1 MII Transmit Enable. Setting Pin J1 high enables transmission on Port 1.                                                                                                                                                                        |

| J2                                                                                                                                     | P1_TXCLK       | 1                      | Port 1 MII Transmit Clock from PHY.                                                                                                                                                                                                                    |

| J3, J8, J9, K2, K3, K9, L10,<br>M2,                                                                                                    | NC             | N/A                    | No Connection.                                                                                                                                                                                                                                         |

| J11                                                                                                                                    | P2_RXDV        | I                      | Port 2 Received Data Valid. Data from the Port 2 PHY is valid when J11 is asserted high (used as CRS/RXDV in RMII mode).                                                                                                                               |

#### Table 5. Pin Function Descriptions (Continued)

| Pin No. | Mnemonic       | Direction <sup>1</sup> | Description                                                                                                                             |

|---------|----------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| J12     | P2_RXCLK       | I                      | Port 2 MII Receive Clock from PHY.                                                                                                      |

| K1      | P1_TXD0        | 0                      | Transmit Data Output Bit 0 for Port 1 MII and RMII.                                                                                     |

| K6      | P1_RXDV        | 1                      | Port I MII Received Data Valid. Asserting Pin K6 high indicates that data from the Port 1 PHY is valid (used as CRS/RXDV in RMII mode). |

| K7      | P1_LINK_STATUS | 1                      | Port 1 Link Status from PHY. Asserting Pin K7 low activates the Port 1 link.                                                            |

| K8      | P2_TXD1        | 0                      | Transmit Data Output Bit 1 for Port 2 MII and RMII.                                                                                     |

| K10     | P2_RXD0        | 1                      | Receive Data Input Bit 0 for Port 2 MII and RMII.                                                                                       |

| L1      | P1_TXD1        | 1                      | Transmit Data Output Bit 1 for Port 1 MII and RMII.                                                                                     |

| L2      | P1_TXD2        | 0                      | Transmit Data Output Bit 2 for Port 1 MII.                                                                                              |

| L3      | P1_RXD0        | 1                      | Receive Data Input Bit 0 for Port 1 MII and RMII.                                                                                       |

| L4      | P1_RXD3        | 1                      | Receive Data Input Bit 3 for Port 1 MII.                                                                                                |

| L6      | P1_CRS         | 1                      | Port 1 Carrier Sense. When L6 is asserted high, a carrier has been sensed on Port 1.                                                    |

| L7      | P1_ACTIVITY    | 0                      | Port 1 Activity LED Output Driver. The LED turns on when Pin L7 is asserted low.                                                        |

| L8      | P2_TXD0        | 0                      | Transmit Data Output Bit 0 for Port 2 MII and RMII.                                                                                     |

| _9      | P2_TXD3        | 0                      | Transmit Data Output Bit 3 for Port 2 MII.                                                                                              |

| L11     | P2_RXD2        | 1                      | Receive Data Input Bit 2 for Port 2 MII.                                                                                                |

| M1      | P1_TXD3        | 0                      | Transmit Data Output Bit 3 for Port 1 MII.                                                                                              |

| M3      | P1_RXD1        | 1                      | Receive Data Input Bit 1 for Port 1 MII AND RMII.                                                                                       |

| M4      | P1_RXD2        | 1                      | Receive Data Input Bit 2 for Port 1 MII.                                                                                                |

| M6      | P1_RXCLK       | 1                      | Port I MII Receive Clock from PHY.                                                                                                      |

| M7      | P1_COL         | 1                      | Port 1 MII Collision. Asserting Pin M7 high indicates a collision on Port 1.                                                            |

| M8      | P2_TXEN        | 0                      | Port 2 MII Transmit Enable. Setting Pin M8 to high enables the Port 2 transmit.                                                         |

| M9      | P2_TXD2        | 0                      | Transmit Data Output Bit 2 for Port 2 MII.                                                                                              |

| M10     | P2_TXCLK       | 1                      | Port 2 MII Transmit Clock from PHY.                                                                                                     |

| M11     | P2_RXD1        | 1                      | Receive Data Input Bit 1 for Port 2 MII and RMII.                                                                                       |

| M12     | P2_RXD3        | 1                      | Receive Data Input Bit 3 for Port 2 MII.                                                                                                |

$^{1}\;$  I is input, I/O is input/output, O is output, and N/A is not applicable.

#### **DEVICE INTERFACES**

#### Oscillator

The oscillator clock source is routed to an internal phase-locked loop (PLL) to create the following clock sources:

- ▶ 25 MHz for the CLKOUT reference clock

- ▶ 50 MHz for the RMII reference clock

An oscillator used as a clock source requires a tighter tolerance.

Figure 7. Oscillator Clock Source Circuit

# Crystal

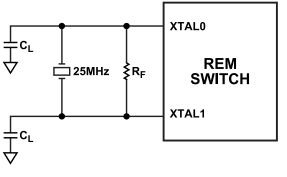

When using the REM switch with a crystal, use an oscillator pad configuration, as shown Figure 8.

Figure 8. Crystal Clock Source Circuit

The values presented in the following list are typical for operation when using a 25 MHz crystal:

- ESR = 40 Ω

- ▶ C<sub>L</sub> = 8 pF

- R<sub>F</sub> = 1 MΩ

#### **Reset Timing**

The timing requirement for RESET is a minimum active low time of 16 ns.

# INTERNAL PRECISION TIMER

The REM switch includes an internal precision timer (IPT). The IPT maintains a system time that has a resolution of 1 ns. Use the IPT to trigger timer output events or capture input event times on the TIMER0, TIMER1, TIMER2, and TIMER3 pins, or to create a complex pulse pattern on the TIMER4, TIMER5, TIMER6, and TIMER7 pins.

#### **TIMER0 to TIMER3 Inputs/Outputs**

TIMER0 to TIMER3 inputs/outputs can be configured to either time stamp an input event or time trigger an output event. When configured to time stamp an input event, the value of the IPT is captured in a 64-bit register when the associated timer signal transitions from low to high. User software reads this register and uses the value to time stamp an associated event. For example, when the TIMER0 signal transitions from low to high, the value of the IPT is stored in the Timer 0, 64-bit register (consult the UG-1285, *REM Switch Software Driver User Guide* for more details). The same is true when configuring TIMER1, TIMER2, or TIMER3 to time stamp input events. User software uses the generated time stamp to associate the time stored in the 64-bit register with a particular event.

When configured to time trigger an output event, the timer signal toggles when the IPT reaches the value stored in the Timer x, 64-bit register. The process of time triggering an output event is as follows using the Timer 0 register in the example:

- 1. The host processor software stores a value in the Timer 0, 64-bit register.

- 2. The IPT reaches that value stored in the Timer 0, 64-bit register.

- 3. The TIMER0 pin toggles from high to low or low to high (depending on its state when the 64-bit register was loaded).

- 4. The same process is followed when the TIMER1, TIMER2, and TIMER3 pins are configured to time trigger output events.

#### **TIMER4 to TIMER7 Outputs**

TIMER4 to TIMER7 outputs are configured to output independent, IPT clock synchronized, programmable, pulse-width modulated signals. Each of these timers has a resolution of 16 ns. Each timer can have its own pulse-width modulation program that allows an arbitrary number of rising and falling edges, depending on the protocols that repeat on a programmable interval. The software drivers for the REM switch provide the capability to define the rising and falling edges for each TIMERx output.

#### HOST INTERFACE

008

#### **Multiplex Bus Select**

The host interface supports a separate address bus and data bus or a multiplexed address and data bus. The selection between the two types of busses is provided by the MBS signal (Pin F2),

#### analog.com

which is sampled on the rising edge of RESET. See Table 5 for pin function descriptions for the MBS and RESET signals.

#### Data Bus Width

The host interface supports either a 16-bit or 32-bit wide data bus. The data bus width is determined by the SIZE 32 (Pin E3) signal that is sampled on the rising edge of RESET. See Table 5 for pin function descriptions for the SIZE 32 and RESET signals.

#### Endianness

The host interface presents data on the data bus in either big endian or little endian format. The endianness of the data is determined by the LE signal (Pin E2), which is sampled on the rising edge of the **RESET** signal. See Table 5 for pin function descriptions for the LE and RESET signals.

The REM switch data bus is defined as follows:

- ▶ D0 = I SB

- ▶ D15 = MSB for 16-bit bus

- ▶ D31 = MSB for 32-bit bus

For all control/status register accesses, there is no difference in operation based on the setting of the LE pin. The data representation in a host processor register must match the data that is transferred over the bus.

All control/status registers are 16-bits wide. If using a 32-bit bus, transfer the data in the following order: D15 to D0 (D31 to D16 are

ignored when using a 32-bit bus). For example, the REM switch driver reads the device number register early in the initialization process. In the case of the number, 0x00003300, the value read from this register must be transferred across the bus, as shown in Table 6 and Table 7. When evaluated in the software on the host processor, the value of these 32 bits results in 0x00003300.

For queue accesses, the REM switch treats all data as byte arrays. Consider the following example of a stream of bytes received over an Ethernet cable into a REM switch port and then transferred to the host. The packet data in network order is as follows: 0x00. 0x01, 0x02, 0x03, 0x04, 0x05, 0x06, 0x07, 0x08, 0x09, 0x0A, 0x0B, 0x0C, 0x0D, 0x0E, 0x0F.

The data is read differently depending on the setting, as follows:

- ▶ Big endian 16-bit host interface: 0x0001, 0x0203, 0x0405, 0x0607, 0x0809, 0x0A0B, 0x0C0D, 0x0E0F.

- ▶ Big endian 32-bit host interface: 0x00010203, 0x04050607, 0x08090A0B, 0x0C0D0E0F.

- ▶ Little endian 16-bit host interface: 0x0100, 0x0302, 0x0504, 0x0706, 0x0908, 0x0B0A, 0x0D0C, 0x0F0E.

- ▶ Little endian 32-bit host interface: 0x03020100, 0x07060504, 0x0B0A0908, 0x0F0E0D0C.

Consult the UG-1285, REM Switch Software Driver User Guide for more details on how to handle endianness in an application of a device.

| 31                                                   | D30                                               | D29                                                  | D28                                              | D27                                                | D26                                           | D25                                          | D24                                              | D23                                         | D22                          | D21            | D20                          | D19       | D18            | D17            | D16            |

|------------------------------------------------------|---------------------------------------------------|------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|-----------------------------------------------|----------------------------------------------|--------------------------------------------------|---------------------------------------------|------------------------------|----------------|------------------------------|-----------|----------------|----------------|----------------|

|                                                      | 0                                                 | 0                                                    | 0                                                | 0                                                  | 0                                             | 0                                            | 0                                                | 0                                           | 0                            | 0              | 0                            | 0         | 0              | 0              | 0              |

| able 7                                               | . Control/S                                       | tatus Regi                                           | sters Bit N                                      | lap—Bits[l                                         | D15:D0]                                       |                                              |                                                  |                                             |                              |                |                              |           |                |                |                |

| 15                                                   | D14                                               | D13                                                  | D12                                              | D11                                                | D10                                           | D9                                           | D8                                               | D7                                          | D6                           | D5             | D4                           | D3        | D2             | D1             | D0             |

|                                                      | 0                                                 | 1                                                    | 1                                                | 0                                                  | 0                                             | 1                                            | 1                                                | 0                                           | 0                            | 0              | 0                            | 0         | 0              | 0              | 0              |

| able 8                                               | . Big Endia                                       | n 16-Bit Da                                          | ata Bus Bi                                       | t Map, 0x0                                         | E0F Hexad                                     | ecimal—B                                     | its[D31:D1                                       | 6]                                          |                              |                |                              |           |                |                |                |

| 31                                                   | D30                                               | D29                                                  | D28                                              | D27                                                | D26                                           | D25                                          | D24                                              | D23                                         | D22                          | D21            | D20                          | D19       | D18            | D17            | D16            |

|                                                      |                                                   |                                                      |                                                  |                                                    |                                               |                                              |                                                  |                                             |                              |                |                              |           |                |                |                |

|                                                      | 0                                                 | 0                                                    | 0                                                | 0                                                  | 0                                             | 0                                            | 0                                                | 0                                           | 0                            | 0              | 0                            | 0         | 0              | 0              | 0              |

| able 9                                               | 0<br>. Big Endia<br>D14                           |                                                      |                                                  |                                                    |                                               |                                              |                                                  |                                             | 0<br>D6                      | 0<br>D5        | 0<br>D4                      | 0<br>D3   | 0<br>D2        | 0<br>D1        | 0<br>D0        |

| able 9<br>15                                         | . Big Endia                                       | n 16-Bit Da                                          | ata Bus Bi                                       | t Map, 0x0                                         | E0F Hexad                                     | ecimal—B                                     | its[D15:D0                                       | 1                                           |                              |                | -                            |           | -              | -              |                |

| <i>able 9</i><br>015                                 | . Big Endia<br>D14                                | <b>D 16-Bit D</b> a<br>D13                           | ata Bus Bi<br>D12                                | t Map, 0x0<br>D11                                  | <b>EOF Hexad</b><br><b>D10</b>                | ecimal—B<br>D9                               | Dits[D15:D0<br>D8                                | <b>D7</b>                                   | D6                           | D5             | D4                           |           | -              | D1             | D0             |

| Table 9<br>015<br>)<br>Table 1                       | . Big Endia<br>D14<br>0                           | <b>D 16-Bit D</b> a<br>D13                           | ata Bus Bi<br>D12                                | t Map, 0x0<br>D11                                  | <b>EOF Hexad</b><br><b>D10</b>                | ecimal—B<br>D9                               | Dits[D15:D0<br>D8                                | <b>D7</b>                                   | D6                           | D5             | D4                           |           | -              | D1             | <b>D0</b>      |

| Table 9<br>15<br>Table 1<br>131                      | . Big Endia<br>D14<br>0<br>0. Big Endi            | n 16-Bit Di<br>D13<br>0<br>ian 32-Bit L              | ata Bus Bi<br>D12<br>0<br>Data Bus E             | t Map, 0x0<br>D11<br>1<br>Bit Map, 0x              | EOF Hexad<br>D10<br>1<br>0C0D0E0F             | ecimal—B<br>D9<br>1<br>Hexadecii             | D15:D0<br>D8<br>0<br>mal—Bits[l                  | ]<br>D7<br>0<br>D31:D16]                    | <b>D6</b><br>0               | <b>D5</b><br>0 | <b>D4</b>                    | <b>D3</b> | <b>D2</b>      | <b>D1</b>      | D0             |

| Fable 9<br>015<br>Fable 1<br>031                     | . Big Endia<br>D14<br>0<br>0. Big Endi<br>D30     | in 16-Bit Di<br>D13<br>0<br>ian 32-Bit I<br>D29<br>0 | ata Bus Bi<br>D12<br>0<br>Data Bus B<br>D28<br>0 | t Map, 0x0<br>D11<br>1<br>Bit Map, 0x0<br>D27<br>1 | EOF Hexad<br>D10<br>1<br>0C0D0E0F<br>D26<br>1 | ecimal—B<br>D9<br>1<br>Hexadecii<br>D25<br>0 | bits[D15:D0<br>D8<br>0<br>mal—Bits[i<br>D24<br>0 | <b>D7</b><br>0<br>0<br>031:D16]<br>D23<br>0 | <b>D6</b><br>0<br><b>D22</b> | D5<br>0<br>D21 | <b>D4</b><br>0<br><b>D20</b> | <b>D3</b> | D2<br>1<br>D18 | D1<br>1<br>D17 | D0<br>1<br>D16 |

| <b>D15</b><br>0<br><i>Table 1</i><br><b>D31</b><br>0 | . Big Endia<br>D14<br>0<br>. Big Endi<br>D30<br>0 | in 16-Bit Di<br>D13<br>0<br>ian 32-Bit I<br>D29<br>0 | ata Bus Bi<br>D12<br>0<br>Data Bus B<br>D28<br>0 | t Map, 0x0<br>D11<br>1<br>Bit Map, 0x0<br>D27<br>1 | EOF Hexad<br>D10<br>1<br>0C0D0E0F<br>D26<br>1 | ecimal—B<br>D9<br>1<br>Hexadecii<br>D25<br>0 | bits[D15:D0<br>D8<br>0<br>mal—Bits[i<br>D24<br>0 | <b>D7</b><br>0<br>0<br>031:D16]<br>D23<br>0 | <b>D6</b><br>0<br><b>D22</b> | D5<br>0<br>D21 | <b>D4</b><br>0<br><b>D20</b> | <b>D3</b> | D2<br>1<br>D18 | D1<br>1<br>D17 | D0<br>1<br>D16 |

#### Table 12. Little Endian 16-Bit Data Bus Bit Map, 0x0E0F Hexadecimal—Bits[D31:D16]

| ) 0                     |             | D29         | D28        | D27        | D26       | D25       | D24        | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

|-------------------------|-------------|-------------|------------|------------|-----------|-----------|------------|-----|-----|-----|-----|-----|-----|-----|-----|

|                         | ) (         | 0           | 0          | 0          | 0         | 0         | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| able 13. Litt           | ttle Endian | n 16-Bit Da | ata Bus Bi | t Map, 0x0 | E0F Hexad | decimal—E | Bits[D15:D | 0]  |     |     |     |     |     |     |     |

| D15 D                   | D14 I       | D13         | D12        | D11        | D10       | D9        | D8         | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| ) 0                     | ) (         | 0           | 0          | 1          | 1         | 1         | 1          | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0   |

| Table 14. Litt<br>D31 D |             |             | D28        | D27        | D26       | D25       | D24        | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| )31 D                   | D30 I       | D29         | D28        | D27        | D26       | D25       | D24        | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| )   0                   | ן ו         | 0           | 0          | 1          | 1         | 1         | 1          | 0   | 0   | 0   | 0   |     |     |     | 0   |

#### Address/Data Bus Operation

The host interface address/data bus connects to the address/ data bus of the CPU. There are four bits of data for the address bus and either 16 bits or 32 bits of data for the data bus. Each REM switch address is 32-bit aligned, meaning that the addresses increment by four bytes (A05 to A02). Regardless of whether the data bus is 16 bits wide or 32 bits wide, the least significant address bit supplied to the REM switch is always the same.

In addition, all accesses to indirect registers return the register data in the lower 16 bits only (even if the interface is 32 bits wide). For wider registers, such as a 64-bit timer, use a repeated set of reads or writes to access the full content of the register.

#### Nonmultiplexed Address Data Bus

MBS = 0 selects the nonmultiplexed address data bus configuration. The read and write cycle timings are defined in Figure 2 and Figure 3. See Table 2 for the read and write cycle timing parameters.

#### **Multiplexed Address Data Bus**

Table 16. Direct Address Register Definitions

MBS = 1 selects the multiplexed address data bus configuration. The read and write cycle timings are defined in Figure 4 and Figure 5. See Table 3 for the read and write cycle timing parameters.

#### **Register and Data Access**