# Quad-Port, IEEE 802.3af/at **PSE Controller for Power over Ethernet**

### **DESCRIPTION**

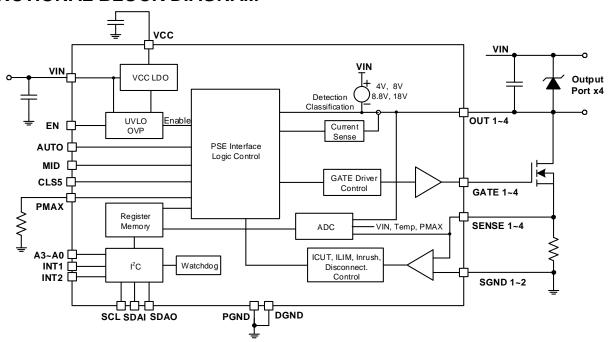

The MP3924 is a quad-port power source equipment (PSE) power controller for IEEE 802.3af/at compliant power over Ethernet (PoE) applications.

The device has all the functions of IEEE 802.3af/at, including detection, single-event and two-event classification, current limiting, and disconnected load detection. All of the functions can be configured to work in automatic operation mode or software program mode via the I2C.

The MP3924 features a 9-bit analog-to-digital converter (ADC) to monitor the current and voltage, a special I2C interface for isolated controller communication, adjustable current limits, and configurable system functions. These features provide flexibility for PoE applications.

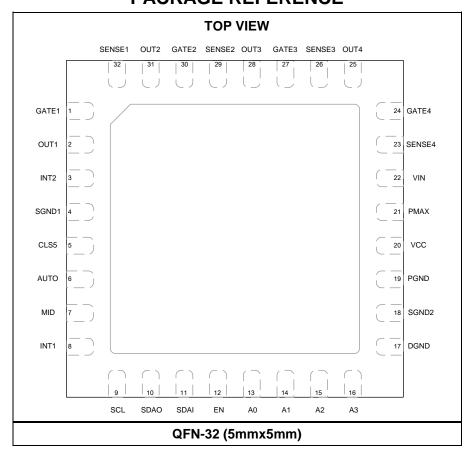

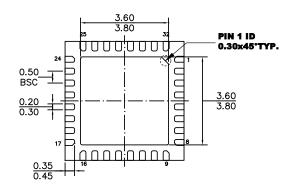

The MP3924 is available in a QFN-32 (5mmx5mm) package.

#### **FEATURES**

- IEEE802.3af/at Compliant

- Quad-Port and 4-Bit Configurable I<sup>2</sup>C Address

- 0.25Ω Current-Sense Resistor

- Automatic Mode and I<sup>2</sup>C Command Control Mode

- Automatic Input Over-Power Shutdown

- Internal VCC Power Supply

- Three-Wire I<sup>2</sup>C Interface for Isolated **Applications**

- Two INT Pins for Interrupt Priority Selection

- Disconnected DC Load Detection

- Instantaneous Current/Voltage Readout

- Thermal Protection

- Available in a QFN-32 (5mmx5mm) Package

## **APPLICATIONS**

- PSE Switches/Routers

- **PSE Midspan Power Injectors**

- Surveillance NVR and DVRs

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

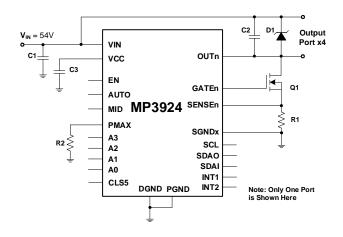

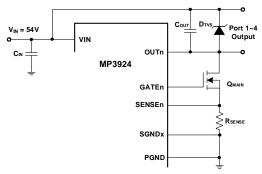

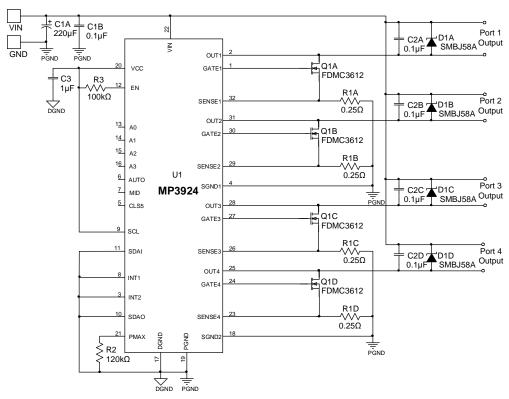

### TYPICAL APPLICATION

© 2021 MPS. All Rights Reserved.

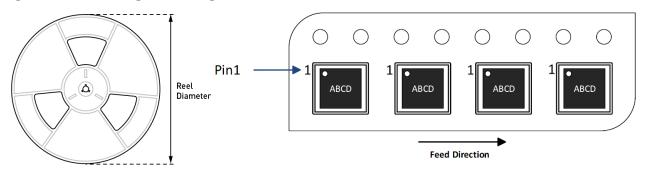

### ORDERING INFORMATION

| Part Number | Package          | Top Marking | MSL Rating |

|-------------|------------------|-------------|------------|

| MP3924GU*   | QFN-32 (5mmx5mm) | See Below   | 2          |

| EVKT-MP3924 | Evaluation kit   | -           |            |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP3924GU-Z).

## **TOP MARKING**

M<u>PSYYWW</u> MP3924 LLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP3924: Part number LLLLLL: Lot number

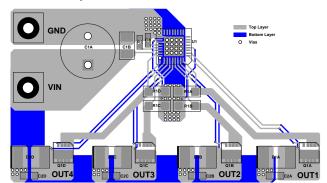

### **EVALUATION KIT EVKT-MP3924**

EVKT-MP3924 kit contents (items listed below can be ordered separately, and the GUI installation file and supplemental documents can be downloaded from the MPS website):

| # | Part Number    | Item                                                                                                     | Quantity |

|---|----------------|----------------------------------------------------------------------------------------------------------|----------|

| 1 | EV3924-U-00A   | MP3924 evaluation board                                                                                  | 1        |

| 2 | EVKT-USBI2C-02 | Includes one USB to I <sup>2</sup> C communication interface device, one USB cable, and one ribbon cable | 1        |

| 3 | MP3924GU       | MP3924 controller IC                                                                                     | 2        |

#### Order directly from MonolithicPower.com or our distributors.

Figure 1: EVKT-MP3924 Evaluation Kit Set-Up

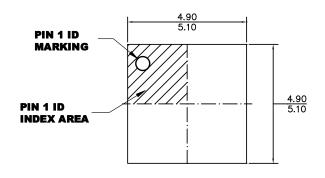

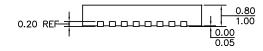

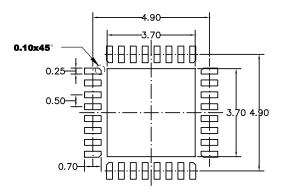

# **PACKAGE REFERENCE**

# **PIN FUNCTIONS**

| Pin# | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | GATE1 | MOSFET gate driver for port 1. Float the GATE1 pin if not used.                                                                                                                                                                                                                                                                                                                                                             |

| 2    | OUT1  | Output voltage sense pin for port 1. Connect OUT1 to the output interface return for detecting, classifying, voltage sensing, and current limit foldback control. Float the OUT1 pin if not used.                                                                                                                                                                                                                           |

| 3    | INT2  | <b>High-priority interrupt request pin.</b> INT2 pulls low when the selected high-priority interrupt source register is set and the interrupt is enabled. INT2 is an open-drain output. Connect INT2 to DGND if the interrupt function is not used.                                                                                                                                                                         |

| 4    | SGND1 | Current sense negative input for port 1 and port 2. Connect SGND1 to the low-side terminal of the sense resistor. For an accurate current sense, use a Kelvin connection when connecting SGND1 to the PCB. Connect SGND1 to DGND if not used.                                                                                                                                                                               |

| 5    | CLS5  | Class 5 enable input. CLS5 is internally pulled down to DGND through a $50k\Omega$ resistor. Leave CLS5 disconnected to disable the classification for Class 5 devices (IEEE 802.3at-compliant mode). Connect CLS5 to VCC to enable the classification of Class 5 devices. CLS5's status is latched when the device starts up, or after a reset condition. If CLS5's status changes after start-up, there is no effect.     |

| 6    | AUTO  | <b>Automatic mode setting pin.</b> AUTO is internally pulled up to VCC through a $50k\Omega$ resistor (an external $10k\Omega$ resistor can be added). Float the AUTO pin to make automatic mode the default. Connect the AUTO pin to DGND to make shutdown mode the default. AUTO's status is latched when the device starts up, or after a reset condition. If AUTO's status changes after start-up, there is no effect.  |

| 7    | MID   | <b>Midspan mode setting.</b> MID is internally pulled up to VCC through a $50k\Omega$ resistor (an external $10k\Omega$ resistor can be added). Float the MID pin for midspan mode, then wait 2.8s to reinitiate detection. Connect the MID pin to DGND to disable midspan mode. MID's status is latched when the device starts up, or after a reset condition. If MID's status changes after start-up, there is no effect. |

| 8    | INT1  | <b>Interrupt request pin for all interrupt source events.</b> INT1 pulls low when the interrupt register is set and the interrupt function is enabled. INT1 is an open-drain output. Connect INT1 to DGND if the interrupt function is not used.                                                                                                                                                                            |

| 9    | SCL   | $I^2C$ clock input pin. Connect SCL to VCC using an external pull-up resistor (typically 4.7kΩ). Connect SCL to VCC if the $I^2C$ interface is not used.                                                                                                                                                                                                                                                                    |

| 10   | SDAO  | $I^2$ C serial data output pin. SDAO is an open-drain output. Connect SDAO to VCC using an external pull-up resistor (typically 4.7kΩ). Connect SDAO to SDAI for non-isolated applications. Connect SDAO to DGND if the $I^2$ C interface is not used.                                                                                                                                                                      |

| 11   | SDAI  | $I^2C$ serial data input pin. Connect SDAI to VCC using an external pull-up resistor (typically 4.7kΩ). Connect SDAI to SDAO for non-isolated applications. Connect SDAI to DGND if the $I^2C$ interface is not used.                                                                                                                                                                                                       |

| 12   | EN    | <b>Enable input.</b> EN turns all internal circuits and four ports (except the VCC regulator) on and off. To turn on the device automatically, externally connect EN to VCC.                                                                                                                                                                                                                                                |

| 13   | A0    | MP3924 address setting pin. Connect A0 to VCC or DGND to set the lower 4-bit address bits (address = 010 A3 A2 A1 A0). The address signal is latched when the device starts up or is reset. A0 is internally pulled up to VCC through a $50k\Omega$ resistor (an external $10k\Omega$ resistor can also be added).                                                                                                          |

| 14   | A1    | MP3924 address setting pin. Connect A1 to VCC or DGND to set the lower 4-bit address bits (Address = 010 A3 A2 A1 A0). The address signal is latched when the device starts up or is reset A1 is internally pulled up to VCC through a $50k\Omega$ resistor (an external $10k\Omega$ resistor can also be added).                                                                                                           |

# PIN FUNCTIONS (continued)

| Pin# | Name   | Description                                                                                                                                                                                                                                                                                                          |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | A2     | <b>MP3924 address setting pin.</b> Connect A2 to VCC or DGND to set the lower 4-bit address bits (Address = 010 A3 A2 A1 A0). The address signal is latched when the device starts up or is reset. A2 is internally pulled up to VCC through a $50k\Omega$ resistor (an external $10k\Omega$ resistor can be added). |

| 16   | А3     | MP3924 address setting pin. Connect A3 to VCC or DGND to set the lower 4-bit address bits (Address = 010 A3 A2 A1 A0). The address signal is latched when the device starts up or is reset. A3 is internally pulled up to VCC through a $50k\Omega$ resistor (an external $10k\Omega$ resistor can also be added).   |

| 17   | DGND   | Ground of the internal digital and analog circuit.                                                                                                                                                                                                                                                                   |

| 18   | SGND2  | Current sense negative input for port 3 and port 4. Connect SGND2 to the low-side terminal of the sense resistor. For an accurate current sense, use a Kelvin connection when connecting SGND2 to the PCB. Connect SGND2 to DGND if not used.                                                                        |

| 19   | PGND   | Ground of input power supply.                                                                                                                                                                                                                                                                                        |

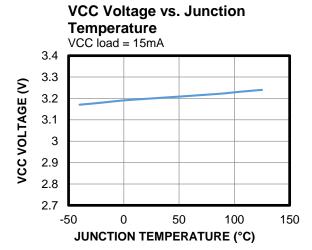

| 20   | VCC    | 3.3V internal regulator output for analog and digital circuit supply. A minimum 1µF ceramic capacitor must be placed between VCC and DGND.                                                                                                                                                                           |

| 21   | PMAX   | <b>Maximum loading power setting pin.</b> Connect one resistor from the PMAX pin to DGND to set the total power capability on all four output ports. The MP3924 limits the total power on all four ports below this set limit. The PMAX setting signal is latched when the device starts up or is reset.             |

| 22   | VIN    | <b>Power supply input for both VCC and output ports.</b> Bypass VIN with at least one 0.1µF/100V ceramic capacitor, placed between VIN and PGND.                                                                                                                                                                     |

| 23   | SENSE4 | Current-sense pin from the high-side sense resistor terminal for port 4. It is recommended to use a $0.25\Omega$ sense resistor for all applications. For an accurate current sense, use a Kelvin connection when connecting SENSE4 during PCB layout. Connect SENSE4 to DGND if not used.                           |

| 24   | GATE4  | MOSFET gate driver for port 4. Float the GATE4 pin if not used.                                                                                                                                                                                                                                                      |

| 25   | OUT4   | Output voltage sense pin for port 4. Connect OUT4 to the return of the output interface for detecting, classifying, voltage sensing, and current limit foldback control. Float the OUT4 pin if not used.                                                                                                             |

| 26   | SENSE3 | Current-sense pin from the high-side sense resistor terminal for port 3. It is recommended to use a $0.25\Omega$ sense resistor for all applications. For an accurate current sense, use a Kelvin connection when connecting SENSE3 during PCB layout. Connect SENSE3 to DGND if not used.                           |

| 27   | GATE3  | MOSFET gate driver for port 3. Float the GATE3 pin if not used.                                                                                                                                                                                                                                                      |

| 28   | OUT3   | Output voltage sense pin for port 3. Connect OUT3 to the return of the output interface for detecting, classifying, voltage sensing, and current limit foldback control. Float the OUT3 pin if it is not used.                                                                                                       |

| 29   | SENSE2 | Current-sense pin from the high-side sense resistor terminal for port 2. It is recommended to use a $0.25\Omega$ sense resistor for all applications. For an accurate current sense, use a Kelvin connection when connecting SENSE1 during PCB layout. Connect SENSE1 to DGND if not used.                           |

| 30   | GATE2  | MOSFET gate driver for port 2. Float the GATE2 pin if not used.                                                                                                                                                                                                                                                      |

| 31   | OUT2   | Output voltage sense pin for port 2. Connect OUT2 to the return of the output interface for detecting, classifying, voltage sensing, and current limit foldback control. Float the OUT2 pin if it is not used.                                                                                                       |

| 32   | SENSE1 | Current-sense pin from the high-side sense resistor terminal for port 1. It is recommended to use a $0.25\Omega$ sense resistor for all applications. For an accurate current sense, use a Kelvin connection when connecting SENSE1 during PCB layout. Connect SENSE1 to DGND if not used.                           |

# **ABSOLUTE MAXIMUM RATINGS (1)** V<sub>IN</sub> .....-0.3V to +80V OUT1~4.....-0.3V to V<sub>IN</sub> + 0.3V GATE1~4, SENSE1~4.....-0.3V to +22V DGND, SGND1, SGND2.....-0.3V to +0.3V All other pins......-0.3V to +6.5V INT1, INT2, SDAO maximum sink current....... ......20mA Continuous power dissipation ( $T_A = 25$ °C) ......3.9W <sup>(2)</sup> (4) Junction temperature .......150°C Storage temperature.....-65°C to +150°C Recommended Operating Conditions (3) Supply voltage (V<sub>IN</sub>) ...... 44V to 57V INT1, INT2, SDAO maximum sink current....... .....5mA Operating junction temp (T<sub>J</sub>)....-40°C to +125°C

| Thermal Resistance | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|--------------------|-------------------------|-------------------------|------|

| EV3924-U-00A (4)   | . 32                    | 2                       | °C/W |

| JESD51-7 (5)       | . 36                    | 8                       | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on EV3924-U-00A, 2-layer, 88mmx106mm PCB.

- 5) The value of θ<sub>JA</sub> given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

6

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}=54V$ , PGND, DGND, SGND1, and SGND2 are connected together,  $R_{SENSE}=0.25\Omega$ ,  $T_{J}=-40^{\circ}C$  to  $+125^{\circ}C$   $^{(6)}$ , typical value is tested at  $T_{J}=25^{\circ}C$ , unless otherwise noted.

| Symbol                  | Condition                                                                                                                                                                 | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                                                                                                                                                                           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

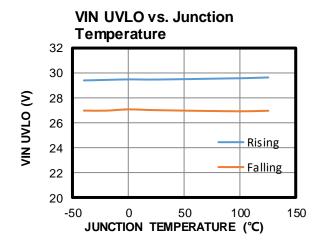

| VIN_UVLO                | V <sub>IN</sub> rising                                                                                                                                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VIN_UVLO_HYS            |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

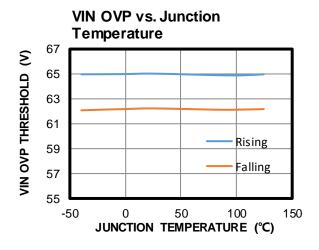

| V <sub>IN_OVP</sub>     | V <sub>IN</sub> rising                                                                                                                                                    | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>IN_OVP_HYS</sub> |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>IN_OK</sub>      | V <sub>IN</sub> rising                                                                                                                                                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VIN_OK_HYS              |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Vн                      |                                                                                                                                                                           | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VLI                     |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         | Pull EN to 0V, 3.3V                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ten_on                  | EN pin high pulse duration                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

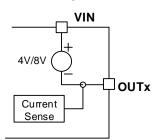

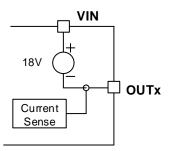

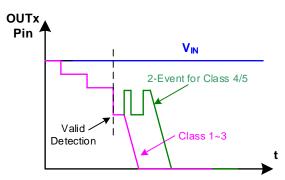

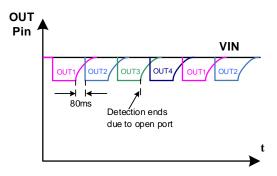

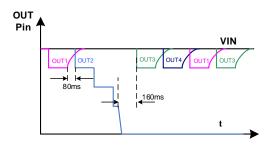

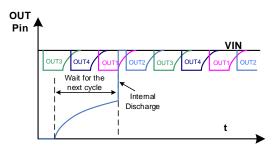

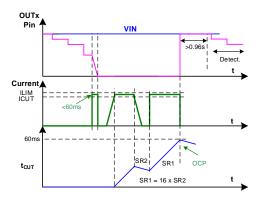

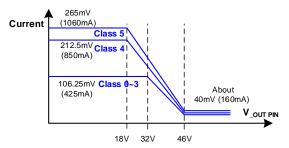

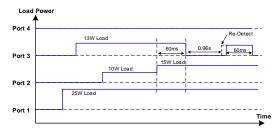

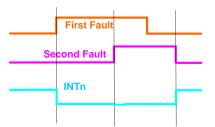

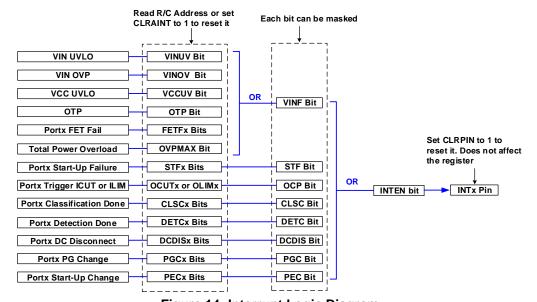

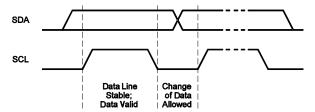

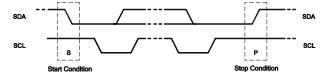

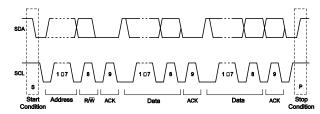

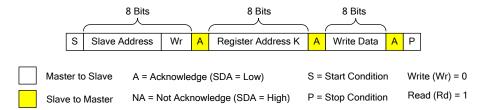

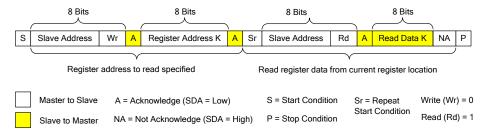

| t <sub>EN_OFF</sub>     | for start-up or low-pulse duration for shutdown                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |