# TC1017

## 150 mA, Tiny CMOS LDO With Shutdown

## Features:

- · Space-saving 5-Pin SC-70 and SOT-23 Packages

- Extremely Low Operating Current for Longer Battery Life: 53 µA (typ.)

- · Very Low Dropout Voltage

- · Rated 150 mA Output Current

- Requires Only 1 µF Ceramic Output Capacitance

- High Output Voltage Accuracy: ±0.5% (typical)

- 10 µs (typ.) Wake-Up Time from SHDN

- Power-Saving Shutdown Mode: 0.05 µA (typ.)

- Overcurrent and Overtemperature Protection

- · Pin-Compatible Upgrade for Bipolar Regulators

#### **Applications:**

- Cellular/GSM/PHS Phones

- Battery-Operated Systems

- · Portable Computers

- Medical Instruments

- Electronic Games

- · Pagers

#### **General Description:**

The TC1017 is a high-accuracy (typically  $\pm 0.5\%$ ) CMOS upgrade for bipolar Low Dropout regulators (LDOs). It is offered in a SC-70 or SOT-23 package. The SC-70 package represents a 50% footprint reduction versus the popular SOT-23 package and is offered in two pinouts to make board layout easier.

Developed specifically for battery-powered systems, the TC1017's CMOS construction consumes only 53  $\mu$ A typical supply current over the entire 150 mA operating load range. This can be as much as 60 times less than the quiescent operating current consumed by bipolar LDOs.

The TC1017 is designed to be stable, over the entire input voltage and output current range, with low-value  $(1 \ \mu F)$  ceramic or tantalum capacitors. This helps to reduce board space and save cost. Additional integrated features, such as shutdown, overcurrent and overtemperature protection, further reduce the board space and cost of the entire voltage-regulating application.

Key performance parameters for the TC1017 include low dropout voltage (285 mV typical at 150 mA output current), low supply current while shutdown (0.05  $\mu$ A typical) and fast stable response to sudden input voltage and load changes.

#### SC-70 **SOT-23** V<sub>OUT</sub> NC NC VIN VOUT VOUT 5 4 5 4 5 4 TC1017 TC1017R TC1017 2 3 3 2 3 VIN GND SHDN SHDN NC GND GND SHDN VIN

## Package Types

## 1.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings †

| Input Voltage              | 6.5V                            |

|----------------------------|---------------------------------|

| Power Dissipation          | Internally Limited (Note 7)     |

| Maximum Voltage On Any Pin | V <sub>IN</sub> + 0.3V to -0.3V |

**†** Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## **PIN FUNCTION TABLE**

| Name             | Function                 |

|------------------|--------------------------|

| SHDN             | Shutdown control input.  |

| NC               | No connect               |

| GND              | Ground terminal          |

| V <sub>OUT</sub> | Regulated voltage output |

| V <sub>IN</sub>  | Unregulated supply input |

## **ELECTRICAL CHARACTERISTICS**

**Electrical Specifications:** Unless otherwise noted,  $V_{IN} = V_R + 1V$ ,  $I_L = 100 \ \mu$ A,  $C_L = 1.0 \ \mu$ F,  $\overline{SHDN} > V_{IH}$ ,  $T_A = +25^{\circ}C$ **Boldface** type specifications apply for junction temperatures of  $-40^{\circ}C$  to  $+125^{\circ}C$ .

| Parameter                                | Sym.                                       | Min.                  | Тур.                  | Max.                   | Units  | Test Conditions                                                                           |

|------------------------------------------|--------------------------------------------|-----------------------|-----------------------|------------------------|--------|-------------------------------------------------------------------------------------------|

| Input Operating Voltage                  | V <sub>IN</sub>                            | 2.7                   | —                     | 6.0                    | V      | Note 1                                                                                    |

| Maximum Output Current                   | I <sub>OUTMAX</sub>                        | 100                   | —                     | —                      | mA     | Note 1                                                                                    |

|                                          |                                            | 150                   | _                     | _                      |        | $V_{IN} \ge 3V$ and<br>$V_{IN} \ge (V_R + 2.5\%) + V_{DROPOUTMAX}$                        |

| Output Voltage                           | V <sub>OUT</sub>                           | V <sub>R</sub> – 2.5% | V <sub>R</sub> ±0.5%  | V <sub>R</sub> + 2.5%  | V      | Note 2                                                                                    |

| V <sub>OUT</sub> Temperature Coefficient | TCV <sub>OUT</sub>                         |                       | 40                    | —                      | ppm/°C | Note 3                                                                                    |

| Line Regulation                          | $ (\Delta V_{OUT}/\Delta V_{IN})  / V_{R}$ | _                     | 0.04                  | 0.2                    | %/V    | $(V_{R} + 1V) < V_{IN} < 6V$                                                              |

| Load Regulation (Note 4)                 | $ \Delta V_{OUT}  / V_{R}$                 | _                     | 0.38                  | 1.5                    | %      | $I_L = 0.1 \text{ mA to } I_{OUTMAX}$                                                     |

| Dropout Voltage (Note 5)                 | V <sub>IN</sub> – V <sub>OUT</sub>         |                       | 2<br>90<br>180<br>285 | —<br>200<br>350<br>500 | mV     | $I_{L} = 100 \ \mu A$<br>$I_{L} = 50 \ m A$<br>$I_{L} = 100 \ m A$<br>$I_{L} = 150 \ m A$ |

| Supply Current                           | I <sub>IN</sub>                            | _                     | 53                    | 90                     | μA     | $\overline{\text{SHDN}} = V_{\text{IH}}, I_{\text{L}} = 0$                                |

| Shutdown Supply Current                  | I <sub>INSD</sub>                          | _                     | 0.05                  | 2                      | μA     | SHDN = 0V                                                                                 |

| Power Supply Rejection Ratio             | PSRR                                       | _                     | 58                    | —                      | dB     | f =1 kHz, I <sub>L</sub> = 50 mA                                                          |

Note 1: The minimum V<sub>IN</sub> has to meet two conditions:  $V_{IN} \ge 2.7V$  and  $V_{IN} \ge (V_R + 2.5\%) + V_{DROPOUT}$ .

**2:**  $V_R$  is the regulator voltage setting. For example:  $V_R$  = 1.8V, 2.7V, 2.8V, 3.0V.

$$TCV_{OUT} = \frac{(V_{OUTMAX} - V_{OUTMIN}) \times 10^6}{V_{OUT} \times \Delta T}$$

- 4: Regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is tested over a load range from 0.1 mA to the maximum specified output current. Changes in output voltage due to heating effects are covered by the thermal regulation specification.

- 5: Dropout voltage is defined as the input-to-output differential at which the output voltage drops 2% below its nominal value at a 1V differential.

- 6: Thermal regulation is defined as the change in output voltage at a time T after a change in power dissipation is applied, excluding load or line regulation effects. Specifications are for a current pulse equal to  $I_{LMAX}$  at  $V_{IN}$  = 6V for t = 10 msec.

- 7: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction-to-air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation causes the device to initiate thermal shutdown. Please see Section 5.1 "Thermal Shutdown", for more details.

- 8: Output current is limited to 120 mA (typ) when V<sub>OUT</sub> is less than 0.5V due to a load fault or short-circuit condition.

3:

0500

#### ELECTRICAL CHARACTERISTICS (CONTINUED) ----

| Parameter                             | Sym.                             | Min. | Тур. | Max. | Units            | Test Conditions                                                                                                       |

|---------------------------------------|----------------------------------|------|------|------|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Wake-Up Time<br>(from Shutdown mode)  | t <sub>wк</sub>                  | _    | 10   | _    | μs               | $V_{IN} = 5V, I_L = 60 mA,$<br>$C_{IN} = C_{OUT} = 1 \mu F,$<br>f = 100 Hz                                            |

| Settling Time<br>(from Shutdown mode) | t <sub>S</sub>                   | —    | 32   | _    | μs               | $V_{IN} = 5V, I_L = 60 \text{ mA},$<br>$C_{IN} = 1 \ \mu\text{F},$<br>$C_{OUT} = 1 \ \mu\text{F}, f = 100 \text{ Hz}$ |

| Output Short-Circuit Current          | I <sub>OUTSC</sub>               | _    | 120  | —    | mA               | V <sub>OUT</sub> = 0V, Average<br>Current (Note 8)                                                                    |

| Thermal Regulation                    | V <sub>OUT</sub> /P <sub>D</sub> | _    | 0.04 | _    | V/W              | Notes 6, 7                                                                                                            |

| Thermal Shutdown Die<br>Temperature   | T <sub>SD</sub>                  | —    | 160  | —    | °C               |                                                                                                                       |

| Thermal Shutdown Hysteresis           | $\Delta T_{SD}$                  | —    | 10   | _    | °C               |                                                                                                                       |

| Output Noise                          | eN                               | _    | 800  | _    | nV/√Hz           | f = 10 kHz                                                                                                            |

| SHDN Input High Threshold             | V <sub>IH</sub>                  | 45   | _    | _    | %V <sub>IN</sub> | V <sub>IN</sub> = 2.7V to 6.0V                                                                                        |

| SHDN Input Low Threshold              | V <sub>IL</sub>                  | _    | _    | 15   | %V <sub>IN</sub> | V <sub>IN</sub> = 2.7V to 6.0V                                                                                        |

Note 1: The minimum  $V_{\text{IN}}$  has to meet two conditions:  $V_{\text{IN}} \geq 2.7 V$  and  $V_{\text{IN}} \geq (V_{\text{R}}$  + 2.5%) +  $V_{\text{DROPOUT}}.$

$V_R$  is the regulator voltage setting. For example:  $V_R$  = 1.8V, 2.7V, 2.8V, 3.0V. 2:

......

. ...

$$TCV_{OUT} = \frac{(V_{OUTMAX} - V_{OUTMIN}) \times 10^{\circ}}{V_{OUT} \times \Delta T}$$

- 4: Regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is tested over a load range from 0.1 mA to the maximum specified output current. Changes in output voltage due to heating effects are covered by the thermal regulation specification.

- 5: Dropout voltage is defined as the input-to-output differential at which the output voltage drops 2% below its nominal value at a 1V differential.

- 6: Thermal regulation is defined as the change in output voltage at a time T after a change in power dissipation is applied, excluding load or line regulation effects. Specifications are for a current pulse equal to ILMAX at VIN = 6V for t = 10 msec.

- 7: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction-to-air (i.e.,  $T_A$ ,  $T_J$ ,  $\theta_{JA}$ ). Exceeding the maximum allowable power dissipation causes the device to initiate thermal shutdown. Please see Section 5.1 "Thermal Shutdown", for more details.

- Output current is limited to 120 mA (typ) when V<sub>OUT</sub> is less than 0.5V due to a load fault or short-circuit condition. 8:

#### **TEMPERATURE CHARACTERISTICS**

| Parameters                   | Sym.            | Min. | Тур. | Max. | Units | Conditions                 |

|------------------------------|-----------------|------|------|------|-------|----------------------------|

| Temperature Ranges           |                 |      |      |      |       |                            |

| Specified Temperature Range  | T <sub>A</sub>  | -40  | —    | +125 | °C    | Extended Temperature parts |

| Operating Temperature Range  | T <sub>A</sub>  | -40  | —    | +125 | °C    |                            |

| Storage Temperature Range    | T <sub>A</sub>  | -65  | —    | +150 | °C    |                            |

| Thermal Package Resistances3 |                 |      |      |      |       |                            |

| Thermal Resistance, 5L-SOT23 | $\theta_{JA}$   |      | 255  | —    | °C/W  |                            |

| Thermal Resistance, 5L-SC-70 | θ <sub>JA</sub> |      | 450  | —    | °C/W  |                            |

## 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

| TABLE 3-1: | PIN FUNCTION TABLE |

|------------|--------------------|

|------------|--------------------|

| Pin No.<br>5-Pin SC-70 | Pin No.<br>5-Pin SOT-23<br>5-Pin SC-70R | Symbol           | Description              |

|------------------------|-----------------------------------------|------------------|--------------------------|

| 1                      | 3                                       | SHDN             | Shutdown Control Input   |

| 2                      | 4                                       | NC               | No Connect               |

| 3                      | 2                                       | GND              | Ground Terminal          |

| 4                      | 5                                       | V <sub>OUT</sub> | Regulated Voltage Output |

| 5                      | 1                                       | V <sub>IN</sub>  | Unregulated Supply Input |

## 3.1 Shutdown Control Input (SHDN)

The regulator is fully enabled when a logic-high is applied to SHDN. The regulator enters shutdown when a logic-low is applied to this input. During shutdown, the output voltage falls to zero and the supply current is reduced to 0.05  $\mu A$  (typ.)

## 3.2 Ground Terminal

For best performance, it is recommended that the ground pin be tied to a ground plane.

## 3.3 Regulated Voltage Output (V<sub>OUT</sub>)

Bypass the regulated voltage output to GND with a minimum capacitance of  $1 \,\mu$ F. A ceramic bypass capacitor is recommended for best performance.

## 3.4 Unregulated Supply Input (V<sub>IN</sub>)

The minimum  $V_{IN}$  has to meet two conditions in order to ensure that the output maintains regulation:  $V_{IN} \ge 2.7V$  and  $V_{IN} \ge [(V_R + 2.5\%) + V_{DROPOUT}]$ . The maximum  $V_{IN}$  should be less than or equal to 6V. Power dissipation may limit  $V_{IN}$  to a lower potential in order to maintain a junction temperature below 125°C. Refer to Section 5.0 "Thermal Considerations", for determining junction temperature.

It is recommended that  $\mathsf{V}_{\mathsf{IN}}$  be bypassed to GND with a ceramic capacitor.

## 4.0 DETAILED DESCRIPTION

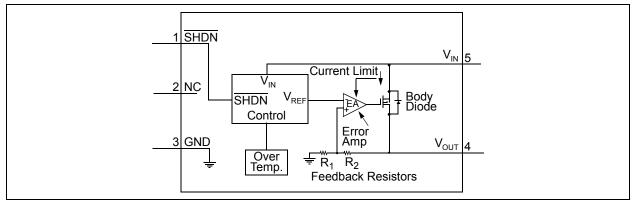

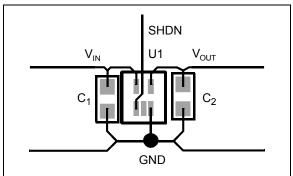

The TC1017 is a precision, fixed-output, linear voltage regulator. The internal linear pass element is a P-channel MOSFET. As with all P-channel CMOS LDOs, there is a body drain diode with the cathode connected to  $V_{\rm IN}$  and the anode connected to  $V_{\rm OUT}$  (Figure 4-1).

As is shown in Figure 4-1, the output voltage of the LDO is sensed and divided down internally to reduce external component count. The internal error amplifier has a fixed bandgap reference on the inverting input and the sensed output voltage on the non-inverting input. The error amplifier output will pull the gate voltage down until the inputs of the error amplifier are equal to regulate the output voltage.

Output overload protection is implemented by sensing the current in the P-channel MOSFET. During a shorted or faulted load condition in which the output voltage falls to less than 0.5V, the output current is limited to a typical value of 120 mA. The current-limit protection helps prevent excessive current from damaging the Printed Circuit Board (PCB).

An internal thermal sensing device is used to monitor the junction temperature of the LDO. When the sensed temperature is over the set threshold of 160°C (typical), the P-channel MOSFET is turned off. When the P-channel is off, the power dissipation internal to the device is almost zero. The device cools until the junction temperature is approximately 150°C and the P-channel is turned on. If the internal power dissipation is still high enough for the junction to rise to 160°C, it will again shut off and cool. The maximum operating junction temperature of the device is 125°C. Steady-state operation at or near the 160°C overtemperature point can lead to permanent damage of the device.

The output voltage  $V_{OUT}$  remains stable over the entire input operating voltage range (2.7V to 6.0V) and the entire load range (0 mA to 150 mA). The output voltage is sensed through an internal resistor divider and compared with a precision internal voltage reference. Several fixed-output voltages are available by changing the value of the internal resistor divider.

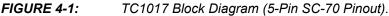

Figure 4-2 shows a typical application circuit. The regulator is enabled any time the shutdown input pin is at or above  $V_{IH}$ . It is shut down (disabled) any time the shutdown input pin is below  $V_{IL}$ . For applications where the SHDN feature is not used, tie the SHDN pin directly to the input supply voltage source. While in shutdown, the supply current decreases to 0.006  $\mu$ A (typical) and the P-channel MOSFET is turned off.

As shown in Figure 4-2, batteries have internal source impedance. An input capacitor is used to lower the input impedance of the LDO. In some applications, high input impedance can cause the LDO to become unstable. Adding more input capacitance can compensate for this.

## 4.1 Input Capacitor

Low input source impedance is necessary for the LDO to operate properly. When operating from batteries, or in applications with long lead length (> 10") between the input source and the LDO, some input capacitance is required. A minimum of 0.1  $\mu$ F is recommended for most applications and the capacitor should be placed as close to the input of the LDO as is practical. Larger input capacitors will help reduce the input impedance and further reduce any high-frequency noise on the input and output of the LDO.

## 4.2 Output Capacitor

A minimum output capacitance of 1  $\mu$ F for the TC1017 is required for stability. The Equivalent Series Resistance (ESR) requirements on the output capacitor are between 0 and 2 ohms. The output capacitor should be located as close to the LDO output as is practical. Ceramic materials X7R and X5R have low temperature coefficients and are well within the acceptable ESR range required. A typical 1  $\mu$ F X5R 0805 capacitor has an ESR of 50 milli-ohms. Larger output capacitors can be used with the TC1017 to improve dynamic behavior and input ripple-rejection performance.

Ceramic, aluminum electrolytic or tantalum capacitor types can be used. Since many aluminum electrolytic capacitors freeze at approximately –30°C, ceramic or solid tantalums are recommended for applications operating below –25°C. When operating from sources other than batteries, supply-noise rejection and transient response can be improved by increasing the value of the input and output capacitors and employing passive filtering techniques.

## 4.3 Turn-On Response

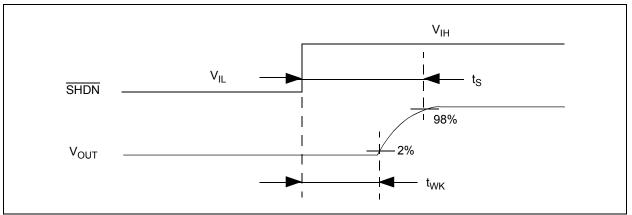

The turn-on response is defined as two separate response categories, wake-up time  $(t_{WK})$  and settling time  $(t_{S}).$

The TC1017 has a fast wake-up time (10  $\mu$ sec, typical) when released from shutdown. See Figure 4-3 for the wake-up time designated as t<sub>WK</sub>. The wake-up time is defined as the time it takes for the output to rise to 2% of the V<sub>OUT</sub> value after being released from shutdown.

The total turn-on response is defined as the settling time ( $t_s$ ) (see Figure 4-3). Settling time (inclusive with  $t_{WK}$ ) is defined as the condition when the output is within 98% of its fully-enabled value (32 µsec, typical) when released from shutdown. The settling time of the output voltage is dependent on load conditions and output capacitance on V<sub>OUT</sub> (RC response).

The table below demonstrates the typical turn-on response timing for different input voltage power-up frequencies:  $V_{OUT}$  = 2.85V,  $V_{IN}$  = 5.0V,  $I_{OUT}$  = 60 mA and  $C_{OUT}$  = 1 µF.

| Frequency | Typical (t <sub>WK</sub> ) | Typical (t <sub>S</sub> ) |

|-----------|----------------------------|---------------------------|

| 1000 Hz   | 5.3 µsec                   | 14 µsec                   |

| 500 Hz    | 5.9 µsec                   | 16 µsec                   |

| 100 Hz    | 9.8 µsec                   | 32 µsec                   |

| 50 Hz     | 14.5 µsec                  | 52 µsec                   |

| 10 Hz     | 17.2 µsec                  | 77 µsec                   |

FIGURE 4-3:

Wake-Up Time from Shutdown.

## 5.0 THERMAL CONSIDERATIONS

## 5.1 Thermal Shutdown

Integrated thermal protection circuitry shuts the regulator off when the die temperature exceeds approximately 160°C. The regulator remains off until the die temperature drops to approximately 150°C.

## 5.2 Power Dissipation: SC-70

The TC1017 is available in the SC-70 package. The thermal resistance for the SC-70 package is approximately 450°C/W when the copper area used in the PCB layout is similar to the JEDEC J51-7 high thermal conductivity standard or semi-G42-88 standard. For applications with a larger or thicker copper area, the thermal resistance can be lowered. See AN792, "A Method to Determine How Much Power a SOT-23 Can Dissipate in an Application" (DS00792), for a method to determine the thermal resistance for a particular application.

The TC1017 power dissipation capability is dependant upon several variables: input voltage, output voltage, load current, ambient temperature and maximum junction temperature. The absolute maximum steadystate junction temperature is rated at +125°C. The power dissipation within the device is equal to:

#### EQUATION 5-1:

$$P_D = (V_{IN} - V_{OUT}) \times I_{LOAD} + V_{IN} \times I_{GND}$$

The V<sub>IN</sub> x I<sub>GND</sub> term is typically very small when compared to the (V<sub>IN</sub>–V<sub>OUT</sub>) x I<sub>LOAD</sub> term, simplifying the power dissipation within the LDO to be:

#### EQUATION 5-2:

$$P_D = (V_{IN} - V_{OUT}) \times I_{LOAD}$$

To determine the maximum power dissipation capability, the following equation is used:

**EQUATION 5-3:**

$$P_{DMAX} = \frac{(T_{J\_MAX} - T_{A\_MAX})}{R \theta_{JA}}$$

Where:

$$T_{J\_MAX} = \text{the maximum junction} \text{temperature allowed}$$

$$T_{A\_MAX} = \text{the maximum ambient} \text{temperature}$$

$$R \theta_{JA} = \text{the thermal resistance from} \text{junction to air}$$

Given the following example:

$$\begin{array}{rcl} V_{\text{IN}} &=& 3.0 \text{V to } 4.1 \text{V} \\ V_{\text{OUT}} &=& 2.85 \text{V} \pm 2.5 \% \\ I_{\text{LOAD}} &=& 120 \text{ mA (output current)} \\ T_{\text{A}} &=& 55^{\circ} \text{C (max. desired ambient)} \end{array}$$

Find:

1. Internal power dissipation:

$$P_{DMAX} = (V_{IN\_MAX} - V_{OUT\_MIN}) \times I_{LOAD}$$

= (4.1V - 2.85 × (0.975)) × 120mA

= 158.5mW

2. Maximum allowable ambient temperature:

$$T_{A\_MAX} = T_{J\_MAX} - P_{DMAX} \times R\theta_{JA}$$

= (125 °C - 158.5 mW × 450 °C/W)

= (125 °C - 71 °C)

= 54 °C

3. Maximum allowable power dissipation at desired ambient:

$$P_D = \frac{T_{J\_MAX} - T_A}{R\theta_{JA}}$$

$$= \frac{125 \,^{\circ}\text{C} - 55 \,^{\circ}\text{C}}{450 \,^{\circ}\text{C}/W}$$

$$= 155 mW$$

In this example, the TC1017 dissipates approximately 158.5 mW and the junction temperature is raised 71°C over the ambient. The absolute maximum power dissipation is 155 mW when given a maximum ambient temperature of  $55^{\circ}$ C.

Input voltage, output voltage or load current limits can also be determined by substituting known values in the power dissipation equations.

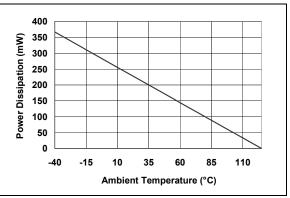

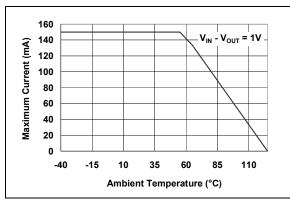

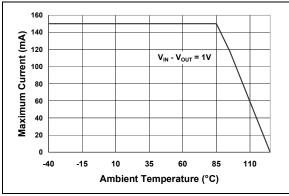

Figure 5-1 and Figure 5-2 depict typical maximum power dissipation versus ambient temperature, as well as typical maximum current versus ambient temperature, with a 1V input voltage to output voltage differential, respectively.

FIGURE 5-1: Power Dissipation vs. Ambient Temperature (SC-70 package).

FIGURE 5-2: Maximum Current vs. Ambient Temperature (SC-70 package).

## 5.3 Power Dissipation: SOT-23

The TC1017 is also available in a SOT-23 package for improved thermal performance. The thermal resistance for the SOT-23 package is approximately 255°C/W when the copper area used in the printed circuit board layout is similar to the JEDEC J51-7 low thermal conductivity standard or semi-G42-88 standard. For applications with a larger or thicker copper area, the thermal resistance can be lowered. See AN792, "A *Method to Determine How Much Power a SOT-23 Can Dissipate in an Application*" (DS00792), for a method to determine the thermal resistance for a particular application.

The TC1017 power dissipation capability is dependent upon several variables: input voltage, output voltage, load current, ambient temperature and maximum junction temperature. The absolute maximum steadystate junction temperature is rated at +125°C. The power dissipation within the device is equal to:

#### **EQUATION 5-4:**

$$P_D = (V_{IN} - V_{OUT}) \times I_{LOAD} + V_{IN} \times I_{GND}$$

The V<sub>IN</sub> x I<sub>GND</sub> term is typically very small when compared to the (V<sub>IN</sub>-V<sub>OUT</sub>) x I<sub>LOAD</sub> term, simplifying the power dissipation within the LDO to be:

#### **EQUATION 5-5:**

$$P_D = (V_{IN} - V_{OUT}) \times I_{LOAD}$$

To determine the maximum power dissipation capability, the following equation is used:

#### **EQUATION 5-6:**

$$P_{DMAX} = \frac{(T_{J\_MAX} - T_{A\_MAX})}{R\theta_{JA}}$$

Where:

$T_{J\_MAX}$  = the maximum junction temperature allowed  $T_{A\_MAX}$  = the maximum ambient temperature  $R\theta_{JA}$  = the thermal resistance from junction to air

Given the following example:

$$V_{IN} = 3.0V \text{ to } 4.1V$$

$$V_{OUT} = 2.85V \pm 2.5\%$$

$$I_{LOAD} = 120 \text{ mA (output current)}$$

$$T_{A} = +85^{\circ}\text{C (max. desired ambient)}$$

Find:

2.

1. Internal power dissipation:

$$P_{DMAX} = (V_{IN\_MAX} - V_{OUT\_MIN}) \times I_{LOAD}$$

= (4.1V - 2.85 × (0.975)) × 120mA

= 158.5mW

Maximum allowable ambient temperature:

$$T_{A\_MAX} = T_{J\_MAX} - P_{DMAX} \times R \theta_{JA}$$

= (125 °C - 158.5m W × 255 °C/W)

= (125 °C - 40.5 °C)

= 84.5 °C

Maximum allowable power dissipation at desired ambient:

$$P_D = \frac{T_{J\_MAX} - T_A}{R\theta_{JA}}$$

$$= \frac{125 \,^{\circ}\text{C} - 85 \,^{\circ}\text{C}}{255 \,^{\circ}\text{C}/W}$$

$$= 157 mW$$

In this example, the TC1017 dissipates approximately 158.5 mW and the junction temperature is raised  $40.5^{\circ}$ C over the ambient. The absolute maximum power dissipation is 157 mW when given a maximum ambient temperature of +85°C.

Input voltage, output voltage or load current limits can also be determined by substituting known values in the power dissipation equations.

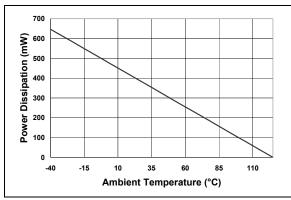

Figure 5-3 and Figure 5-4 depict typical maximum power dissipation versus ambient temperature, as well as typical maximum current versus ambient temperature with a 1V input voltage to output voltage differential, respectively.

FIGURE 5-3: Power Dissipation vs. Ambient Temperature (SOT-23 Package).

FIGURE 5-4: Maximum Current vs. Ambient Temperature (SOT-23 Package).

## 5.4 Layout Considerations

The primary path for heat conduction out of the SC-70/ SOT-23 package is through the package leads. Using heavy, wide traces at the pads of the device will facilitate the removal of the heat within the package, thus lowering the thermal resistance  $R\theta_{JA}$ . By lowering the thermal resistance, the maximum internal power dissipation capability of the package is increased.

FIGURE 5-5: Layout.

SC-70 Package Suggested