# LAN8700/LAN8700i

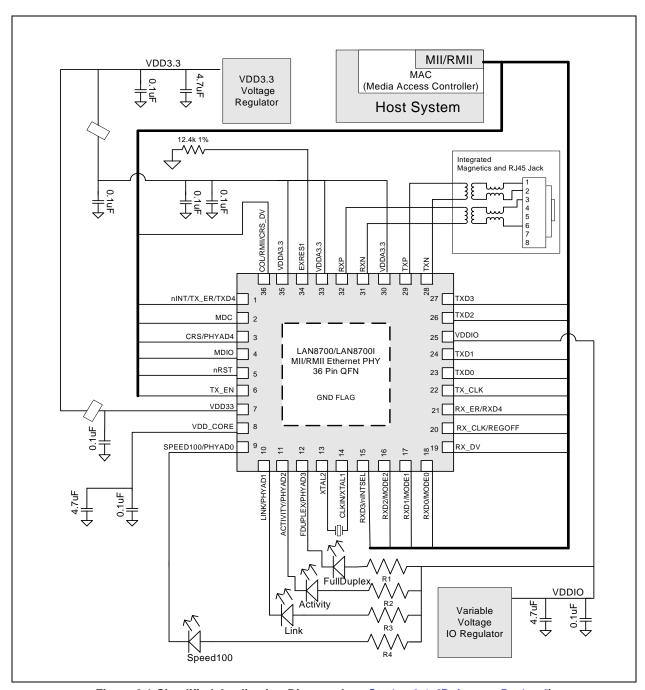

# ±15kV ESD Protected MII/RMII 10/100 Ethernet Transceiver with HP Auto-MDIX Support and flexPWR<sup>®</sup> Technology in a Small Footprint

#### PRODUCT FEATURES

**Datasheet**

- Single-Chip Ethernet Physical Layer Transceiver (PHY)

- ESD Protection levels of ±8kV HBM without external protection devices

- ESD protection levels of EN/IEC61000-4-2, ±8kV contact mode, and ±15kV for air discharge mode per independent test facility

- Comprehensive flexPWR<sup>®</sup> Technology

Flexible Power Management Architecture

- LVCMOS Variable I/O voltage range: +1.6V to +3.6V

- Integrated 3.3V to 1.8V regulator for optional single supply operation.

- Regulator can be disabled if 1.8V system supply is available.

- Performs HP Auto-MDIX in accordance with IEEE 802.3ab specification

- Cable length greater than 150 meters

- Automatic Polarity Correction

- Latch-Up Performance Exceeds 150mA per EIA/JESD 78, Class II

- Energy Detect power-down mode

- Low Current consumption power down mode

- Low operating current consumption:

- 39mA typical in 10BASE-T and

- 79mA typical in 100BASE-TX mode

- Supports Auto-negotiation and Parallel Detection

- Supports the Media Independent Interface (MII) and Reduced Media Independent Interface (RMII)

- Compliant with IEEE 802.3-2005 standards

MII Pins tolerant to 3.6V

- IEEE 802.3-2005 compliant register functions

- Integrated DSP with Adaptive Equalizer

- Baseline Wander (BLW) Correction

- Vendor Specific register functions

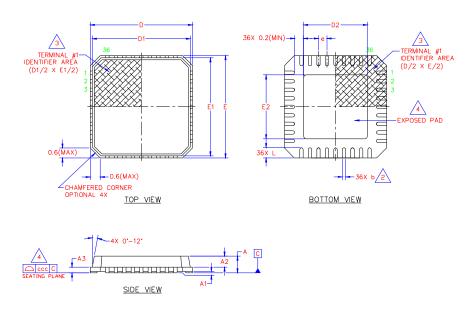

- Low profile 36-pin QFN lead-free RoHS compliant package (6 x 6 x 0.9mm height)

- 4 LED status indicators

- Commercial Operating Temperature 0° C to 70° C

- Industrial Operating Temperature -40° C to 85° C version available (LAN8700i)

#### **Applications**

- Set Top Boxes

- Network Printers and Servers

- LAN on Motherboard

- 10/100 PCMCIA/CardBus Applications

- Embedded Telecom Applications

- Video Record/Playback Systems

- Cable Modems/Routers

- DSL Modems/Routers

- Digital Video Recorders

- Personal Video Recorders

- IP and Video Phones

- Wireless Access Points

- Digital Televisions

- Digital Media Adaptors/Servers

- POS Terminals

- Automotive Networking

- Gaming Consoles

- Security Systems

- POE Applications

- Access Control

#### **Order Numbers:**

LAN8700C-AEZG for 36-pin, QFN lead-free RoHS compliant package

LAN8700iC-AEZG for (Industrial Temp) 36-pin, QFN lead-free RoHS compliant package

4900 pcs per tray

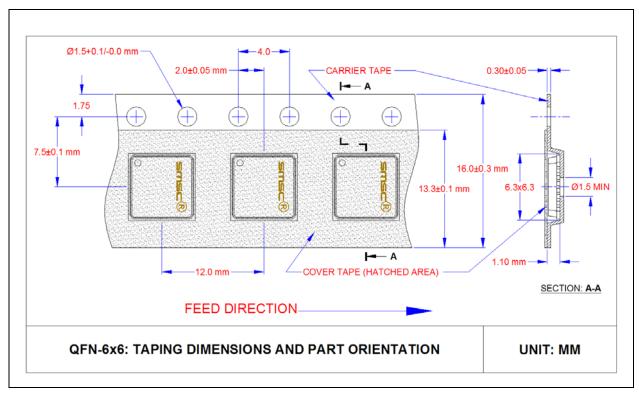

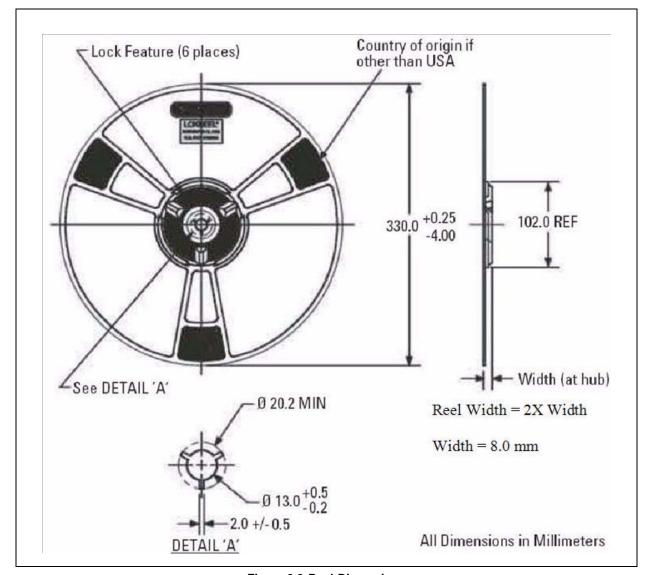

LAN8700C-AEZG-TR for 36-pin, QFN lead-free RoHS compliant package (tape and reel) 3000 pcs per reel

This product meets the halogen maximum concentration values per IEC61249-2-21 For RoHS compliance and environmental information, please visit www.smsc.com/rohs

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000 or 1 (800) 443-SEMI

Copyright © 2011 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

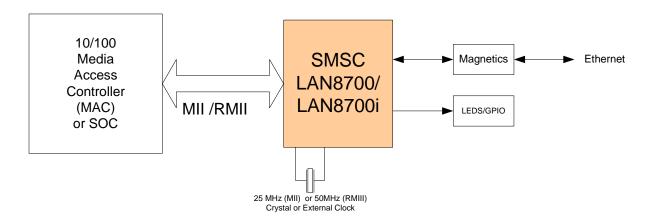

| <b>Chap</b> 1.1 |            | General Descriptionural Overview                                  |    |

|-----------------|------------|-------------------------------------------------------------------|----|

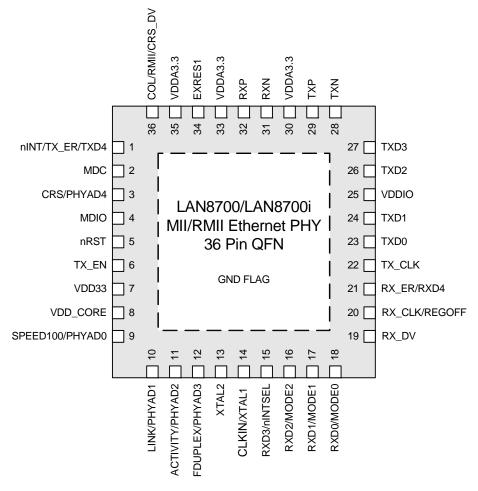

| Chan            | tor 2 P    | in Configuration                                                  | 10 |

| 2.1             |            | Pin-out Diagram and Signal Table                                  |    |

| <u>Z. I</u>     | rackage    | Pili-out Diagram and Signal Table                                 | 10 |

| _               |            | Pin Description                                                   |    |

| 3.1             | I/O Signa  | als                                                               | 12 |

| Chap            | ter 4 A    | Architecture Details                                              | 19 |

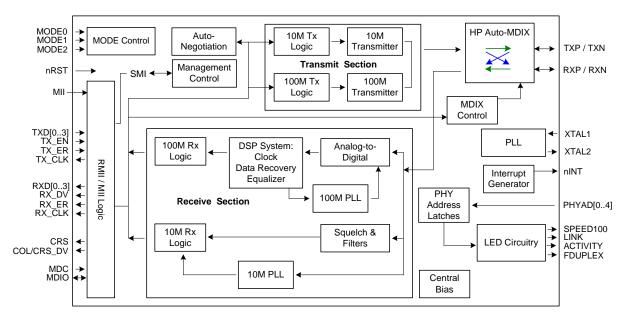

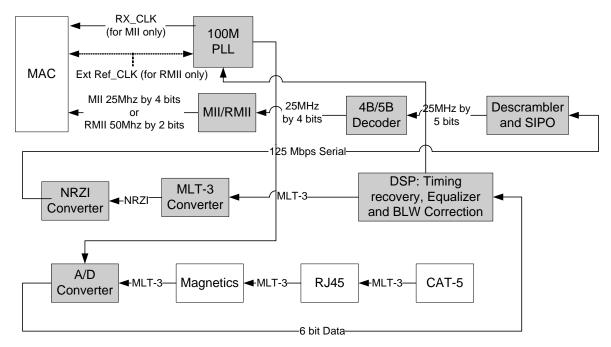

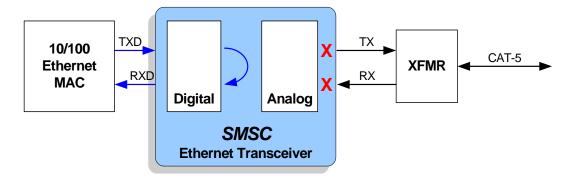

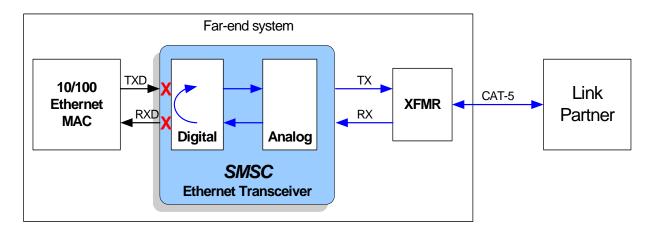

| 4.1             | Top Leve   | el Functional Architecture                                        | 19 |

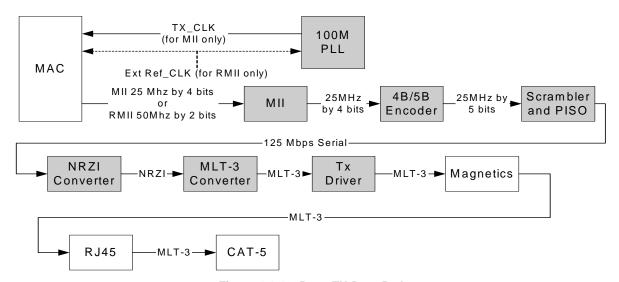

| 4.2             | 100Base    | -TX Transmit                                                      | 19 |

|                 | 4.2.1      | 100M Transmit Data Across the MII/RMII Interface                  | 19 |

|                 | 4.2.2      | 4B/5B Encoding                                                    | 19 |

|                 | 4.2.3      | Scrambling                                                        |    |

|                 | 4.2.4      | NRZI and MLT3 Encoding                                            | 21 |

|                 | 4.2.5      | 100M Transmit Driver                                              | 21 |

|                 | 4.2.6      | 100M Phase Lock Loop (PLL)                                        | 22 |

| 4.3             | 100Base    | -TX Receive                                                       | 22 |

|                 | 4.3.1      | 100M Receive Input                                                | 22 |

|                 | 4.3.2      | Equalizer, Baseline Wander Correction and Clock and Data Recovery | 22 |

|                 | 4.3.3      | NRZI and MLT-3 Decoding                                           | 23 |

|                 | 4.3.4      | Descrambling                                                      | 23 |

|                 | 4.3.5      | Alignment.                                                        | 23 |

|                 | 4.3.6      | 5B/4B Decoding                                                    | 23 |

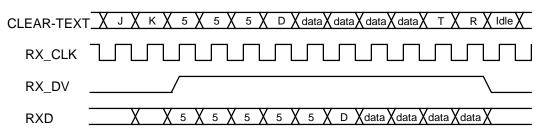

|                 | 4.3.7      | Receive Data Valid Signal                                         | 23 |

|                 | 4.3.8      | Receiver Errors                                                   | 24 |

|                 | 4.3.9      | 100M Receive Data Across the MII/RMII Interface                   | 24 |

| 4.4             | 10Base-    | T Transmit                                                        |    |

|                 | 4.4.1      | 10M Transmit Data Across the MII/RMII Interface                   | 24 |

|                 | 4.4.2      | Manchester Encoding                                               | 25 |

|                 | 4.4.3      | 10M Transmit Drivers                                              | 25 |

| 4.5             | 10Base-    | T Receive                                                         | 25 |

|                 | 4.5.1      | 10M Receive Input and Squelch                                     | 25 |

|                 | 4.5.2      | Manchester Decoding                                               | 25 |

|                 | 4.5.3      | 10M Receive Data Across the MII/RMII Interface                    | 26 |

|                 | 4.5.4      | Jabber Detection                                                  | 26 |

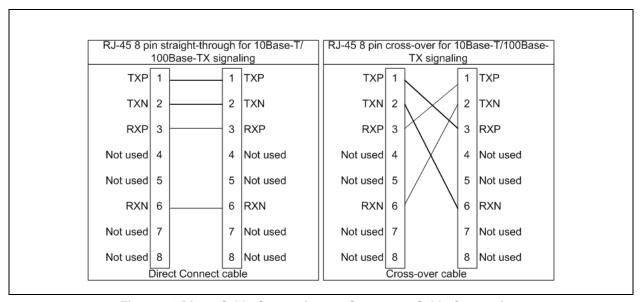

| 4.6             | MAC Inte   | erface                                                            | 26 |

|                 | 4.6.1      | MII                                                               | 26 |

|                 | 4.6.2      | RMII                                                              | 27 |

|                 | 4.6.3      | MII vs. RMII Configuration                                        | 28 |

| 4.7             | Auto-neg   | otiation                                                          | 29 |

|                 | 4.7.1      | Parallel Detection                                                | 30 |

|                 | 4.7.2      | Re-starting Auto-negotiation                                      | 30 |

|                 | 4.7.3      | Disabling Auto-negotiation                                        | 30 |

|                 | 4.7.4      | Half vs. Full Duplex                                              |    |

| 4.8             | HP Auto-   | ·                                                                 |    |

| 4.9             | Internal - | +1.8V Regulator Disable                                           |    |

|                 | 4.9.1      | Disable the Internal +1.8V Regulator                              |    |

|                 | 4.9.2      | Enable the Internal +1.8V Regulator                               |    |

| 4.10                    |                | (_ER/TXD4 Strapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

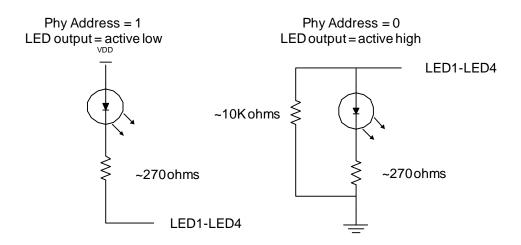

| 4.11<br>4.12            |                | dress Strapping and LED Output Polarity Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

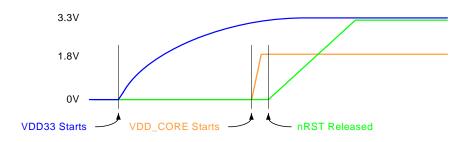

| 4.12                    | 4.12.1         | Voltage I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         | 4.12.1         | I/O Voltage Stability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.13                    |                | anagement Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

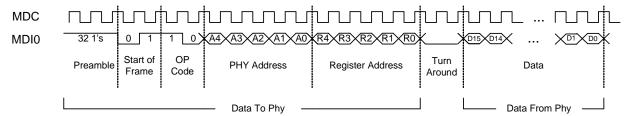

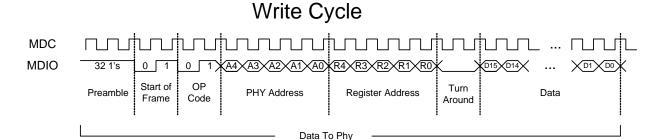

| 7.10                    | 4.13.1         | Serial Management Interface (SMI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                         | 1.10.1         | Contai managomone interiaco (Cini).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Chap                    | oter 5         | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.1                     |                | gister Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.2                     |                | gister Format41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3                     |                | t Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                         | 5.3.1          | Primary Interrupt System49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                         | 5.3.2          | Alternate Interrupt System50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.4                     |                | neous Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | 5.4.1          | Carrier Sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                         | 5.4.2          | Collision Detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                         | 5.4.3          | Isolate Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                         | 5.4.4<br>5.4.5 | Link Integrity Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                         | 5.4.5<br>5.4.6 | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                         | 5.4.7          | LED Description. 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

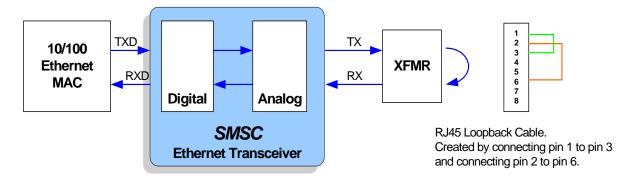

|                         | 5.4.8          | Loopback Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

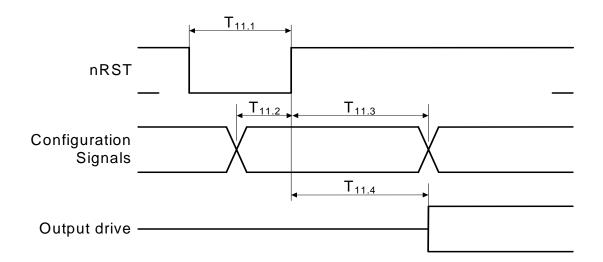

|                         | 5.4.9          | Configuration Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                         | 00             | - Comiguration Olympia Transfer to the Company of t |

| Char                    | oter 6         | AC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

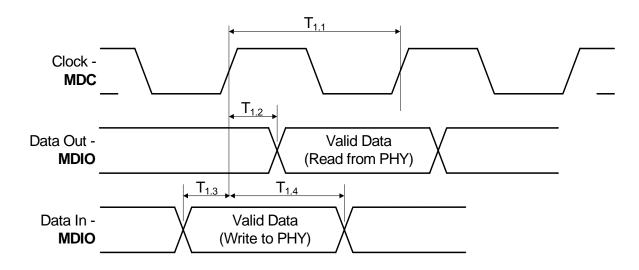

| 6.1                     |                | lanagement Interface (SMI) Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

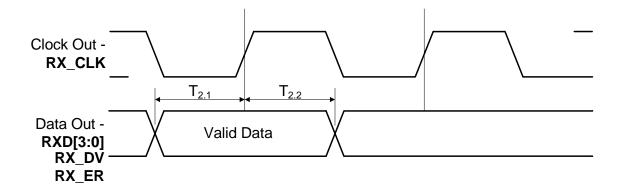

| 6.2                     |                | 00Base-TX/RX Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

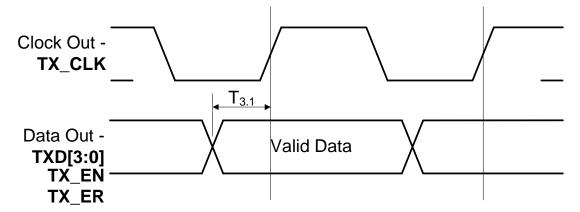

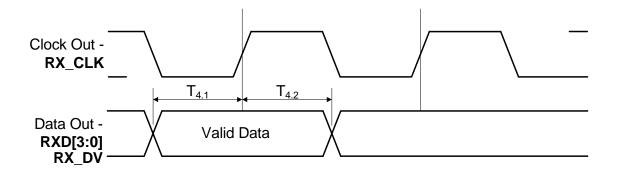

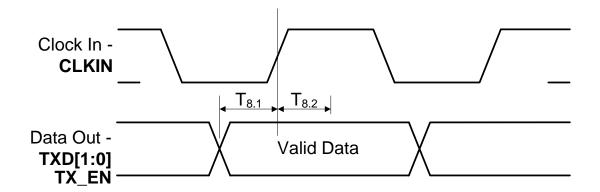

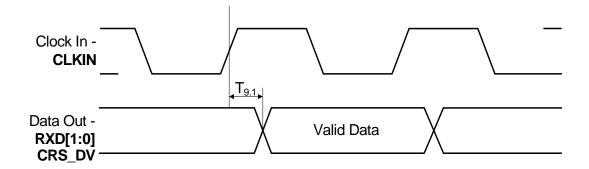

|                         | 6.2.1          | MII 100Base-T TX/RX Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

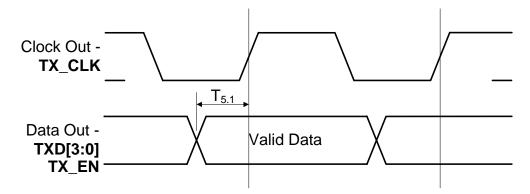

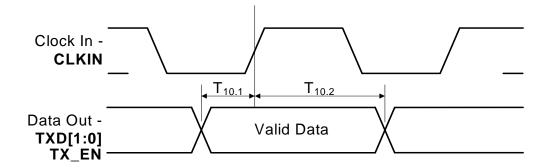

|                         | 6.2.2          | MII 10Base-T TX/RX Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.3                     | RMII 10        | /100Base-TX/RX Timings62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                         | 6.3.1          | RMII 100Base-T TX/RX Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                         | 6.3.2          | RMII 10Base-T TX/RX Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

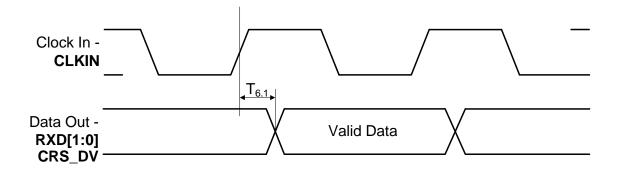

| 6.4                     |                | .KIN Timing66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |