# ICL88xx flyback design guide

## For high power factor flyback converter with constant voltage output

### About this document

### Scope and purpose

The ICL88xx family of single-stage power factor correction (PFC)/flyback controllers for constant voltage (CV) output is tailored to meet LED lighting regulatory requirements and satisfy LED lighting applications, including LED drivers with dim-to-off requirements.

This document is a design guide to using ICL88xx as a single-stage PFC flyback converter at 43 W.

It has features such as low standby power consumption (**ICL8810** and **ICL8820**) and outstanding PFC and low total harmonic distortion (THD) at full load as well as at low load conditions.

The PWM jitter feature (ICL8820) allows for ease of EMI compliance, and reduces the size, count and cost of external components for emergency lighting application in DC operation.

The evaluation board regulates a CV output, and is intended to be used with a constant current (CC) converter for LED lighting applications.

The design guide takes the reader step by step through the design process of high power factor (HPF) flyback converters and explains each step using a 52 V/43 W converter as an example.

#### **Intended audience**

This design guide is intended for power supply design engineers and field application engineers.

### **Table of contents**

| Abou  | It this document                                                                   | 1  |

|-------|------------------------------------------------------------------------------------|----|

| Table | e of contents                                                                      | 1  |

| 1     | Introduction                                                                       | 3  |

| 1.1   | Pin configuration and description                                                  | 4  |

| 1.2   | Design process                                                                     | 5  |

| 2     | Design specifications                                                              | 6  |

| 2.1   | Specification of a 43 W PFC flyback reference design for LED lighting applications | 6  |

| 3     | PFC flyback converter design                                                       | 7  |

| 3.1   | Transformer design                                                                 |    |

| 3.2   | Flyback MOSFET and secondary main output diode selection                           | 17 |

| 3.3   | Output capacitor                                                                   | 21 |

| 3.4   | MOSFET snubber design                                                              | 22 |

| 3.5   | CS resistor and GD pin-related design                                              |    |

| 3.6   | VIN pin-related design                                                             |    |

| 3.7   | On-time adjustment                                                                 | 34 |

| 3.8   | V <sub>cc</sub> capacitance and output UVP design                                  | 37 |

| 4     | THD optimization                                                                   | 42 |

| 4.1   | Output OVP-related design                                                          | 44 |

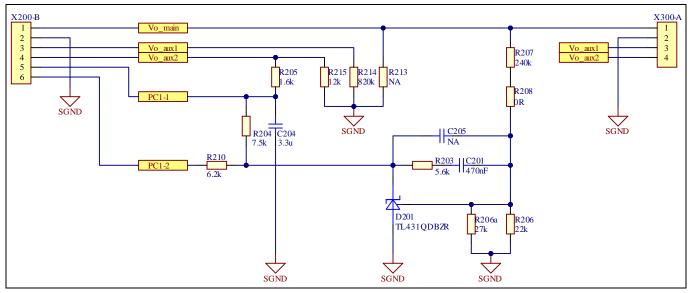

| 5     | Secondary-side regulation feedback circuit design                                  | 47 |

| 6     | PCB layout guide                                                                   | 53 |

| 7    | Tips and tricks              | 55 |

|------|------------------------------|----|

| 8    | Debugging guide              | 56 |

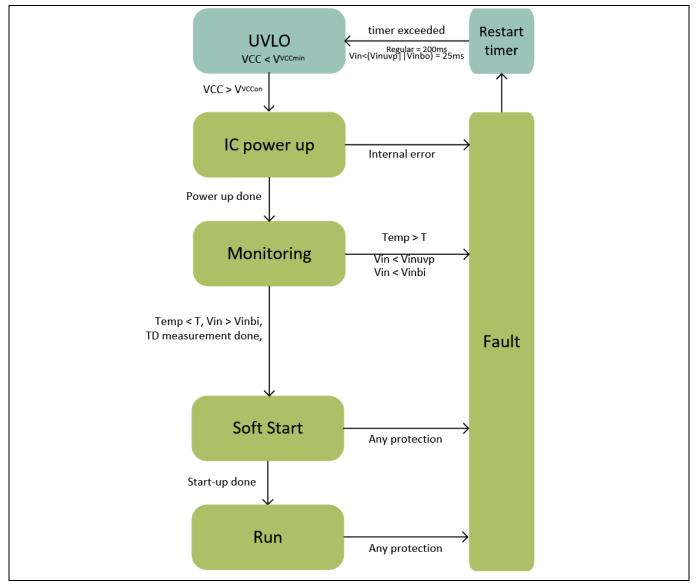

| 9    | ICL8800 operation flow chart | 57 |

| 10   | Protection features          |    |

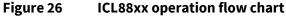

| 10.1 | Schematic                    | 59 |

| 11   | References                   | 62 |

| 12   | Revision history             | 63 |

### ICL88xx flyback design guide For high power factor flyback converter with constant voltage output Introduction

## 1 Introduction

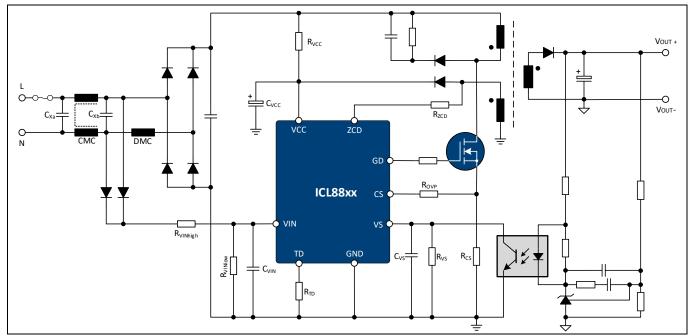

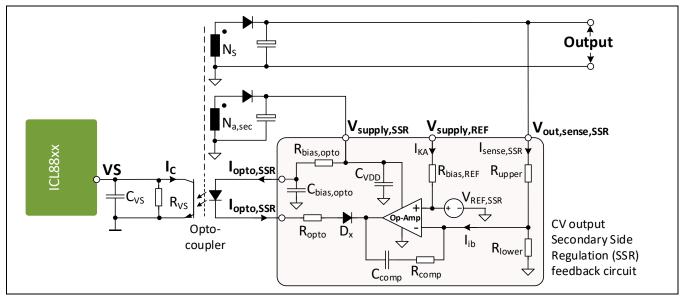

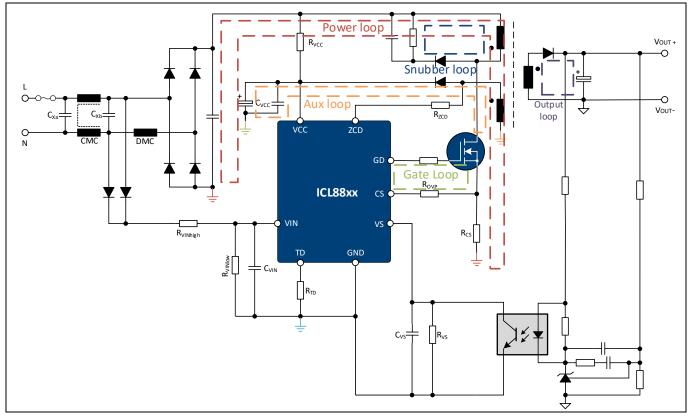

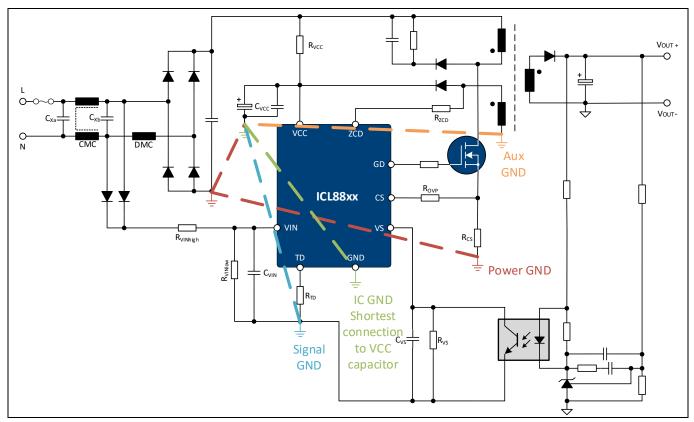

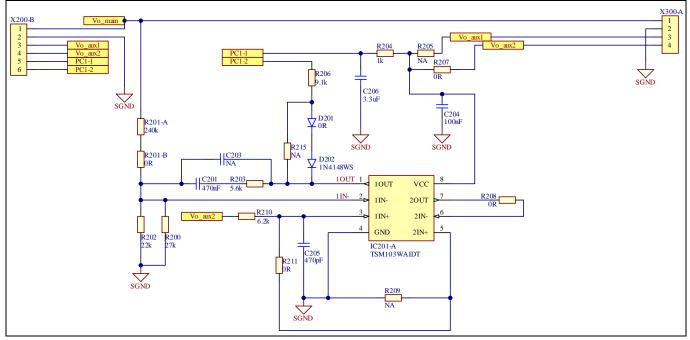

The ICL88xx family is optimized for secondary-side regulated (SSR) HPF flyback converters. The simplified schematic is shown in **Figure 1**.

The ICL88xx family can also be used in a primary-side regulated (PSR) configuration – please visit **Infineon** to find more information on this topic.

Figure 1 ICL88xx flyback converter – simplified circuitry with secondary-side regulated CV output

ICL88xx is a quasi-resonant (QR) controller operating in a critical conduction mode (CrCM) at full load and minimum input voltage. The IC will try to stay in CrCM for as long as possible. QR control helps to minimize switching noise and increases efficiency by turning on the main power MOSFET at the lowest possible drain-source voltage during transformer demagnetization.

The IC regulates the CV output, according to its feedback (FB) pin current signal, which is controlled by the secondary-side regulation FB circuit via an optocoupler.

For LED lighting applications, the ICL88xx flyback CV output is usually converted to a CC output by a secondstage DC-DC converter, which is either a switching or linear regulator.

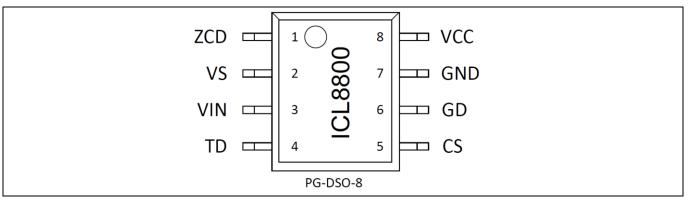

### **1.1** Pin configuration and description

The ICL88xx comes in a PG-DSO-8 package with eight pins. The main functions of each pin are shown in **Table 1** and **Figure 2**.

Figure 2 Pin-out of ICL88xx

#### Table 1Pin definitions and functions

| Name | Pin | Function                                                                                                                                                                                                                                                                                                                        |

|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZCD  | 1   | Zero crossing detection                                                                                                                                                                                                                                                                                                         |

|      |     | Connected to an auxiliary winding via a resistor to detect the zero crossing of the switching current. When the zero crossing is detected, the controller initiates a new switching cycle. The resistor from the ZCD pin to the auxiliary winding is used to set the maximum on-time and therefore tune the output power limit. |

| VS   | 2   | Voltage sense                                                                                                                                                                                                                                                                                                                   |

|      |     | Connected to the feedback circuit. The current drawn out of this pin determines the on-<br>time. A resistor $R_{vs}$ of 12k is mandatory to set the correct operation point.                                                                                                                                                    |

| VIN  | 3   | Input voltage detection                                                                                                                                                                                                                                                                                                         |

|      |     | Measure the AC or DC input voltage for power limitation, input overvoltage protection (OVP), brown-in (BI) and brown-out (BO).                                                                                                                                                                                                  |

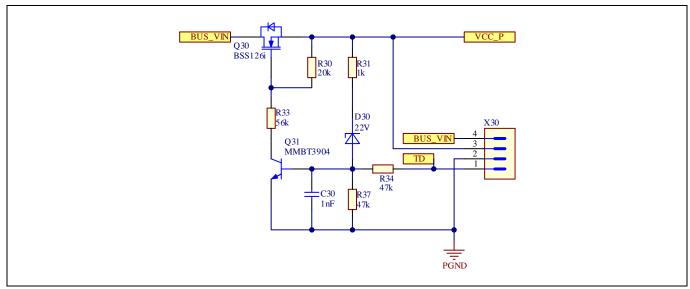

| TD   | 4   | THD correction                                                                                                                                                                                                                                                                                                                  |

|      |     | Sets the THD correction using a resistor to GND. The voltage on this pin can be used to control an external start-up circuit.                                                                                                                                                                                                   |

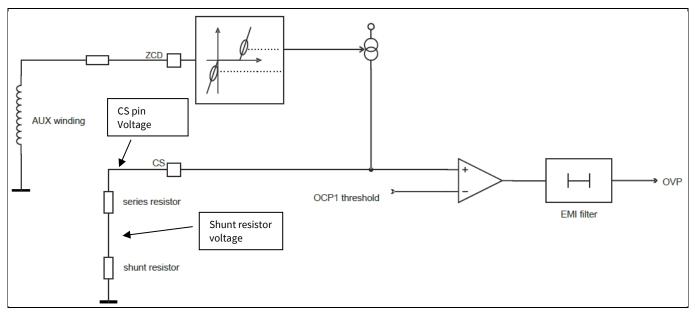

| CS   | 5   | MOSFET current sense and output voltage protection                                                                                                                                                                                                                                                                              |

|      |     | Primary-side overcurrent protection (OCP). A series resistance to the shunt resistor is used to tune a secondary OVP for the flyback topology.                                                                                                                                                                                  |

| GD   | 6   | Gate driver                                                                                                                                                                                                                                                                                                                     |

|      |     | PWM gate drive for the main power MOSFET.                                                                                                                                                                                                                                                                                       |

| GND  | 7   | Ground                                                                                                                                                                                                                                                                                                                          |

|      |     | Connected to ground, and represents the ground level of the IC for the supply voltage, gate driver and sense signals.                                                                                                                                                                                                           |

| VCC  | 8   | Power supply                                                                                                                                                                                                                                                                                                                    |

|      |     | Supplies the IC.                                                                                                                                                                                                                                                                                                                |

### ICL88xx flyback design guide For high power factor flyback converter with constant voltage output Introduction

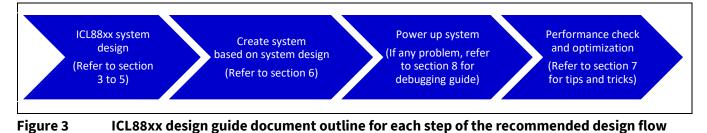

### 1.2 Design process

Figure 3 shows the design guide and design step sequence for the ICL88xx family of devices.

#### **Design specifications** 2

The ICL88xx PFC flyback converter design guide describes a step-by-step process for creating a 43.2 W CV converter. By following the step-by-step process, an engineer can develop a similar ICL88xx controlled converter with their own target specification.

#### Specification of a 43 W PFC flyback reference design for LED lighting 2.1 applications

A front-stage HPF flyback converter with CV output set-point V<sub>OUT-SET</sub> of 52 V at 0.8 A was selected as a design example. The design specifications are shown in **Table 2**.

| Specification                                               | Symbol                           | Value                   | Unit             |  |

|-------------------------------------------------------------|----------------------------------|-------------------------|------------------|--|

| Maximum AC input voltage                                    | V <sub>AC</sub>                  | 90 to 305               | V <sub>RMS</sub> |  |

| Normal operational AC input voltage                         | V <sub>AC,max</sub>              | 100 to 277              | V <sub>RMS</sub> |  |

| Normal operational AC input frequency                       | F <sub>line</sub>                | 47 ~ 63                 | Hz               |  |

| Secondary-side regulated CV output set-point                | V <sub>out</sub>                 | 52                      | V                |  |

| Steady-state output load current                            | <i>I</i> <sub>out</sub>          | 0~800                   | mA               |  |

| Steady-state full-load output power                         | Pout                             | 43                      | W                |  |

| Minimum efficiency at P <sub>out,full</sub>                 | $oldsymbol{\eta}_{min,at,P,out}$ | 91                      | %                |  |

| Target minimum switching frequency at P <sub>out,full</sub> | $f_{\rm sw,min,at,P,out}$        | 52                      | kHz              |  |

| Standard compliance                                         |                                  |                         |                  |  |

| Harmonics                                                   | -                                | EN 61000-3-2<br>class C | -                |  |

| EMI                                                         | -                                | EN55015                 | -                |  |

| Board dimensions                                            |                                  |                         |                  |  |

| Size                                                        | L×B                              | Main board:<br>171 × 27 | mm               |  |

| Size                                                        | L×B                              | PlugIN-TL:<br>36.5 × 27 | mm               |  |

POUT-FULL of 43.2 W is defined in this design example, to be able to supply a second-stage CC Note: converter which has minimum efficiency of 93 percent (or maximum 3.2 W loss) at full load, for a 40 W LED driver design.

The recommended f<sub>sw,min,at,P,out</sub> is between 50 kHz and 65 kHz. In general, a higher f<sub>sw,min,at,P,out</sub> value Note: would result in a smaller flyback transformer with lower efficiency, while a lower f<sub>sw,min,at,P,out</sub> value would result in a larger flyback transformer with higher efficiency.

## **3 PFC flyback converter design**

The primary function of a PFC converter is to shape and synchronize the AC-line current with the AC-line voltage. This enables maximization of real power drawn from the AC mains. In an ideal PFC circuit, the input current follows the input voltage as a pure resistor, without any input current harmonics.

On the other hand, the input current of the converter consists of the triangular currents through MOSFET Q1 (**Figure 1**), filtered and smoothed by the EMI filter consisting of  $C_{xa}$ ,  $C_{xb}$ , the differential-mode choke (DMC) and the leakage inductance of the common-mode choke (CMC).

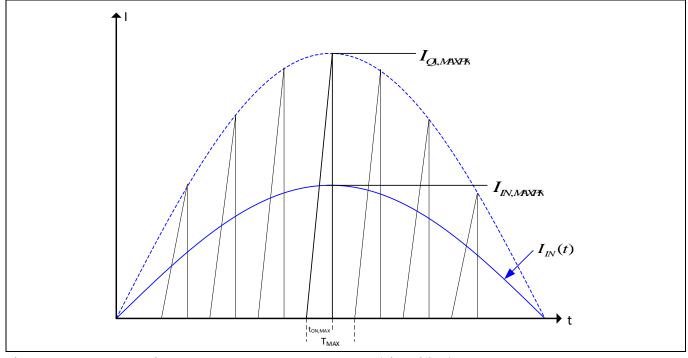

The relationship between the MOSFET and the input current is shown in Figure 4.

Figure 4 Flyback input current and MOSFET current (simplified)

As explained earlier, the converter operates in CrCM at the peak of the lowest line voltage, which is 90  $V_{RMS}$  in our example. The highest peak currents at the input as well as in the MOSFET occur under this condition and consequently, this point is essential for the design. Since real and apparent power are virtually identical, the expression for  $I_{IN,MAXPK}$  is simple:

$$I_{IN.MAXPK} = \frac{P_{OUT}}{\eta \cdot V_{IN,MINRMS}} \cdot \sqrt{2}$$

$$= \frac{43.2 W}{0.9 \cdot 90 V} \cdot \sqrt{2} = \underline{0.75 A}$$

$$(1)$$

### ICL88xx flyback design guide For high power factor flyback converter with constant voltage output PFC flyback converter design

This must, by definition, be identical to the maximum peak current of the MOSFET averaged over one switching cycle:

$$\frac{I_{Q1.MAXPK}}{2} \cdot \frac{t_{ON,MAX}}{T_{MAX}} = I_{IN.MAXPK}$$

Definitions:

- t<sub>on</sub> power MOSFET on-time

- T period of switching cycle  $(T = 1/f_{SW})$

Neither  $t_{ON}$  nor T are constant in this application but vary through the line half-wave. This behavior is needed in order to achieve good THD and PF. As the above equation implies, maximum on-time  $t_{ON,MAX}$  and maximum switching period  $T_{MAX}$  occur in the maximum of the lowest input voltage.

Now these two parameters,  $T_{MAX}$  and  $t_{ON,MAX}$ , have to be chosen. Because the maximum switching period equates to the minimum switching frequency, this parameter needs to be looked at first. A higher switching frequency can lead to a smaller transformer size on the one hand, but increases switching losses on the other.

### 3.1 Transformer design

To achieve both high efficiency and high power quality in quasi-resonant mode (QRM) with first valley switching (QRM1), the flyback transformer primary main winding to secondary main winding turns ratio, N, should be large. A larger turns ratios (N) will equate to a larger V<sub>DS</sub> MOSFET requirement. Design trade-offs between efficiency, size and cost are considered.

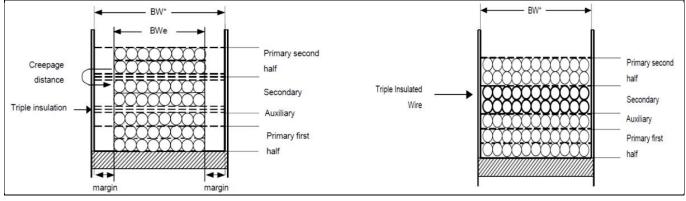

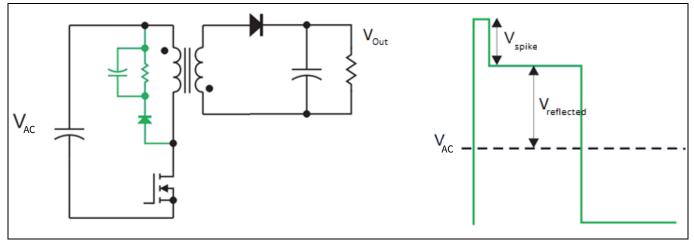

To reduce transformer leakage inductance for low MOSFET voltage spike *V*<sub>SPIKE-FET</sub>, transformer design with interleaved construction as shown in **Figure 5** is highly recommended. The voltage seen by the drain of the MOSFET is illustrated in **Figure 6**.

Transformer design with sandwich construction

Design Guide

(2)

## ICL88xx flyback design guide For high power factor flyback converter with constant voltage output

PFC flyback converter design

For this design, a minimum switching frequency at full load of 54 kHz was selected. In general, a frequency between 50 kHz and 70 kHz is recommended for wide input voltage range designs.

This minimum frequency range selection balances:

- Higher efficiency (lower *f*<sub>sw</sub>)

- Smaller transformer size (larger *f*<sub>sw</sub>)

- EMI compliance (second harmonic less than  $2 \times \min f_{sw}$ )

The second step in the design process is the winding ratio of the transformer (N). A duty-cycle ratio (DCR) has to be specified, and it is recommended to choose a value between 50 and 70 percent for wide-input AC-line designs, and a range of 50 to 60 percent for narrow AC-line designs. The increased on-time in the wide-range design allows the system to remain for longer in the first valley, as it is designed around the operating point with the lowest input voltage.

The system has to operate there on the boundary of DMC/CMC operation and has to be able to deliver full power. The duty cycle has a direct impact on the magnitude of the reflected voltage as well as the secondary-and primary-side current. This duty cycle has to be chosen with these values in mind.

QR flyback efficiency increases as the reflected voltage is increased. The larger reflected voltage causes the voltage across the drain-source of the main power MOSFET to ring lower after the transformer demagnetization, allowing for less voltage across the MOSFET during turn-on transitions. Larger reflected voltages develop greater voltage stress on the MOSFET, and this must be considered. The winding ratio N is a compromise between minimizing the switching losses and the capability of the selected MOSFET.

A large duty-cycle ratio develops a higher reflected voltage across the drain-source of the main MOSFET and reduces the magnitude of the primary MOSFET and transformer current. The benefit is a reduction in both conduction losses and EMI signature. By carefully choosing the duty cycle, it is possible to balance the MOSFET performance and cost.

Larger duty cycles also reduce the off-time of the converter, resulting in higher secondary-side peak currents.

A common first attempt to determine a proper transformer winding ratio (N) is to choose a MOSFET with a given  $V_{DS}$  rating, and then determine the duty cycle and other parameters given the MOSFET chosen.

Or, define a duty-cycle ratio and perform the calculations to see which MOSFET blocking voltage is required to keep this ratio. Both ways to find a proper winding ratio N are described in this document.

### ICL88xx flyback design guide For high power factor flyback converter with constant voltage output PFC flyback converter design

(3)

The winding ratio N (and in turn  $t_{ON,MAX}$ ) is a compromise between minimizing the switching losses and the maximum breakdown voltage  $V_{(BR)DSS}$  of the selected MOSFET.

This can be seen in the volt-second balance of the transformer that yields in an equation for t<sub>ON,MAX</sub>:

$N \cdot (V_{OUT} + V_D) \cdot t_{OFF} = V_{IN,MINPK} \cdot t_{ON,MAX}$

In this equation, N is the turns ratio of the transformer and  $V_D$  is the forward voltage of the output rectifier. Because  $t_{OFF} = T_{MAX} - t_{ON,MAX}$  it becomes obvious that  $t_{ON,MAX}$  and N can't be chosen independently.

The term  $N \cdot (V_{OUT} + V_D)$  is the output voltage reflected to the input or short "reflected voltage" V<sub>R</sub>. It occurs across the primary side of the transformer during the off-time of the MOSFET and adds to the input voltage as shown in **Figure 6**, increasing the maximum V<sub>DS</sub>.

#### **Option 1: Calculation of N based on DCR**

With fixed-frequency (FF) flyback controller design, it is common to start the design with a defined DCR. With this ICL88xx design, it is important to mention that the DCR is determined at the operating condition where the input AC-line is at its lowest operating point, and full output power. The ICL88xx family of devices are not FF controllers, therefore the DCR is not fixed in this system and the ratio adjusts as the AC-line voltage level changes in magnitude.

Here 57 percent was selected as the DCR. This value was found after three iterations of this calculation. Based on this input and output specification, a duty cycle larger than 57 percent led to high reflected voltages, which resulted in too-small margins for the desired 800 V MOSFET and to too-high secondary currents. On the other hand, a smaller duty cycle would result in high primary current. This current would require a more expensive MOSFET with smaller R<sub>DS(on)</sub> in order to not overheat. Furthermore, because the on-time at low-line and full load is not as long as before, the change from the first valley to the second will happen earlier, meaning at larger loads. The effect of a larger and smaller DCR can be seen in **Figure 7**.

The selected DCR of 57 percent offers a good compromise between a high reflected voltage, a cost effective MOSFET, proper on-time and reasonably sized transformer.

|                                                                     |                 | 50%             | 2             | 57%            |           | 001/            | •/            | Increase of the duty evel                |

|---------------------------------------------------------------------|-----------------|-----------------|---------------|----------------|-----------|-----------------|---------------|------------------------------------------|

| max duty cycle ratio                                                |                 | 50%             | 1%            | 51%            | 1%        | 66%             | %             | Increase of the duty cycle               |

| Calculated on-time                                                  | T_on            | 9.615E-06       | s             | 1.096E-05      | s         | 1.269E-05       | s             |                                          |

| Calculated off-time                                                 | T_off           | 9.62E-06        | s             | 8.27E-06       | s         | 6.54E-06        | s             |                                          |

| Maximum calculated winding ratio                                    | N_calc          | 2.45            |               | 3.24           |           | 4.75            |               | After selecting N the MOSFETS break down |

| Maximum calculated winding ratio                                    | N_caic          | 2.40            |               | 3.24           |           | 4.10            |               | voltage has to be checked in MOSFET      |

|                                                                     |                 |                 |               |                |           |                 |               |                                          |

|                                                                     |                 | $\frown$        |               | $\frown$       |           |                 |               |                                          |

| Selected ratio                                                      | N_select        | 2.40            |               | 3.20           |           | 4.70            |               | Leads to a larger N                      |

|                                                                     |                 | $\sim$          |               | $\sim$         |           |                 |               |                                          |

|                                                                     |                 |                 |               | 2.540          |           |                 |               | Deculting in larger inductors            |

| Primary maximum Peak current                                        | Lmax_pk         | 2.914           | Α.            | 547.24         | A<br>uH   | 2.199           | Α.            | Resulting in larger inductors            |

| Primary main Inductance                                             | L_P             | 418.60          | uH            | 547.24         | uH<br>uH  | 735.24          | uH            | with smaller primary                     |

| Selected Main Inductance                                            | L_P             | 410.00          | $Q^{\bullet}$ | 0.30           | T         | 100.00          | ~             |                                          |

| saturation flux density at 100 °C                                   | B_sat           | 0.30            | ~             | 169.00         | 1         | 0.30            | U.            | currents                                 |

| cross sectional area of the core                                    | A_e             | 169.00          |               | 90.00          | mm'<br>%  |                 |               |                                          |

| derating factor for flux density<br>Minimum Number of primary Turns | D_f_Bsat        | 90.00<br>26.70  | 7.            | 30.39          | <u> </u>  | 90.00<br>35.42  | <i>7</i> .    |                                          |

| Minimum Number of primary Turns<br>Selected Number of Turns         | N_p_min<br>N_p  | 27.00           |               | 30.00          |           | 35.42           |               |                                          |

| calculated Number of secondary Turns                                | N_p<br>N_s_calc | 11.25           | -             | 9.38           | -         | 7.45            |               |                                          |

| Selected Number of Secondary Turns                                  | N_S_Calc<br>N_s | 8.00            |               | 8.00           |           | 8.00            |               |                                          |

| Minimum Prim Auxiliary Voltage                                      | V_aux_min       | 14.00           | V             | 14.00          | V         | 14.00           | v             |                                          |

| Min Number of axiliary Turns                                        | N_a_min         | 2.13            | ×.            | 2.13           |           | 2.13            | ×.            |                                          |

| Maximum Prim Auxiliary Voltage                                      | V_aux_max       | 20.00           | V             | 20.00          | V         | 20.00           | v             |                                          |

| Max Number of axiliary Turns                                        | N_a_max         | 3.04            |               | 3.04           |           | 3.04            |               |                                          |

| Selected Number of auxiliary Turns                                  | N_a             | 4.00            |               | 4.00           |           | 4.00            |               |                                          |

| required max ontime                                                 | t_on_max        | 9.52            | us            | 10.90          | us        | 12.65           | us            |                                          |

|                                                                     |                 |                 |               |                | -         |                 |               |                                          |

|                                                                     |                 |                 |               |                |           |                 |               |                                          |

| T                                                                   |                 |                 |               |                |           |                 |               |                                          |

| Peak AC voltage                                                     |                 | 431.3351365     | V             |                | V         | 431.3351365     | V             |                                          |

| Reflected voltage                                                   |                 | 124.8           | V             | 166.4          | V         | 244.4           | V             |                                          |

| Drain source voltage seen in normal operation                       |                 | 556.1351365     |               | 597.7351365    |           | 675.7351365     | V             |                                          |

| Precentage of Voltage margin for spike on FET                       |                 | 33.00           | %             | 33.00          | 1         | 33.00           | %             |                                          |

| Estimated Voltage spike on FET                                      | V_spike_FET     | 100.65          | V             | 100.65         | V         | 100.65          | V             |                                          |

| Recomended min MOSFET break down voltage                            |                 | 656.79          | V             | 698.39         | V         | 776.39          | V             | Reducing the MOSFET                      |

| Selected MOSFET Drain break down voltage                            | V_(BR)DSS       | 800.00          | V             | 800.00         | V         | 800.00          | V             |                                          |

| Surge Margin                                                        | V_Matgin        | 143.21          | V             | 101.61         | V         |                 | ۷             | margin and current                       |

| Estimated MOSFET RMS current                                        | LMOSFET_RMS     | 0.874           | Α.            | 0.765<br>45.00 | A<br>1C/W | 0.660           | Q.            | (selection of the                        |

| Thermal Junction Ambient resitance                                  | R_JA            | 45.00           | 3             | 45.00          | 1C        |                 | ~             |                                          |

| Maximum ambient temperature<br>Maximum junction temperature         | T_A<br>T_J      | 55.00<br>110.00 | 9             | 110.00         | 1C        | 55.00<br>110.00 | °C            | breakthrough voltage)                    |

| Estimated maximum powerlosses for given temp rise                   |                 |                 | -             |                |           |                 | -             |                                          |

| and T_JA                                                            | P_tot           | 1.22            | W             | 1.22           | W.        | 1.22            | W.            |                                          |

| Initial maximum R_dson                                              | R_dson          | 0.80            | Ohm           | 1.05           | Ohm       | 1.40            | Ohrr          | Loodo to lorgor P                        |

| inida maximum r_uson                                                | n_ason          | 0.00            |               |                | - Crim    |                 | Onin          | Leads to larger R <sub>DS(on)</sub>      |

|                                                                     |                 |                 | ς) I          |                | -         |                 | ~~            |                                          |

|                                                                     |                 |                 | J             |                |           |                 | U             |                                          |

| Diode                                                               |                 |                 |               |                |           |                 |               |                                          |

|                                                                     |                 |                 |               |                |           |                 |               |                                          |

| maximum reverse voltage                                             | V_r_max         | 393.38          | V             | 295.04         | V         | 200.88          | V             | Resulting in smaller reverse             |

| maximum secondary main winding peak current                         | <br>Lsec_pk_max | 7.34            | A             | 8.56           | A         | 10.85           | A             |                                          |

| Estimated secondary Diode RMS current                               | sec_rms         | 2.03            | Δ             | 2.19           | A         | 2.47            |               | voltage but higher diode                 |

|                                                                     | <br>L_k=        | 5.00            | _~            | 5.00           | uН        | 5.00            | $Q^{\bullet}$ | currents                                 |

| measured leakage of the transformer                                 | L_k =           | 5.00            | $\cup$        |                |           |                 |               | ourrents                                 |

| a start soo sida laaksaa                                            | L k coort       | 0.44            |               | 0.36           | ωн        | 0.26            | ωн            |                                          |

Figure 7 Effect of the duty cycle on the system, showing the trade-offs

With this information, the required winding ratio of the transformer can be calculated. First the estimated ontime and off-time of the converter are calculated:

$$t_{ON,MAX} = \frac{DCR_{MAX}}{f_{SW,MIN}} \tag{4}$$

$$ff = \frac{1}{f_{owner}} - t_{on,MAX} \tag{5}$$

$$\iota_{off} = \frac{1}{f_{SW,MIN}} - \iota$$

+

$$t_{on,max} = \frac{57\%}{52 \ kHz} = 10.96 \ \mu s \tag{6}$$

$$t_{off} = \frac{1}{52 \, kHz} - \ 12.7 \, \mu s = 6.5 \, \mu s$$

Based on the (3), N can be defined as:

$$\frac{V_{in}}{V_{out}} = N \times \frac{t_{ON}}{t_{OFF}} \tag{7}$$

$$N \le \frac{V_{AC,MIN,PK}}{V_{OUT}} \times \frac{t_{ON,MAX}}{t_{OFF}}$$

(8)

$$N \le \frac{90 \,\mathrm{V} \times \sqrt{2}}{52 \,\mathrm{V}} \times \frac{10.96 \,\mathrm{\mu}s}{6.5 \,\mathrm{\mu}s} = 3.23 \tag{9}$$

Based on the above, **N = 3.2** is selected.

Determine the drain-source voltage rating (with margin) of the main switching power MOSFET using the selected turns ratio:

$$V_{AC,MAX,PK} = V_{AC,MAX} \times \sqrt{2} = 300 V \times \sqrt{2} = 431 V$$

(10)

$$V_R = V_{OUT} \times N = 52 V \times 3.2 = 166.4 V \tag{11}$$

$$V_{DS} = V_R + V_{AC,MAX,PK} = 431 V + 166.4 V = 597.4 V$$

(12)

With an RCD snubber network positioned across the primary main winding (see **Figure 10**),  $V_{\text{SPIKE}}$  can be estimated to be around 30 to 45 percent of  $V_{AC,max}$ .  $V_{AC,max}$  is 305  $V_{\text{RMS}}$ ;  $V_{\text{SPIKE}}$  is assumed to be  $\approx$  100 V.

Minimum MOSFET breakdown voltage V<sub>DS</sub> can be calculated as:

$$V_{DS} = V_{DS} + V_{spike} = 597.4 V + 100 V = 697.4 V$$

(13)

It is good design practice to select a power MOSFET with a  $V_{DS}$  rating above the worst-case normal operation.

Based on the calculation above, a MOSFET with  $V_{DS}$  = 800 V can be selected. Here we have

$$800 V - 697.4 V = 102.6 V \tag{14}$$

margin for input overvoltage or surge events.

For additional information on lightning surge and for a simulation circuit, you can read the **Lightning surge discharge design for SMPS application note**.

#### Option 2: Calculation of turns ratio (N) based on MOSFET VDs rating

An alternative way to determine both the turns ratio and the  $V_{DS}$  rating of the power MOSFET is to first declare the MOSFET  $V_{DS}$  rating. In this example, an 800 V MOSFET was selected. In narrow-range designs and low output voltage designs a 700 V MOSFET might also be suitable. If the design comprises a large output voltage, or a greater voltage margin on the main power MOSFET is desired, a MOSFET with a  $V_{DS}$  rating of 950 V is possible.

$$V_{DS,max} = V_{AC,max} \times \sqrt{2} + N \times V_{OUT} + V_{SPIKE} + V_{MARGIN}$$

(15)

$$N \le \frac{V_{DS,max} - V_{AC,max} \times \sqrt{2} - V_{SPIKE} - V_{MARGIN}}{V_{OUT} + V_D}$$

(16)

Where  $V_{AC,max,pk}$  is  $\sqrt{2}$  times  $V_{AC,max}$  and  $V_D$  is the secondary main output diode forward voltage (0.70 V).

N can then be calculated as:

$$N \le \frac{800 \, V - \sqrt{2} \times 300 \, V - 100 \, V - 100 \, V}{52 \, V + 0.7 \, V} = 3.21 \tag{17}$$

Finally, **N = 3.2** has been selected. From volt-second balance we finally get:

$$t_{ON,MAX} = \frac{V_R}{V_R + V_{AC,MIN,PK}} \cdot T_{MAX}$$

(18)

$$T_{\max} = \frac{1}{f_{sw,min}} = \frac{1}{52 \ kHz} = 19.23 \ \mu s \tag{19}$$

$$V_R = 3.2 \cdot (52 V + 0.7 V) = 168.64 V \tag{20}$$

$$t_{ON,MAX} = \frac{168.64 V}{168.64 V + 127.28 V} \cdot 19.23 \ \mu s = 0.57 \cdot 19.23 \ \mu s = 10.96 \ \mu s \tag{21}$$

#### Calculation of the peak currents

After finding the winding ratio by one of the two methods, the maximum primary-side currents have to be calculated.

The maximum primary peak current  $I_{Q1.MAXPK}$  can then be calculated as:

### ICL88xx flyback design guide For high power factor flyback converter with constant voltage output PFC flyback converter design

$$I_{Q1.MAXPK} = \frac{2 \cdot I_{AC.MAXPK}}{d_{MAX}} = \frac{2 \cdot \sqrt{2} \cdot P_{OUT}}{\eta \cdot V_{AC,MINRMS} \cdot DCR_{MAX}}$$

(22)

$$I_{Q1.MAXPK} = \frac{2 \cdot \sqrt{2} \cdot 43.2 W}{0.9 \cdot 90 V \cdot 0.57} = 2.605 A$$

As a result, the primary main winding inductance  $L_p$  can be defined and calculated as:

$$L_{P} = \frac{V_{AC,MINPK}}{I_{Q1,MAXPK}} \cdot t_{ON,MAX}$$

(23)

$$L_{P} = \frac{\sqrt{2} \cdot 90 V \cdot 11.13 \,\mu s}{2.605 \,A} = 544 \,\mu H$$

An inductance of  $L_P = 544 \ \mu H$  is selected for this design.

Based on core cross-sectional area,  $A_e = 120.3 \text{ mm}^2$  and saturation flux density at 100°C,  $B_{SAT(T=100^\circ C)} = 0.390$  Tesla for PQ26/20 core, the transformer primary main winding turns  $N_p$  can be defined as:

$$N_p \ge \frac{L_p \cdot I_{Q1,MAXPK}}{A_e \cdot B_{SAT(T=100^\circ C)} \cdot D_{F,SAT}}$$

(24)

Where  $D_{F,SAT}$  is the derating factor to ensure the designed transformer maximum flux density,  $B_{MAX}$  is below  $B_{SAT(T=100^{\circ}C)}$  by a margin of (100 percent -  $D_{F-BSAT}$ ) from saturation, and it is typical to set  $D_{F-BSAT}$  in the range of 85 to 95 percent for a margin of 5 to 15 percent from transformer core saturation.

$D_{\text{F-BSAT}}$  = 90 percent,  $N_p$  can then be calculated as:

$$N_p \ge \frac{544 \times 10^{-6} \, H \times 2.605 \, A}{120.1 \times 10^{-6} m^2 \times 0.39 \, T \times 90\%} = 30.39 \tag{25}$$

N<sub>p</sub> = 32 is selected.

The transformer secondary main winding turns  $N_s$  can then be calculated as:

Design Guide

$$N_s = \frac{N_p}{N} = \frac{32}{3.2}$$

(26)

$N_{s} = 10$

#### Auxiliary winding ratio determination

Define a minimum and maximum turns ratio based on good design choices.

To ensure fast start-up of the system, and to eliminate restart, the  $V_{cc}$  supply powering the ICL88xx device is chosen as 14 V. As a result, the recommended minimum primary auxiliary winding turns  $N_{A,MIN}$  can be defined and calculated as:

$$N_{A,MIN} = \frac{V_{A,MIN} \times N_s}{(V_{OUT} + V_D)} = \frac{14 \, V \times 10}{(54 \, V + 0.7 \, V)} = 2.56 \tag{27}$$

To ensure high efficiency,  $V_{CC}$  voltage should remain less than 19 V;  $V_{A,MAX}$  is therefore defined as 19 V.  $N_{A,MAX}$  can be defined and calculated as:

$$N_{A,MAX} = \frac{V_{A,MAX} \times N_s}{(V_{OUT} + V_D)} = \frac{19 \, V \times 10}{(54 \, V + 0.7 \, V)} = 3.47$$

(28)

Based on the calculation results of equations (27) and (28), primary auxiliary winding turns  $N_A = 3$  is selected.

An additional auxiliary winding on the secondary side is added to power the SSR feedback circuit, as its op-amp or shunt regulator's maximum operating voltage is considerably less than V<sub>OUT-SET</sub> of 54 V.

The recommended minimum secondary auxiliary winding turns  $N_{A,SEC,MIN}$  and recommended maximum secondary auxiliary winding turns  $N_{A,SEC,MAX}$  can be defined respectively as per  $N_{A,MIN}$  and  $N_{A,MAX}$ , as shown below:

$$N_{A,SEC,MIN} = N_{A,MIN} = 2.56$$

(29)

$N_{A,SEC,MAX} = N_{A,MAX} = 3.47$

(30)

N<sub>A,SEC</sub> = 3 is selected.

### 3.2 Flyback MOSFET and secondary main output diode selection

The CoolMOS<sup>™</sup> P7 MOSFET series from Infineon is well suited to ICL88xx applications, due to its balance of high performance and reasonable cost.

Through optimizing key parameters ( $C_{oss}$ ,  $E_{oss}$ ,  $Q_g$ ,  $C_{iss}$  and  $V_{GS(th)}$ ), integrating a Zener diode for ESD protection and other measures, this product family fully addresses market concerns in performance, ease of use and price/performance ratio.

The 700 V, 800 V and 950 V CoolMOS<sup>™</sup> P7 MOSFET series have been specifically designed for flyback and PFC topologies (hard-switching).

MOSFET drain-source breakdown voltage  $V_{(BR)DSS} = 800 V$  is selected in this design example based on  $V_{AC,max}$  of 300  $V_{RMS}$  and transformer design in chapter **3.1**.

On-resistance ( $R_{DS(on)}$ ) of the MOSFET should be considered next to ensure power dissipation under all operating conditions.

MOSFET *R*<sub>DS(on)</sub> and maximum primary RMS current *I*<sub>PRI-RMS-MAX</sub> must be estimated based on:

$$I_{Q1,MAX(RMS)} \approx I_{Q1,MAXPK} \times x \tag{31}$$

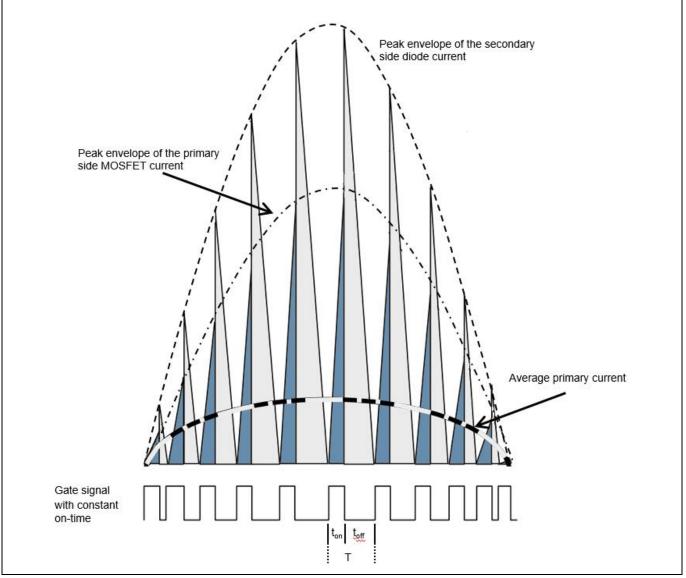

In a HPF flyback converter, the peak current occurs at the peak of the sinusoidal input voltage. The waveform of the current through the MOSFET is triangular in shape and flows only during the constant on-time of the MOSFET. Connecting all the peaks of the currents during one half-cycle of the input voltage would lead to a sinusoidal shape. Unfortunately, it is not easy to calculate the accurate average primary current, because the off-time is not fixed. These relationships are illustrated in **Figure 8**.

The value x, which helps to calculate the average current out of the peak current in a HPF flyback, is dependent on the ratio between the minimum peak input voltage and the reflected output voltage. Although these values vary from design to design, this value can be approximated by 0.3. If the DCR were fixed, e.g., due to DC input, x could be calculated as:

$$x = \sqrt{\frac{DCR}{6}}$$

(32)

(33)

With the initially chosen DCR<sub>MAX</sub> of 0.57, x would be 0.31, which shows that 0.3 is a fair approximation.  $I_{PRI-MAX(RMS)}$  can then be calculated as:

$I_{Q1,MAX(RMS)} \approx 2.605 \times 0.3$

$I_{Q1,MAX(RMS)} \approx 0.765 A$

Figure 8 Relationship of the main flyback currents with regard to the input voltage

#### **MOSFET** *R*<sub>DS(on)</sub> selection

A critical electrical parameter when selecting a power MOSFET is the on-state resistance. The limit for the onstate resistance is the maximum allowable power dissipation of the application and the maximum junction temperature of the MOSFET.

### ICL88xx flyback design guide For high power factor flyback converter with constant voltage output PFC flyback converter design

(34)

A starting point for selecting the proper on-resistance of a power MOSFET is packaging and cost. For sub-100 W flyback converters, a TO-220, DPAK or SOT-223 package is likely to be selected.

Once a MOSFET package has been chosen, an estimate of on-state resistance is determined. During bench analysis, the MOSFET can be optimized for lower on-resistance, or higher residence (to save cost) if required. Infineon offers dozens of on-state resistance options for a given package and rated drain-source voltage.

The power losses of the MOSFET can be divided into the conduction losses and the switching losses. An easy first-pass guideline is to assume 50 percent conduction losses and 50 percent switching losses.

$$P_{\text{TOT}} = P_{\text{COND}} + P_{\text{SW}},$$

$$P_{\text{COND}} = \frac{1}{2} P_{\text{TOT}}$$

#### $R_{DS(on)}$ determination and process

- Package choice: DPAK

- Typical *R*<sub>0JA</sub> for this package ranges from 30°C/W to 50°C/W

- MOSFET RMS current is determined to be 0.765 A

- Maximum allowed junction temperature is 100°C

- Maximum operating ambient air temperature is 45°C

$$R_{\theta JA} = \frac{T_J - T_C}{P_{TOT}}$$

(35)

$$P_{\rm TOT} = \frac{100^{\circ}C - 45^{\circ}C}{45\frac{\circ}{W}} \approx 1.25 \,\rm W \tag{36}$$

$$P_{\text{COND}} = \frac{1}{2} P_{\text{TOT}} = 0.625 \text{ W}$$

(37)

(38)

$$R_{\text{DSON-MAX}} = \frac{P_{COND}}{I_{RMS}^2}$$

$$R_{\text{DSON-MAX}} = \frac{0.625 W}{(0.765 A)^2} = 1 \Omega$$

Referring to the calculation results of equation (38) and **Table 3** below,  $R_{DS(on),25^{\circ}C} = 900 \text{ m}\Omega$  is selected.

#### Table 3 800 V CoolMOS<sup>™</sup> P7 MOSFET selection table

| R <sub>DS(on)</sub><br>[mΩ] | TO -220     | TO-220 FullPAK | TO-247      | TO-252<br>(DPAK) | TO-251<br>(IPAK) | TO-251<br>(IPAK Short Lead) | SOT-223     | TO-220 FullPAK narrow<br>lead |

|-----------------------------|-------------|----------------|-------------|------------------|------------------|-----------------------------|-------------|-------------------------------|

| 280                         | IPP80R280P7 | IPA80R280P7    | IPW80R280P7 | IPD80R280P7      |                  |                             |             | IPAN80R280P7                  |

| 360                         | IPP80R360P7 | IPA80R360P7    | IPW80R360P7 | IPD80R360P7      |                  |                             |             | IPAN80R360P7                  |

| 450                         | IPP80R450P7 | IPA80R450P7    |             | IPD80R450P7      |                  |                             |             | IPAN80R450P7                  |

| 600                         | IPP80R600P7 | IPA80R600P7    |             | IPD80R600P7      | IPU80R600P7      | IPS80R600P7                 | IPN80R600P7 |                               |

| 750                         | IPP80R750P7 | IPA80R750P7    |             | IPD80R750P7      | IPU80R750P7      | IPS80R750P7                 | IPN80R750P7 |                               |

| 900/950                     | IPP80R900P7 | IPA80R900P7    |             | IPD80R900P7      | IPU80R900P7      | IPS80R900P7                 | IPN80R950P7 |                               |

| 1200                        | IPP80R1K2P7 | IPA80R1K2P7    |             | IPD80R1K2P7      | IPU80R1K2P7      | IPS80R1K2P7                 | IPN80R1K2P7 |                               |

| 1400                        | IPP80R1K4P7 | IPA80R1K4P7    |             | IPD80R1K4P7      | IPU80R1K4P7      | IPS80R1K4P7                 | IPN80R1K4P7 |                               |

| 2000                        |             |                |             | IPD80R2K0P7      | IPU80R2K0P7      | IPS80R2K0P7                 | IPN80R2K0P7 |                               |

| 2400                        |             |                |             | IPD80R2K4P7      | IPU80R2K4P7      | IPS80R2K4P7                 | IPN80R2K4P7 |                               |

| 3300                        |             |                |             | IPD80R3K3P7      | IPU80R3K3P7      |                             | IPN80R3K3P7 |                               |

| 4500                        |             |                |             | IPD80R4K5P7      | IPU80R4K5P7      |                             | IPN80R4K5P7 |                               |

#### Secondary-side diode selection

The first step is to estimate the maximum reverse voltage  $V_{RD,MAX}$  and maximum secondary main winding peak current  $I_{SEC-MAX(PK)}$ , based on:

$$V_{RD,MAX} = V_{D,SPIKE} + V_{OUT} + \frac{V_{AC,MAX,PK} + V_{MARGIN}}{N}$$

(39)

Where  $V_{D,SPIKE}$  is the diode reverse voltage spike.

Assuming:

$$V_{D,SPIKE} \approx 35\% \times \left( V_{OUT} + \frac{V_{AC,MAX,PK} + V_{MARGIN}}{N} \right)$$

(40)

)

$$V_{RD,MAX} \approx 135\% \times \left(V_{OUT} + \frac{V_{AC,MAX,PK} + V_{MARGIN}}{N}\right) = 135\% \times \left(54V + \frac{\sqrt{2} \times 305V + 100V}{3.2}\right)$$

(41)

$$V_{RD,MAX} \approx 295.04V$$

$$I_{SEC-MAX(PK)} \approx I_{Q1.MAX,PK} \cdot \frac{N_p}{N_s} = 2.55 \cdot \frac{32}{10}$$

(42)

$I_{SEC-MAX(PK)} \approx 8.56 A$

Based on the above, a secondary main output diode with repetitive reverse voltage rating  $V_{RRM} = 300 V$  is selected. To minimize its switching and conduction losses, the selected diode also has the properties of hyperfast recovery speed and low forward voltage drop at  $I_{SEC-MAX(PK)}$ .

In addition, a RC secondary snubber network, for example a 10  $\Omega$  resistor in series with 150 pF capacitor, is deployed across the secondary main output diode, to suppress the diode reverse voltage spike and the EMI.

### **3.3 Output capacitor**

$V_{ripple,out(pk-pk),max}$  denotes the maximum allowable secondary main output voltage peak-to-peak ripple level. Assuming the flyback output in this design example is connected to a second-stage CC buck regulator, which has a maximum LED voltage load  $V_{LED,max}$  of 48 V and maximum allowable duty cycle  $D_{buck,max}$  of 95 percent,  $V_{ripple,out(pk-pk),max}$  can be defined and calculated as:

$$V_{rippleout(pk-pk),\max} = 2 \times \left(V_{out} - \frac{V_{LEDmax}}{D_{buckmax}}\right) = 2 \times \left(54 V - \frac{48 V}{0.95}\right) = 6.95 V$$

<sup>(43)</sup>

The secondary main output capacitor C<sub>out,main</sub> value can then be defined and calculated as:

$$C_{out,main} \ge \frac{P_{out}}{2 \times \pi \times F_{line,min} \times V_{ripple,out(pk-pk),max} \times V_{out}} = \frac{41.6W}{2 \times \pi \times 47Hz \times 6.95V \times 52V}$$

(44)

= 387 µF

Considering the electrolytic capacitor value tolerance,  $C_{\text{out,main}} = 470 \,\mu\text{F}$  is selected in this design example. For switching noise filtering, low-ESR ceramic capacitors  $C_{\text{out,main,lowESR1}} = 1 \,\mu\text{F}$  and  $C_{\text{out,main,lowESR2}} = 0.1 \,\mu\text{F}$  are also added in parallel with  $C_{\text{out,main}}$ .

Design Guide

The secondary auxiliary output capacitor  $C_{out,aux,sec}$  is recommended to be at least 47  $\mu$ F, to ensure stable operating voltage supply of the SSR FB circuit, during burst mode.

$C_{\text{out,aux,sec}}$  = 100 µF is selected in this design example.

### 3.4 MOSFET snubber design

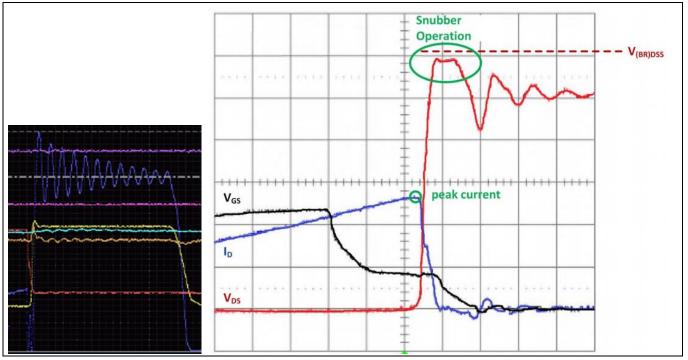

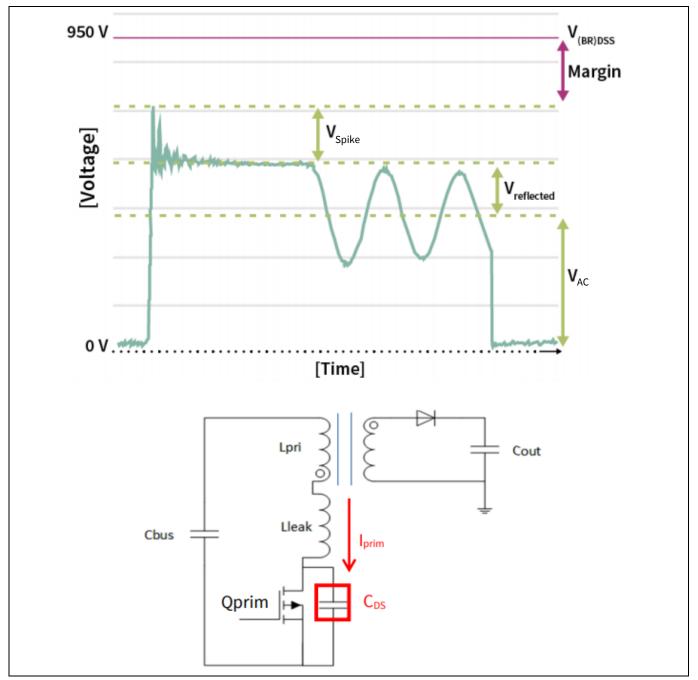

The voltage across the drain-source of the power MOSFET is ideally a square wave with a plateau determined by the AC input voltage and the reflected output voltage.

During the turn-off transition of the power MOSFET, the MOSFET switch stops the current flow through the leakage inductance of the transformer. This causes a spike voltage at the drain of the MOSFET. Together with the stray capacitance of the circuit, this produces high-frequency, high-amplitude oscillation. This high-frequency voltage spike is seen rising above the plateau mentioned earlier and needs to be considered when determining the V<sub>DS</sub> rating of the power MOSFET.

Many flyback design application notes ignore the snubber; it is sometimes difficult to optimize, and no clear guideline/optimum calculation can be given as each circuit is different and the stray inductances and capacitances vary. But there are three major issues if this waveform is ignored:

- The excessive voltage spike can lead to an avalanche breakdown of the MOSFET if the margin is too small.

- Ringing energy is radiated and conducted throughout the system (power supply and load), which causes noise issues and can cause mis-triggering.

- The ringing shows up in the conducted and radiated EMI measurement.

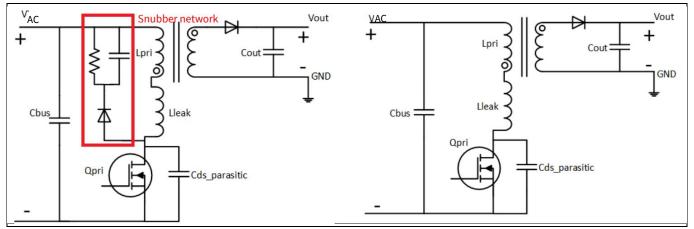

There are numerous methods to dampen the oscillation and reduce the voltage spike magnitude. In this document the RCD circuit is explained, which can be seen in **Figure 10**.

First the leakage inductance of the transformer must be measured, because it has the dominant role in the oscillation. Furthermore, it is the easiest to measure. The ringing capacitance is a combination of inter-winding capacitance, non-linear semiconductor capacitances and other stray capacitances in the system. Luckily, the resonance is in the low MHz region, so most of the oscilloscopes should be able to measure and display it.

The voltage spike at the MOSFET can be clamped to a desired maximum  $V_{\text{SPIKE}}$  value by selecting an appropriate valued capacitor. The resistor in parallel to the capacitor has to dissipate the charge stored in it.

The design of the clamping network for a PFC flyback is a bit more complicated than that for one with constant input voltage. This is because the peak drain current is modulated by a sinusoidal half-wave and thus the energy stored in the leakage inductance has a modulation of the form  $(\sin(2 \times \pi \times f_L \times t))^2$ , with  $f_L$  being the line frequency. Consequently, the **average** energy that needs to be dissipated in the clamping network is half of that calculated by means of  $I_{Q1.MAXPK}$ :

$$P_{Snub} = \frac{1}{4} \times L \times I_{Q1.MAXPK}^{2} \times f_{SW} \times \frac{V_{R} + V_{SPIKE}}{V_{SPIKE}}$$

(45)

The factor  $(V_R + V_{SPIKE})/V_{SPIKE}$  results from the fact that the voltage across the leakage inductance (V<sub>SPIKE</sub>) and the reflected voltage (V<sub>R</sub>) are in series together conduct the demagnetization current of the leakage inductor.

### ICL88xx flyback design guide For high power factor flyback converter with constant voltage output PFC flyback converter design

In this design example, a MOSFET with a breakdown voltage of 800 V has been selected and this limit should not be exceeded and  $V_{SPIKE}$  has been selected to be 100 V. Then the calculated dissipation of the clamp network would be:

$$P_{Snub} = \frac{1}{4} \times 5 \ \mu H \times (2.605 \ A)^2 \times 52 \ kHz \times \frac{166 \ V + 100 \ V}{100 \ V} = \mathbf{1.17} \ W$$

(46)

The actual power dissipation will be lower than that since part of the energy is transferred to the output capacitance of the MOSFET and parasitic capacitances of the system.

The value of the resistor is based on  $P_{Snub}$  that needs to be dissipated by the latter. Assuming that the voltage across the clamp network is reasonable constant, its value can be determined by:

$$R_{Snub} = \frac{(V_R + V_{SPIKE})^2}{P_{Snub}}$$

$$R_{Snub} = \frac{(166 V + 100 V)^2}{1.17 W} = 60.4 k\Omega$$

(47)

In order to calculate the value of the capacitor, we must specify how large the maximum ripple of the snubber capacitor is allowed to be. Let's assume it to be 30 percent in this calculation:

$$C_{Snub} = \frac{V_{SPIKE} + V_R}{V_{ripple} \times R_{Snub} \times f}$$

(48)

$$C_{Snub} = \frac{100 V + 166 V}{(30\% \times (100 V + 166 V)) \times 60 k\Omega \times 52 kHz} = 1.1 nF$$

Due to parasitic capacitances mentioned earlier, the actual power dissipation will be smaller which means the optimum resistance will be higher and the capacitance smaller than the values calculated above.

Furthermore, a small capacitor is beneficial for the THD performance, since close to the zero crossing of the input voltage, less energy is required to charge up the capacitor to  $V_R$  if it gets discharged below this voltage. In addition, a small capacitor is also beneficial for the efficiency of the burst mode for the same reason.

The resistor has a similar impact on the system. The smaller the losses of the snubber due to a larger resistor, the better the THD performance and the efficiency.

These measures, smaller capacitor and larger resistor, increase the drain voltage of the MOSFET. A trade-off has to be made between a higher  $V_{DS}$  MOSFET voltage versus the losses in the snubber.

This calculation offers a good starting point for the optimization.

Further guidelines for a proper RCD snubber design:

- The snubber diode is crucial. It must be able to withstand the occurring peak voltages, and it needs to be able to handle the currents. It is strongly advised to use a fast diode in order to achieve good THD and PF.

- The voltage across the snubber capacitor should be very stable. If the voltage is triangular or shows spikes, either the selected diode has a too-low voltage rating, the selected resistor is too small or the capacitor is too small.

- When optimizing the snubber, a compromise must be found between spike voltage and power dissipation. The lower the spike voltage, the higher the losses.

- The voltage across the snubber circuit is high, so care should be taken when selecting the voltage rating of the capacitor.

- Adjust the clamping voltage by raising or lowering the resistance of the snubber resistor, with all other snubber components fixed.

After some testing, 630 pF and 200 k $\Omega$  were used in the final design, since these values clamp the voltage sufficiently. For stronger clamping and a more stable voltage between the capacitor and the diode, a larger capacitor can be used.

**Figure 9**

Oscillating drain-source voltage without snubber

# ICL88xx flyback design guide For high power factor flyback converter with constant voltage output

PFC flyback converter design

Figure 10 The typical RCD (in red) snubber vs. snubberless configuration

### Design consideration: Snubberless design

The new 950 V variant of the CoolMOS<sup>™</sup> P7 MOSFET enables a more efficient standard flyback without RCD snubber.

By removing the snubber network and switching to a snubberless design, the overall system efficiency can be improved. Switching losses and snubber losses play a large role in the losses of this supply due to the HV operation. In addition to improving the system efficiency, the snubberless flyback converter also reduces the necessary PCB area and removes the cost of the RCD network.

The losses of the system are reduced in a snubberless design (see **Figure 9**) due to removing two key loss mechanisms.

The first is that the RCD network charges up to the reflected voltage every switching cycle regardless of the system load. The leakage inductance energy also increases this voltage, leading to further losses across the snubber resistor.

The second loss mechanism comes from the additional capacitance added to the switching node from the RCD network, as well as needing to charge the capacitance across the RCD diode junction. These loss mechanisms are eliminated by removing the RCD snubber network.

To keep the MOSFET  $V_{DS}$  from getting too high, an additional drain-source capacitance is added across the drain node of the MOSFET. This leads to a higher  $C_{DS}$  switching loss when compared to the design with a snubber network, as shown above in red. The energy that is stored in the transformer leakage inductance gets dissipated in the high-frequency copper loss of the transformer rather than in the RCD network.

PFC flyback converter design

Figure 11 The MOSFET V<sub>DS</sub> margin needs consideration for snubberless operation

In designing a snubberless flyback converter, it is critical to make sure the  $V_{(BR)DSS}$  of the MOSFET is not exceeded. The  $V_{DS}$  of a MOSFET consists of three main sections, as shown in **Figure 29**. The  $V_{DS}$  is the total of the bus voltage ( $V_{AC}$ ), the reflected voltage ( $V_{R}$ ) and the ringing voltage ( $V_{SPIKE}$ ). The ringing voltage of the MOSFET is the only portion that is affected in the transition from an RCD snubber to a snubberless design. To understand how to remove the snubber, the mechanism behind the drain-source ringing needs to be understood.

When the MOSFET is turned on in a flyback converter, the current through the primary side of the transformer begins to ramp. When the MOSFET turns off, this energy gets transferred to the secondary of the flyback converter. Not all of this energy gets transferred to the secondary, and the leakage inductance is the energy that cannot couple to the secondary. This energy then transfers to the total output capacitance of the MOSFET, which consists of the MOSFET  $C_{DS}$ , transformer parasitic capacitance, trace capacitance and any other

### ICL88xx flyback design guide For high power factor flyback converter with constant voltage output PFC flyback converter design

capacitance on the drain node. An LC ringing occurs with the period set by the C<sub>DS</sub> total and the leakage. To control the peak voltage of the drain-source ringing, an external capacitance can be added in parallel to the drain source of the MOSFET. Furthermore, cold start-up sequences must be considered.

As a recommendation, a minimum of 10 percent margin should be kept from the drain-source breakdown voltage with worst-case component tolerances.

More information about the snubberless design can be found in the **950 V CoolMOS™ P7 MOSFET** application note.

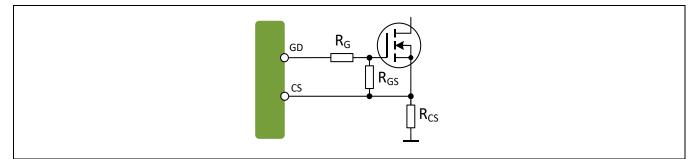

### 3.5 CS resistor and GD pin-related design

**Figure 12** shows the connections of the current sense (CS) resistor  $R_{cs}$ , gate resistor  $R_{g}$  and gate source resistor  $R_{gs}$ .

Figure 12 GD pin, CS pin, R<sub>cs</sub>, R<sub>g</sub> and R<sub>gs</sub> connections

Current through the main power MOSFET is sensed across resistor R<sub>cs</sub>, as illustrated above.

The recommended minimum CS resistor  $R_{CS-MIN}$  based on the datasheet value  $V_{OCP1-MIN}$  value is defined and calculated as:

$$R_{CS-MIN} = \frac{V_{OCP1-MIN}}{I_{PRI-MAX(PK)}} = \frac{0.57 V}{2.605 A} = 0.224 \Omega$$

<sup>(49)</sup>

The recommended maximum CS resistor  $R_{CS-MAX}$  based on the datasheet value  $V_{OCP1-MIN}$  value is defined and calculated as:

$$R_{CS-MAX} = \frac{V_{OCP1-MIN}}{I_{PRI-MAX(PK)}} = \frac{0.65 \, V}{2.605 \, A} = 0.255 \, \Omega \tag{50}$$

Based on the calculation results above, CS resistor  $R_{cs} = 0.22 \Omega$  is selected as a starting point in this design example.

### PFC flyback converter design

Even when not intending to use the second OVP feature described in chapter 4.1, it is advised to connect a resistor from the CS pin to the R<sub>cs</sub>. The size of the resistor should be a view 100 ohms smaller than the calculated resistor. This helps to limit the occurring voltage spikes on this pin.

After some measurements at low-line and maximum load, the value of the resistor can be adjusted to limit the primary-side current. Keep in mind that some margin to the normal full load operation has to be kept to allow a quick regulation in case of load changes.

Resistor  $R_{\rm G}$  is placed in series with the main power MOSFETs' gate pin to damp the gate-rise oscillation, and  $R_{\rm GS}$ is to ensure the MOSFET remains in an off-state when AC input is applied, with the IC not being activated yet. R<sub>G</sub> = 47  $\Omega$  and  $R_{GS}$  = 47 k $\Omega$  are selected in this design example.

The gate-drive peak voltage  $V_{GD,pk}$  is typically 11 V with sufficient  $V_{CC}$  voltage supply. To achieve a good balance of switching loss and EMI, the gate voltage rising and falling slope can be modified by using external components around the MOSFET, including the gate resistance. More information can be found in the **CoolMOS<sup>™</sup> P7 MOSFET** application note.

With the high-speed switching characteristics of CoolMOS<sup>™</sup> P7 MOSFET, which reduce the switching losses, it is recommended to start with a gate resistor  $R_{\rm G}$  of 20 to 50  $\Omega$ .

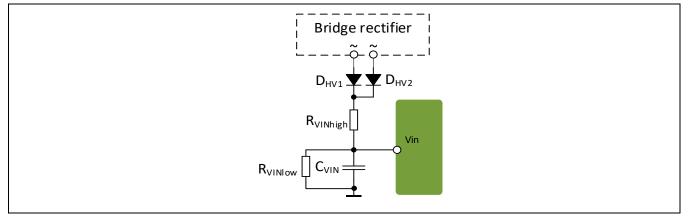

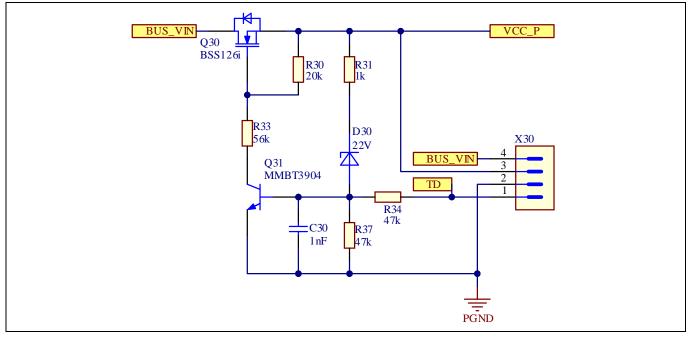

#### 3.6 VIN pin-related design

The rectified input voltage is sensed through an external resistor divider which consists of R<sub>VINhigh</sub> and R<sub>VINhow</sub> at the VIN pin as shown in Figure 13. This input voltage sensing function enables BI and BO protection as well as input OVP and AC-DC detection.

A capacitor C<sub>VIN</sub> should also be connected between the HV pin and ground in parallel to R<sub>VINIow</sub>.

Figure 13 HV pin, R<sub>VINhigh</sub>, R<sub>VINlow</sub>, C<sub>VIN</sub>, D<sub>HV1</sub> and D<sub>HV2</sub> connections

Brown-in – At the initial start-up (AC plug-in), the voltage at the VIN pin must exceed the 0.63 V threshold to initiate PFC start-up; this is defined as brown-in (BI).

- AC RMS line voltage at BI is defined as  $V_{IN_BI}$ . •

- VIN pin BI threshold is 0.63 V, noted as  $V_{\rm BI}$ .

**Brown-out** – Once the converter is operating, brown-out (BO) is detected when the voltage at the VIN pin drops below the 0.42 V threshold  $V_{B0}$ . ICL88xx stops PFC switching and enters auto restart. The normal system operation recovers if the average voltage at the VIN pin rises above  $V_{BI}$  (0.63 V).

- AC RMS line voltage at BO is defined as  $V_{IN_{BO}}$ .

- VIN pin BO threshold is 0.42 V, noted as  $V_{BO}$ .

Determining BI and BO voltages and sense resistor values:

- 1. Set BI voltage value ( $V_{AC-Bi} = 85 V$ ).

- 2. Determine  $R_{VINhigh}$  and  $R_{VINlow}$  given BI value.

- 3. Calculate BO voltage with  $R_{VINhigh}$  and  $R_{VINlow}$  values determined from the second step.

Set the lower resistor value to 43 k $\Omega$  ( $R_{B02}$ ), declare the BI threshold at 85 V AC to make sure the system starts up at 90 V AC and calculate the upper resistor value. m is a correction factor for the internal averaging.

$$R_{\text{VINhigh}} = \left(\frac{V_{\text{AC-BI}} \times m}{V_{\text{BI}}} - 1\right) \times R_{\text{VINlow}}$$

$$R_{\text{VINhigh}} = \left(\frac{85 \text{ V} \times 1.11}{0.63 \text{ V}} - 1\right) \times 43 \text{ k}\Omega \approx 5.8 \text{ M}\Omega$$

(51)

The calculated  $R_{BO1}$  = 5.8 M $\Omega$  is divided into three parts to reduce the voltage and power stress of the resistor (SMT 1206 size). To improve the accuracy of the measurement, resistors with tolerance of less than 1 percent should be selected.

Rearrange the previous equation and now determine the BO voltage. For BO, a different correction factor must be considered:

$$V_{AC-BO} = \frac{\left(\frac{R_{VINhigh} + R_{VINlow}}{R_{VINlow}}\right) \times V_{BO}}{n}$$

$$V_{AC-BO} = \frac{\left(\frac{5.8 \text{ M}\Omega + 39 \text{ k}\Omega}{39 \text{ k}\Omega}\right) \times (0.42 \text{ V})}{0.9} = 70 \text{ V}_{RMS}$$

(52)

The BI voltage can be calculated once  $R_{VINHigh}$  and  $R_{VINlow}$  are determined:

$$V_{IN_{OVP}} = \frac{\left(\frac{5.8 \text{ M}\Omega}{39 \text{ k}\Omega} + 1\right) \times (2 \text{ V})}{0.9} = 332 \text{ V}_{\text{RMS}}$$

(53)

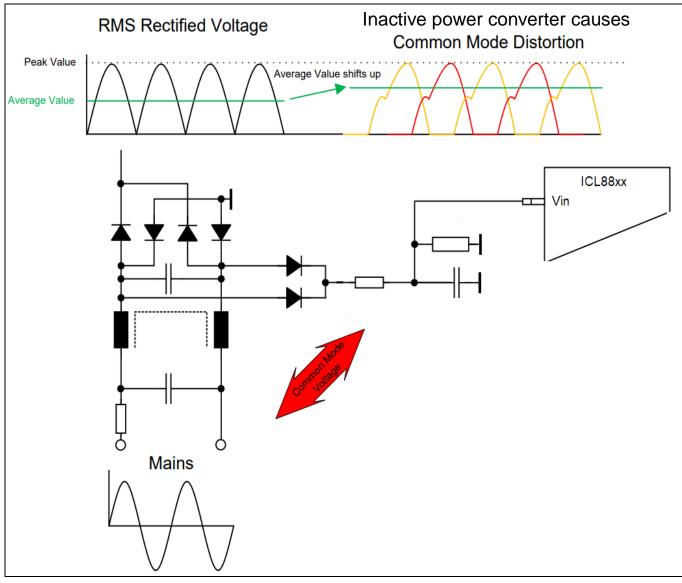

The BO detection function of the ICL88xx is based on a DC voltage on the VIN pin that represents the average value of the rectified mains voltage – see **Figure 14**.

The voltage sensed at the VIN pin of the ICL88xx becomes distorted when the converter is off, or has shut down due to a protection. This voltage distortion is due to the diode bridge not conducting, and common-mode (CM) voltages from the AC main to GND being present (refer to **Figure 14**).

It results in a shifting up of the average value of the RMS rectified voltage; see "Common mode distortion" in **Figure 14**. For this reason, the VIN divider calculations need two different correction values depending on the initial mode.

Figure 14 Impact of conducting vs. non-conducting (distortion)

**AC input line sensing** – A small filter capacitor needs to be placed close to the VIN pin of the ICL88xx. The value of the capacitor should be small enough to react quickly to line voltage changes and not trigger the short protection  $V_{VINUV}$  = 0.208 V, and not too large to safely detect an AC or DC voltage.

Determine VIN sense pin average voltage during the lowest AC-line operation (90 V AC):

$$V_{VIN_{AVG}} = V_{AC,min} \times n \times \frac{R_{VINlow}}{R_{VINhigh} + R_{VINlow}}$$

(54)

$$V_{VIN_{AVG}} = 90 V \times 0.9 \times \frac{39 k\Omega}{5.8 M\Omega + 39 k\Omega} = 0.54 V$$

$$V_{VIN_{ripple-max}} = (V_{VIN_{AVG}} - V_{VIN_{UV}}) \times 2 = (0.540 V - 0.208 V) \times 2 = 0.664 V$$

(55)

The subtraction must be multiplied by two because the peak-to-peak value is needed.

Using the complex voltage divider, the minimum capacitor size for these resistors can now be calculated:

$$Z_{lower_{\max}} = \frac{R_{VINhigh}}{\frac{4}{3 \times \pi} \times \frac{2}{V_{VIN_{ripple-max}}} \times V_{AC-min} \times \sqrt[2]{2} - 1} = 30.8 \, k\Omega$$

(56)

$$C_{VIN-MIN} = \begin{pmatrix} 2 \sqrt{\frac{1}{Z_{lower_{\max}}^2} - \frac{1}{R_{VINlow}^2}} \\ \frac{2 \times \pi \times 2 \times f_{AC}}{2 \times \pi \times 2 \times f_{AC}} \end{pmatrix} = 35.3 \, nF$$

$$(57)$$

A maximum allowed VIN pin capacitance permissible ( $C_{VIN-MAX}$ ) allowing for proper AC-line detection should also be calculated. This value is determined as the  $C_{VIN-MIN}$  was, but now using the maximum AC-line voltage (305 V AC).

The voltage at the VIN pin  $V_{VINAVG}$  should be smaller than the  $V_{VINOVP}$  = 2 V that was the case for 305 V AC.

The worst case for ripple detection is at high-line and should be greater than 0.313 V.

The calculation results in:

$$V_{VIN_{AVG}} = V_{AC,max} \times n \times \frac{R_{VINlow}}{R_{VINhigh} + R_{VINlow}}$$

(58)

$$V_{VIN_{AVG}} = 305 V \times 0.9 \times \frac{39 k\Omega}{5.8 M\Omega + 39 k\Omega} = 1.83 V$$

$$V_{VIN_{ripple-\min}} = 0.313 V \tag{59}$$

This value is an IC parameter.

Using the complex voltage divider, the maximum capacitor size for these resistors can now be calculated:

$$Z_{lower_{\min}} = \frac{R_{VINhigh}}{\frac{4}{3 \times \pi} \times \frac{2}{V_{VIN_{ripple-\min}}} \times V_{AC,max} \times \sqrt[2]{2} - 1} = 4.6 \ k\Omega$$

(60)

$$C_{VIN-max} = \begin{pmatrix} 2 \sqrt{\frac{1}{Z_{lower_{\min}}^2} - \frac{1}{R_{-}VINlow^2}} \\ \frac{1}{2 \times \pi \times 2 \times f_{AC}} \end{pmatrix} = 262.9 \, nF$$

(61)

### ICL88xx flyback design guide For high power factor flyback converter with constant voltage output

PFC flyback converter design

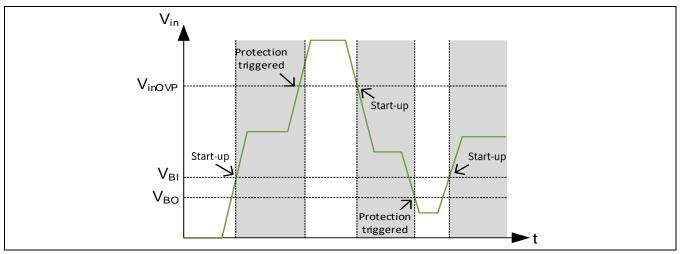

Figure 15 Input voltage levels for start-up and protection

If the capacitor is larger than the calculated value, there is the risk that the IC detects DC at high input voltages. This may cause a bad THD at PF, because the QR operation gets lost.

For ICL8820, the IC starts to introduce the jitter pattern to the otherwise constant operating frequency.

#### Fast restart

The VIN pin offers an additional fast restart feature. Where the normal restart takes 200 ms after a protection is triggered, the fast restart checks the start-up conditions every 25 ms as long as a  $V_{cc}$  is available.

This feature might be useful to turn the IC off for very low standby applications with additional auxiliary power supply. In this case, the response time to start-up is largely decreased from the worst-case 200 ms + start-up time to just 25 ms + start-up time.

$R_{BO1}$  = 5.8 M $\Omega$  can be used for the first start-up of the board. Later optimization showed that a value of 6.31 M $\Omega$  is better suited to this board.

### 3.7 On-time adjustment

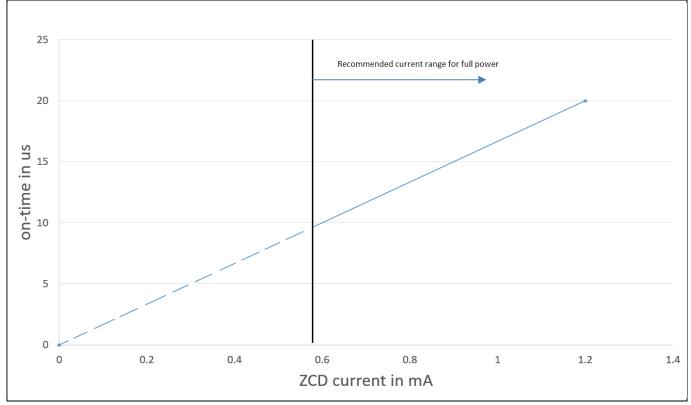

To limit the maximum power delivery at low AC-line input voltages, the ICL88xx limits the maximum on-time. This is accomplished with the resistor connecting the ZCD pin and the auxiliary winding. The on-time has a linear relationship to the current flowing in the pin, which is displayed in **Figure 16**. To get the best performance, it is advisable to design the on-time to be greater than 10 µs.

Figure 16 ZCD current vs. on-time

Maximum on-time for this design was calculated in chapter **3.1** (12.2  $\mu$ s).

Where:

- $V_{\text{ZCDClamp}} = 55 \text{ mV}$

- $ZCD_{coeff} = 60 \text{ A/s}$

According to the calculation, gate pulses with 12.2  $\mu$ s are needed at 90 V and 800 mA. To generate these, the ZCD signal must have more than 0.7 mA peak-to-peak.

The aux voltage is:

$$V_{a_{pk}} \times \frac{N_{A,SEC}}{N_{prim}} = V_{auxneg}$$

(62)

$$V_{auxneg} = 90 V \times \sqrt{2} \times \frac{3}{32} = 11.9 V$$

in the negative direction, and:

$$(V_{out} + V_d) \times \frac{N_a}{N_{sec}} = V_{auxpos}$$

(63)

$V_{auxpos} = (52 V + 0.7 V) \times \frac{3}{10} = 15.81 V$

in the positive direction.

The peak-to-peak voltage is 28.3 V. For a ZCD current of 0.6 mA peak-to-peak, the ZCD resistor may have a maximum of:

$$\frac{V_{auxpkpk}}{I_{ZCD}} = R_{ZCDmax}$$

$$R_{ZCDmax} = \frac{27.7 V}{0.6 mA} = 42 k\Omega$$

(64)

Margin should be considered when setting the maximum on-time (selecting resistor  $R_{zcD}$ ). This takes into account abrupt AC-line and load changes, and ensures quick start-up.

Based on bench analysis, 15 percent margin on maximum on-time leads to good and stable results.

If resistor R<sub>zcD</sub> is selected to be too large, during certain operating conditions the output voltage may decrease enough to cause slow start-up times or possibly initiate multiple start/restart sequences.

With 15 percent margin added to the maximum on-time, the resistor is selected:  $R_{ZCD}$  = 33 k $\Omega$ .

With  $R_{ZCD}$  = 33 k $\Omega$  on the ZCD pin, there was still some reserve for the maximum pulse width.

The limit for the lowest  $R_{ZCD}$  is given by the maximum current and on-time handling capability of the ZCD pin. Inside the IC a deterioration of the THD due to too-high negative ZCD current occurs from approx. 2.5 mA; at 125°C it is approximately 1.8 mA.

At 300 V AC, the aux voltage in the negative direction is:

$$V_{AC,max,pk} \times \frac{N_a}{N_p} = V_{auxnegmax}$$

Design Guide

(65)

(66)

$$V_{auxnegmax} = 300 V \times \sqrt{2} \times \frac{3}{32} = 39.8 V$$

To stay below 1.8 mA, the  $R_{ZCD}$  must be at least:

$$\frac{V_{aux,pkpk}}{I_{ZCD}} = R_{ZCDmin}$$

For 1.8 mA:

$$R_{ZCDmin} = \frac{39.8 \, V}{1.8 \, mA} = 22 \, k\Omega \tag{67}$$

For 2.5 mA:

$$R_{ZCDmin} = \frac{39.8 \, V}{2.5 \, mA} = 16 \, k\Omega \tag{68}$$

Given these two conditions, the ZCD resistor may be selected without restriction between 22 k $\Omega$  and 33 k $\Omega$ .

#### Trade-off between power limitation and operating point

The on-time of the ICL88xx family of devices is determined by the current out of the ZCD pin and the  $R_{ZCD}$  resistor selected as described above. The  $R_{ZCD}$  value also affects the operating point of the system. To be clearer, the value of  $R_{ZCD}$  will have an effect on what valley number the converter uses to turn on the main power MOSFET.

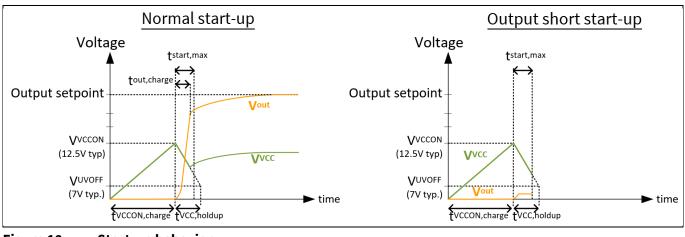

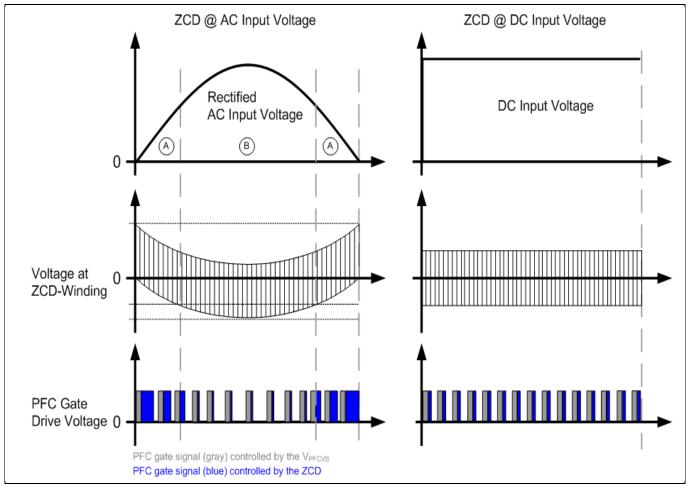

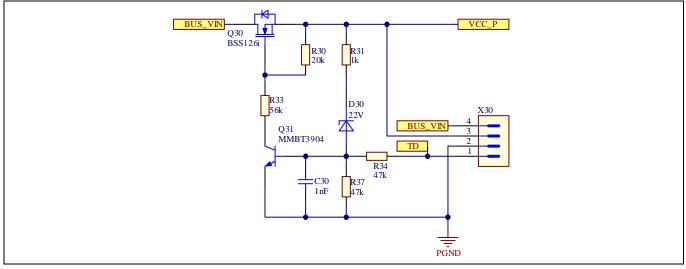

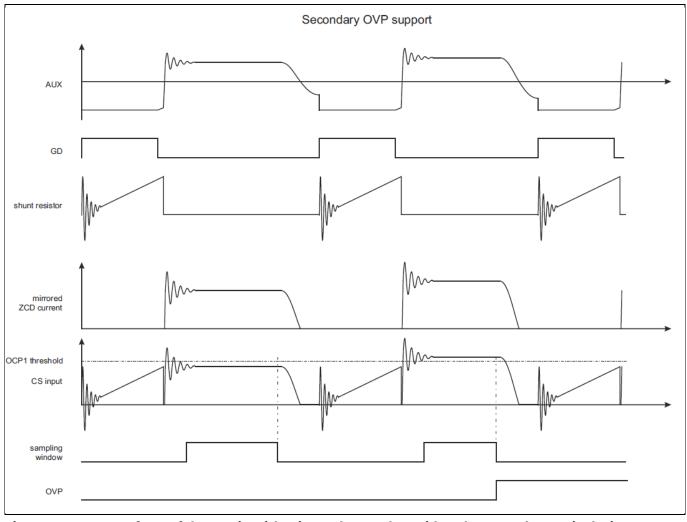

As the value of resistor  $R_{zcD}$  reduces, the ICL88xx moves to a higher valley number earlier. Bench analysis has shown the best trade-off between THD, power limitation and performance is achieved with a smaller  $R_{zcD}$  than initially calculated. This is due to shorter gate pulses being avoided.