protocols. Visit the Altera IP MegaStore at [www.altera.com](http://www.altera.com) to download IP MegaCore functions.

- Nios II Embedded Processor support

The Cyclone II family offers devices with the Fast-On feature, which offers a faster power-on-reset (POR) time. Devices that support the Fast-On feature are designated with an “A” in the device ordering code. For example, EP2C5A, EP2C8A, EP2C15A, and EP2C20A. The EP2C5A is only available in the automotive speed grade. The EP2C8A and EP2C20A are only available in the industrial speed grade. The EP2C15A is only available with the Fast-On feature and is available in both commercial and industrial grades. The Cyclone II “A” devices are identical in feature set and functionality to the non-A devices except for support of the faster POR time.

Cyclone II A devices are offered in automotive speed grade. For more information, refer to the Cyclone II section in the *Automotive-Grade Device Handbook*.

For more information on POR time specifications for Cyclone II A and non-A devices, refer to the *Hot Socketing & Power-On Reset* chapter in the *Cyclone II Device Handbook*.

Table 1–1 lists the Cyclone II device family features. Table 1–2 lists the Cyclone II device package offerings and maximum user I/O pins.

| <b>Table 1–1. Cyclone II FPGA Family Features (Part 1 of 2)</b> |           |           |            |            |         |         |           |

|-----------------------------------------------------------------|-----------|-----------|------------|------------|---------|---------|-----------|

| Feature                                                         | EP2C5 (2) | EP2C8 (2) | EP2C15 (1) | EP2C20 (2) | EP2C35  | EP2C50  | EP2C70    |

| LEs                                                             | 4,608     | 8,256     | 14,448     | 18,752     | 33,216  | 50,528  | 68,416    |

| M4K RAM blocks (4 Kbits plus 512 parity bits)                   | 26        | 36        | 52         | 52         | 105     | 129     | 250       |

| Total RAM bits                                                  | 119,808   | 165,888   | 239,616    | 239,616    | 483,840 | 594,432 | 1,152,000 |

| Embedded multipliers (3)                                        | 13        | 18        | 26         | 26         | 35      | 86      | 150       |

| PLLs                                                            | 2         | 2         | 4          | 4          | 4       | 4       | 4         |

| Feature               | EP2C5 (2) | EP2C8 (2) | EP2C15 (1) | EP2C20 (2) | EP2C35 | EP2C50 | EP2C70 |

|-----------------------|-----------|-----------|------------|------------|--------|--------|--------|

| Maximum user I/O pins | 158       | 182       | 315        | 315        | 475    | 450    | 622    |

**Notes to Table 1–1:**

- (1) The EP2C15A is only available with the Fast On feature, which offers a faster POR time. This device is available in both commercial and industrial grade.

- (2) The EP2C5, EP2C8, and EP2C20 optionally support the Fast On feature, which is designated with an “A” in the device ordering code. The EP2C5A is only available in the automotive speed grade. The EP2C8A and EP2C20A devices are only available in industrial grade.

- (3) This is the total number of  $18 \times 18$  multipliers. For the total number of  $9 \times 9$  multipliers per device, multiply the total number of  $18 \times 18$  multipliers by 2.

| Device           | 144-Pin  | 208-Pin  | 240-Pin | 256-Pin      | 484-Pin      | 484-Pin            | 672-Pin      | 896-Pin      |

|------------------|----------|----------|---------|--------------|--------------|--------------------|--------------|--------------|

|                  | TQFP (3) | PQFP (4) | PQFP    | FineLine BGA | FineLine BGA | Ultra FineLine BGA | FineLine BGA | FineLine BGA |

| EP2C5 (6) (8)    | 89       | 142      | —       | 158 (5)      | —            | —                  | —            | —            |

| EP2C8 (6)        | 85       | 138      | —       | 182          | —            | —                  | —            | —            |

| EP2C8A (6), (7)  | —        | —        | —       | 182          | —            | —                  | —            | —            |

| EP2C15A (6), (7) | —        | —        | —       | 152          | 315          | —                  | —            | —            |

| EP2C20 (6)       | —        | —        | 142     | 152          | 315          | —                  | —            | —            |

| EP2C20A (6), (7) | —        | —        | —       | 152          | 315          | —                  | —            | —            |

| EP2C35 (6)       | —        | —        | —       | —            | 322          | 322                | 475          | —            |

| EP2C50 (6)       | —        | —        | —       | —            | 294          | 294                | 450          | —            |

| EP2C70 (6)       | —        | —        | —       | —            | —            | —                  | 422          | 622          |

**Notes to Table 1-2:**

- (1) Cyclone II devices support vertical migration within the same package (for example, you can migrate between the EP2C20 device in the 484-pin FineLine BGA package and the EP2C35 and EP2C50 devices in the same package).

- (2) The Quartus® II software I/O pin counts include four additional pins, TDI, TDO, TMS, and TCK, which are not available as general purpose I/O pins.

- (3) TQFP: thin quad flat pack.

- (4) PQFP: plastic quad flat pack.

- (5) Vertical migration is supported between the EP2C5F256 and the EP2C8F256 devices. However, not all of the DQ and DQS groups are supported. Vertical migration between the EP2C5 and the EP2C15 in the F256 package is not supported.

- (6) The I/O pin counts for the EP2C5, EP2C8, and EP2C15A devices include 8 dedicated clock pins that can be used for data inputs. The I/O counts for the EP2C20, EP2C35, EP2C50, and EP2C70 devices include 16 dedicated clock pins that can be used for data inputs.

- (7) EP2C8A, EP2C15A, and EP2C20A have a Fast On feature that has a faster POR time. The EP2C15A is only available with the Fast On option.

- (8) The EP2C5 optionally support the Fast On feature, which is designated with an "A" in the device ordering code. The EP2C5A is only available in the automotive speed grade. Refer to the Cyclone II section in the *Automotive-Grade Device Handbook*.

Cyclone II devices support vertical migration within the same package (for example, you can migrate between the EP2C35, EP2C50, and EP2C70 devices in the 672-pin FineLine BGA package). The exception to vertical migration support within the Cyclone II family is noted in Table 1-3.

Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities.

**Table 1-3. Total Number of Non-Migratable I/O Pins for Cyclone II Vertical Migration Paths**

| Vertical Migration Path | 144-Pin TQFP | 208-Pin PQFP | 256-Pin FineLine BGA<br>(1) | 484-Pin FineLine BGA<br>(2) | 484-Pin Ultra FineLine BGA | 672-Pin FineLine BGA<br>(3) |

|-------------------------|--------------|--------------|-----------------------------|-----------------------------|----------------------------|-----------------------------|

| EP2C5 to EP2C8          | 4            | 4            | 1 (4)                       | —                           | —                          | —                           |

| EP2C8 to EP2C15         | —            | —            | 30                          | —                           | —                          | —                           |

| EP2C15 to EP2C20        | —            | —            | 0                           | 0                           | —                          | —                           |

| EP2C20 to EP2C35        |              | —            | —                           | 16                          | —                          | —                           |

| EP2C35 to EP2C50        | —            | —            | —                           | 28                          | 28 (5)                     | 28                          |

| EP2C50 to EP2C70        | —            | —            | —                           | —                           | 28                         | 28                          |

*Notes to Table 1-3:*

- (1) Vertical migration between the EP2C5F256 to the EP2C15AF256 and the EP2C5F256 to the EP2C20F256 devices is not supported.

- (2) When migrating from the EP2C20F484 device to the EP2C50F484 device, a total of 39 I/O pins are non-migratable.

- (3) When migrating from the EP2C35F672 device to the EP2C70F672 device, a total of 56 I/O pins are non-migratable.

- (4) In addition to the one non-migratable I/O pin, there are 34 DQ pins that are non-migratable.

- (5) The pinouts of 484 FBGA and 484 UBGA are the same.

When moving from one density to a larger density, I/O pins are often lost because of the greater number of power and ground pins required to support the additional logic within the larger device. For I/O pin migration across densities, you must cross reference the available I/O pins using the device pin-outs for all planned densities of a given package type to identify which I/O pins are migratable.

To ensure that your board layout supports migratable densities within one package offering, enable the applicable vertical migration path within the Quartus II software (go to Assignments menu, then Device, then click the **Migration Devices** button). After compilation, check the information messages for a full list of I/O, DQ, LVDS, and other pins that are not available because of the selected migration path. Table 1-3 lists the Cyclone II device package offerings and shows the total number of non-migratable I/O pins when migrating from one density device to a larger density device.

Cyclone II devices are available in up to three speed grades:  $-6$ ,  $-7$ , and  $-8$ , with  $-6$  being the fastest. [Table 1-4](#) shows the Cyclone II device speed-grade offerings.

| <b>Table 1-4. Cyclone II Device Speed Grades</b> |              |              |              |                      |                      |                            |                      |                      |

|--------------------------------------------------|--------------|--------------|--------------|----------------------|----------------------|----------------------------|----------------------|----------------------|

| Device                                           | 144-Pin TQFP | 208-Pin PQFP | 240-Pin PQFP | 256-Pin FineLine BGA | 484-Pin FineLine BGA | 484-Pin Ultra FineLine BGA | 672-Pin FineLine BGA | 896-Pin FineLine BGA |

| EP2C5 <a href="#">(1)</a>                        | $-6, -7, -8$ | $-7, -8$     | —            | $-6, -7, -8$         | —                    | —                          | —                    | —                    |

| EP2C8                                            | $-6, -7, -8$ | $-7, -8$     | —            | $-6, -7, -8$         | —                    | —                          | —                    | —                    |

| EP2C8A <a href="#">(2)</a>                       | —            | —            | —            | $-8$                 | —                    | —                          | —                    | —                    |

| EP2C15A                                          | —            | —            | —            | $-6, -7, -8$         | $-6, -7, -8$         | —                          | —                    | —                    |

| EP2C20                                           | —            | —            | $-8$         | $-6, -7, -8$         | $-6, -7, -8$         | —                          | —                    | —                    |

| EP2C20A <a href="#">(2)</a>                      | —            | —            | —            | $-8$                 | $-8$                 | —                          | —                    | —                    |

| EP2C35                                           | —            | —            | —            | —                    | $-6, -7, -8$         | $-6, -7, -8$               | $-6, -7, -8$         | —                    |

| EP2C50                                           | —            | —            | —            | —                    | $-6, -7, -8$         | $-6, -7, -8$               | $-6, -7, -8$         | —                    |

| EP2C70                                           | —            | —            | —            | —                    | —                    | —                          | $-6, -7, -8$         | $-6, -7, -8$         |

*Notes to Table 1-4:*

- (1) The EP2C5 optionally support the Fast On feature, which is designated with an "A" in the device ordering code. The EP2C5A is only available in the automotive speed grade. Refer to the Cyclone II section in the [Automotive-Grade Device Handbook](#) for detailed information.

- (2) EP2C8A and EP2C20A are only available in industrial grade.

Each global clock network has a clock control block to select from a number of input clock sources (PLL clock outputs, CLK [] pins, DPCLK [] pins, and internal logic) to drive onto the global clock network. [Table 2–2](#) lists how many PLLs, CLK [] pins, DPCLK [] pins, and global clock networks are available in each Cyclone II device. CLK [] pins are dedicated clock pins and DPCLK [] pins are dual-purpose clock pins.

**Table 2–2. Cyclone II Device Clock Resources**

| Device | Number of PLLs | Number of CLK Pins | Number of DPCLK Pins | Number of Global Clock Networks |

|--------|----------------|--------------------|----------------------|---------------------------------|

| EP2C5  | 2              | 8                  | 8                    | 8                               |

| EP2C8  | 2              | 8                  | 8                    | 8                               |

| EP2C15 | 4              | 16                 | 20                   | 16                              |

| EP2C20 | 4              | 16                 | 20                   | 16                              |

| EP2C35 | 4              | 16                 | 20                   | 16                              |

| EP2C50 | 4              | 16                 | 20                   | 16                              |

| EP2C70 | 4              | 16                 | 20                   | 16                              |

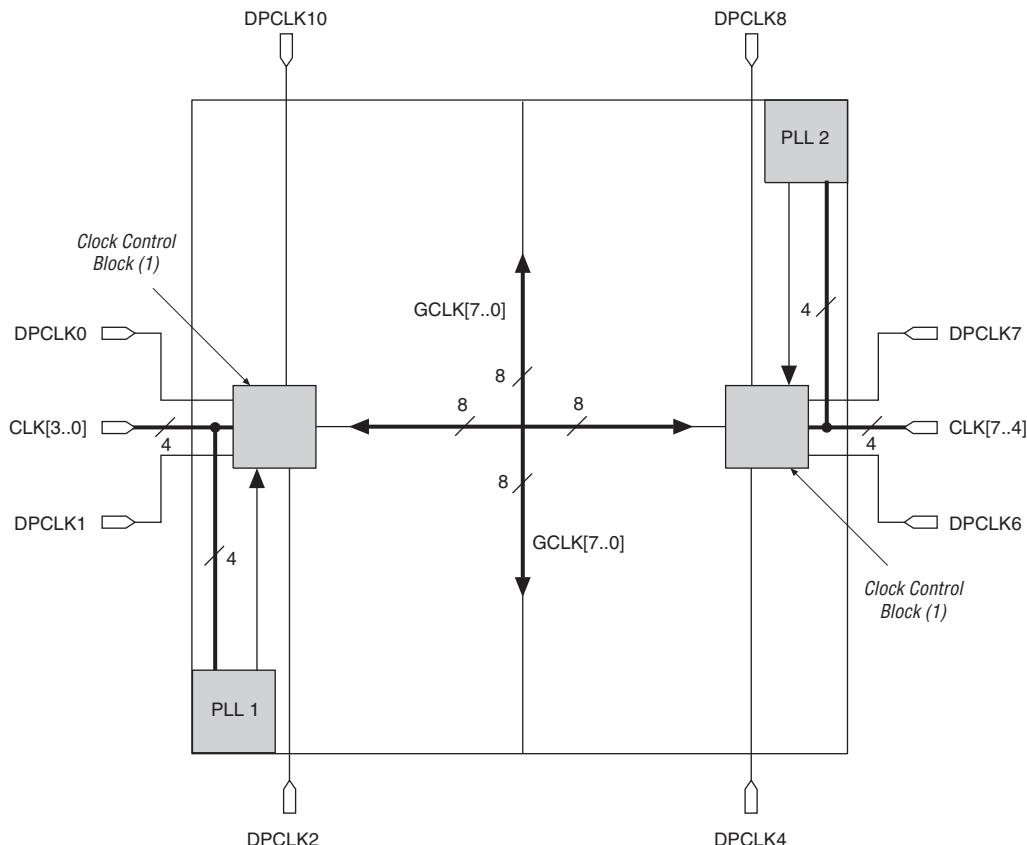

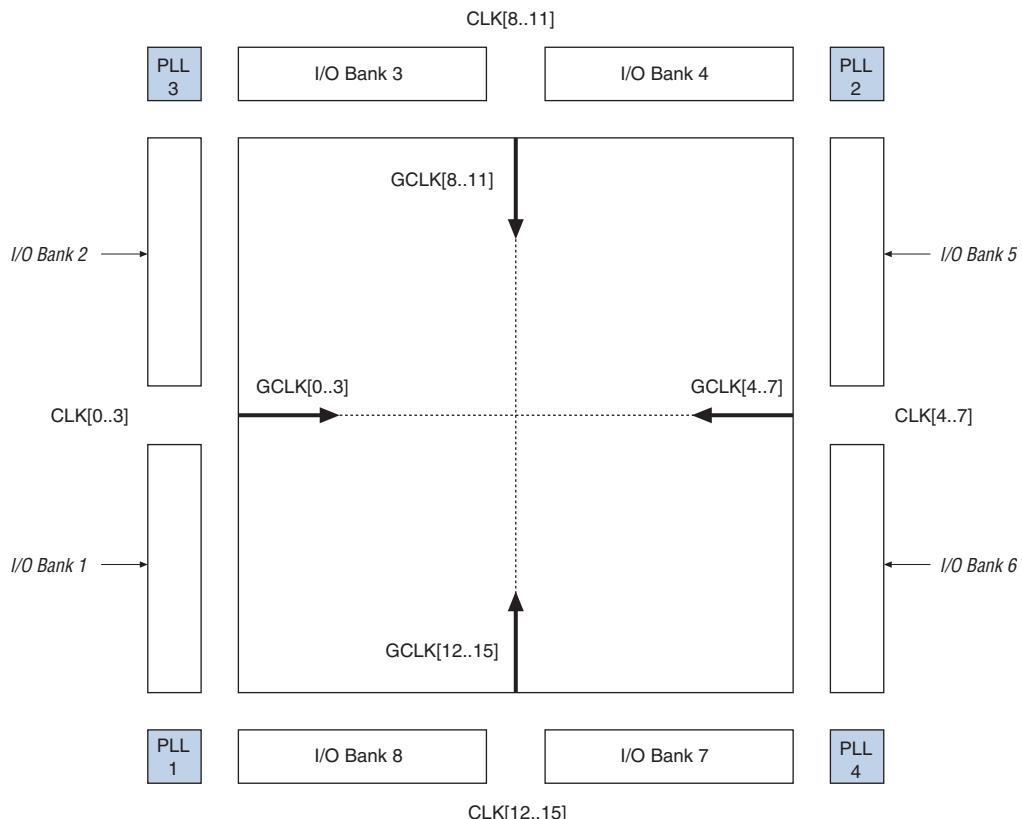

[Figures 2–11](#) and [2–12](#) show the location of the Cyclone II PLLs, CLK [] inputs, DPCLK [] pins, and clock control blocks.

Figure 2-11. EP2C5 &amp; EP2C8 PLL, CLK[], DPCLK[] &amp; Clock Control Block Locations

*Note to Figure 2-11:*

- (1) There are four clock control blocks on each side.

## Dedicated Clock Pins

Larger Cyclone II devices (EP2C15 and larger devices) have 16 dedicated clock pins ( $\text{CLK}[15 \dots 0]$ , four pins on each side of the device). Smaller Cyclone II devices (EP2C5 and EP2C8 devices) have eight dedicated clock pins ( $\text{CLK}[7 \dots 0]$ , four pins on left and right sides of the device). These  $\text{CLK}$  pins drive the global clock network (GCLK), as shown in [Figures 2-11](#) and [2-12](#).

If the dedicated clock pins are not used to feed the global clock networks, they can be used as general-purpose input pins to feed the logic array using the MultiTrack interconnect. However, if they are used as general-purpose input pins, they do not have support for an I/O register and must use LE-based registers in place of an I/O register.

## Dual-Purpose Clock Pins

Cyclone II devices have either 20 dual-purpose clock pins,  $\text{DPCLK}[19 \dots 0]$  or 8 dual-purpose clock pins,  $\text{DPCLK}[7 \dots 0]$ . In the larger Cyclone II devices (EP2C15 devices and higher), there are 20  $\text{DPCLK}$  pins; four on the left and right sides and six on the top and bottom of the device. The corner  $\text{CDPCLK}$  pins are first multiplexed before they drive into the clock control block. Since the signals pass through a multiplexer before feeding the clock control block, these signals incur more delay to the clock control block than other  $\text{DPCLK}$  pins that directly feed the clock control block. In the smaller Cyclone II devices (EP2C5 and EP2C8 devices), there are eight  $\text{DPCLK}$  pins; two on each side of the device (see [Figures 2-11](#) and [2-12](#)).

A programmable delay chain is available from the  $\text{DPCLK}$  pin to its fan-out destinations. To set the propagation delay from the  $\text{DPCLK}$  pin to its fan-out destinations, use the **Input Delay from Dual-Purpose Clock Pin to Fan-Out Destinations** assignment in the Quartus II software.

These dual-purpose pins can connect to the global clock network for high-fanout control signals such as clocks, asynchronous clears, presets, and clock enables, or protocol control signals such as  $\text{TRDY}$  and  $\text{IRDY}$  for PCI, or  $\text{DQS}$  signals for external memory interfaces.

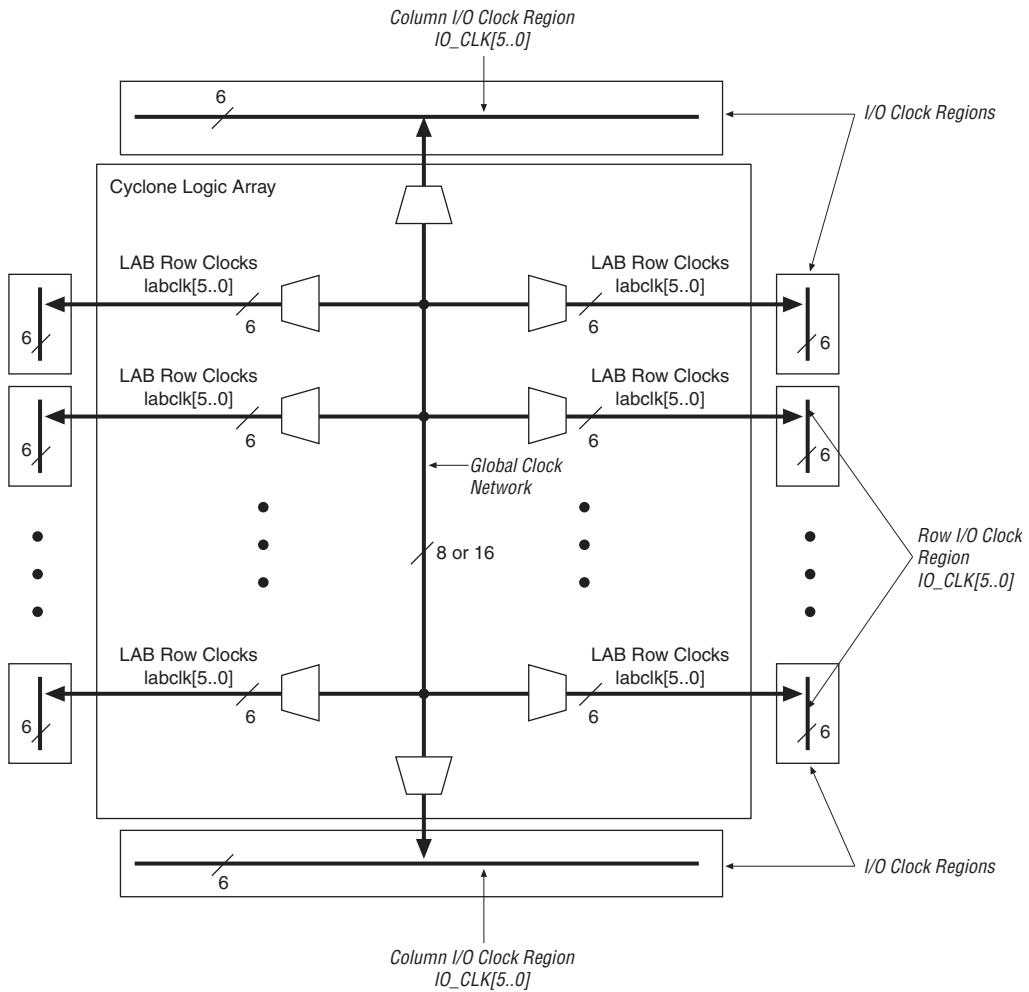

## Global Clock Network

The 16 or 8 global clock networks drive throughout the entire device. Dedicated clock pins (CLK [ ]), PLL outputs, the logic array, and dual-purpose clock (DPCLK [ ]) pins can also drive the global clock network.

The global clock network can provide clocks for all resources within the device, such as IOEs, LEs, memory blocks, and embedded multipliers. The global clock lines can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin, or DQS signals for DDR SDRAM or QDRII SRAM interfaces. Internal logic can also drive the global clock network for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fan-out.

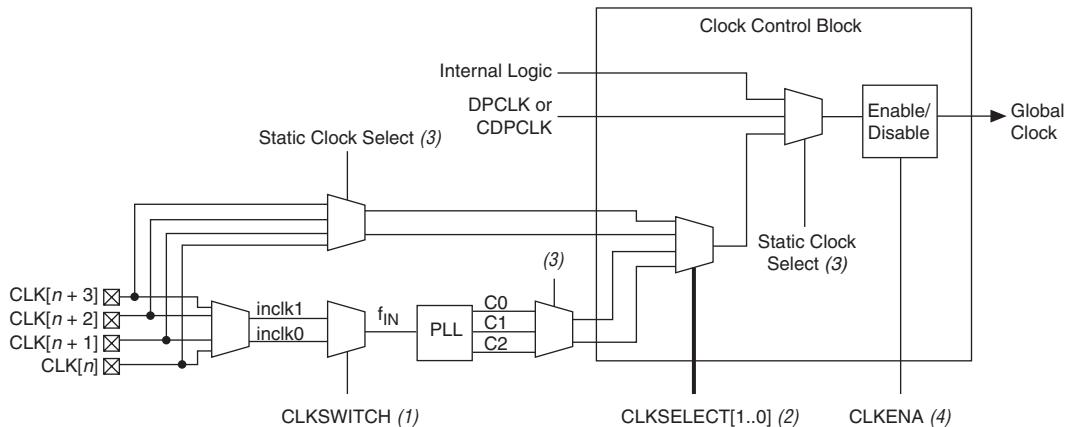

### *Clock Control Block*

There is a clock control block for each global clock network available in Cyclone II devices. The clock control blocks are arranged on the device periphery and there are a maximum of 16 clock control blocks available per Cyclone II device. The larger Cyclone II devices (EP2C15 devices and larger) have 16 clock control blocks, four on each side of the device. The smaller Cyclone II devices (EP2C5 and EP2C8 devices) have eight clock control blocks, four on the left and right sides of the device.

The control block has these functions:

- Dynamic global clock network clock source selection

- Dynamic enable/disable of the global clock network

In Cyclone II devices, the dedicated CLK [ ] pins, PLL counter outputs, DPCLK [ ] pins, and internal logic can all feed the clock control block. The output from the clock control block in turn feeds the corresponding global clock network.

The following sources can be inputs to a given clock control block:

- Four clock pins on the same side as the clock control block

- Three PLL clock outputs from a PLL

- Four DPCLK pins (including CDCLK pins) on the same side as the clock control block

- Four internally-generated signals

Figure 2-15. LAB &amp; I/O Clock Regions

For more information on the global clock network and the clock control block, see the *PLLs in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

## PLLs

Cyclone II PLLs provide general-purpose clocking as well as support for the following features:

- Clock multiplication and division

- Phase shifting

- Programmable duty cycle

- Up to three internal clock outputs

- One dedicated external clock output

- Clock outputs for differential I/O support

- Manual clock switchover

- Gated lock signal

- Three different clock feedback modes

- Control signals

Cyclone II devices contain either two or four PLLs. [Table 2–3](#) shows the PLLs available for each Cyclone II device.

**Table 2–3. Cyclone II Device PLL Availability**

| Device | PLL1 | PLL2 | PLL3 | PLL4 |

|--------|------|------|------|------|

| EP2C5  | ✓    | ✓    |      |      |

| EP2C8  | ✓    | ✓    |      |      |

| EP2C15 | ✓    | ✓    | ✓    | ✓    |

| EP2C20 | ✓    | ✓    | ✓    | ✓    |

| EP2C35 | ✓    | ✓    | ✓    | ✓    |

| EP2C50 | ✓    | ✓    | ✓    | ✓    |

| EP2C70 | ✓    | ✓    | ✓    | ✓    |

Each M4K block can implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and first-in first-out (FIFO) buffers. The M4K blocks support the following features:

- 4,608 RAM bits

- 250-MHz performance

- True dual-port memory

- Simple dual-port memory

- Single-port memory

- Byte enable

- Parity bits

- Shift register

- FIFO buffer

- ROM

- Various clock modes

- Address clock enable

Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

Table 2–5 shows the capacity and distribution of the M4K memory blocks in each Cyclone II device.

**Table 2–5. M4K Memory Capacity & Distribution in Cyclone II Devices**

| Device | M4K Columns | M4K Blocks | Total RAM Bits |

|--------|-------------|------------|----------------|

| EP2C5  | 2           | 26         | 119,808        |

| EP2C8  | 2           | 36         | 165,888        |

| EP2C15 | 2           | 52         | 239,616        |

| EP2C20 | 2           | 52         | 239,616        |

| EP2C35 | 3           | 105        | 483,840        |

| EP2C50 | 3           | 129        | 594,432        |

| EP2C70 | 5           | 250        | 1,152,000      |

Embedded multipliers can operate at up to 250 MHz (for the fastest speed grade) for  $18 \times 18$  and  $9 \times 9$  multiplications when using both input and output registers.

Each Cyclone II device has one to three columns of embedded multipliers that efficiently implement multiplication functions. An embedded multiplier spans the height of one LAB row. Table 2–10 shows the number of embedded multipliers in each Cyclone II device and the multipliers that can be implemented.

| <b>Table 2–10. Number of Embedded Multipliers in Cyclone II Devices</b> |                                    |                             | <i>Note (1)</i>                            |                                              |

|-------------------------------------------------------------------------|------------------------------------|-----------------------------|--------------------------------------------|----------------------------------------------|

| <b>Device</b>                                                           | <b>Embedded Multiplier Columns</b> | <b>Embedded Multipliers</b> | <b><math>9 \times 9</math> Multipliers</b> | <b><math>18 \times 18</math> Multipliers</b> |

| EP2C5                                                                   | 1                                  | 13                          | 26                                         | 13                                           |

| EP2C8                                                                   | 1                                  | 18                          | 36                                         | 18                                           |

| EP2C15                                                                  | 1                                  | 26                          | 52                                         | 26                                           |

| EP2C20                                                                  | 1                                  | 26                          | 52                                         | 26                                           |

| EP2C35                                                                  | 1                                  | 35                          | 70                                         | 35                                           |

| EP2C50                                                                  | 2                                  | 86                          | 172                                        | 86                                           |

| EP2C70                                                                  | 3                                  | 150                         | 300                                        | 150                                          |

**Note to Table 2–10:**

(1) Each device has either the number of  $9 \times 9$ - or  $18 \times 18$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

The embedded multiplier consists of the following elements:

- Multiplier block

- Input and output registers

- Input and output interfaces

Figure 2–18 shows the multiplier block architecture.

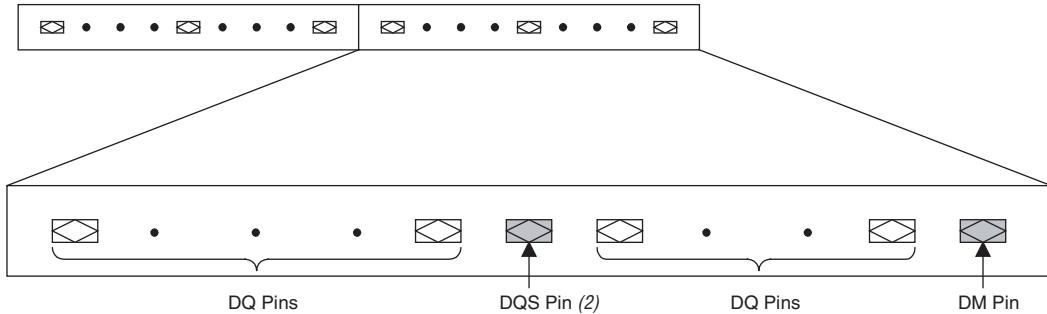

Figure 2–26. Cyclone II Device DQ & DQS Groups in  $\times 8/\times 9$  Mode Notes (1), (2)

## Notes to Figure 2–26:

- (1) Each DQ group consists of a DQS pin, DM pin, and up to nine DQ pins.

- (2) This is an idealized pin layout. For actual pin layout, refer to the pin table.

Cyclone II devices support the data strobe or read clock signal (DQS) used in DDR and DDR2 SDRAM. Cyclone II devices can use either bidirectional data strobes or unidirectional read clocks. The dedicated external memory interface in Cyclone II devices also includes programmable delay circuitry that can shift the incoming DQS signals to center align the DQS signals within the data window.

The DQS signal is usually associated with a group of data (DQ) pins. The phase-shifted DQS signals drive the global clock network, which is used to clock the DQ signals on internal LE registers.

Table 2–15 shows the number of DQ pin groups per device.

Table 2–15. Cyclone II DQS &amp; DQ Bus Mode Support (Part 1 of 2) Note (1)

| Device | Package               | Number of $\times 8$ Groups | Number of $\times 9$ Groups (5), (6) | Number of $\times 16$ Groups | Number of $\times 18$ Groups (5), (6) |

|--------|-----------------------|-----------------------------|--------------------------------------|------------------------------|---------------------------------------|

| EP2C5  | 144-pin TQFP (2)      | 3                           | 3                                    | 0                            | 0                                     |

|        | 208-pin PQFP          | 7 (3)                       | 4                                    | 3                            | 3                                     |

| EP2C8  | 144-pin TQFP (2)      | 3                           | 3                                    | 0                            | 0                                     |

|        | 208-pin PQFP          | 7 (3)                       | 4                                    | 3                            | 3                                     |

|        | 256-pin FineLine BGA® | 8 (3)                       | 4                                    | 4                            | 4                                     |

| EP2C15 | 256-pin FineLine BGA  | 8                           | 4                                    | 4                            | 4                                     |

|        | 484-pin FineLine BGA  | 16 (4)                      | 8                                    | 8                            | 8                                     |

| EP2C20 | 256-pin FineLine BGA  | 8                           | 4                                    | 4                            | 4                                     |

|        | 484-pin FineLine BGA  | 16 (4)                      | 8                                    | 8                            | 8                                     |

| <b>Table 2–15. Cyclone II DQS &amp; DQ Bus Mode Support (Part 2 of 2) <i>Note (1)</i></b> |                      |                                               |                                                        |                                                |                                                         |

|-------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------|--------------------------------------------------------|------------------------------------------------|---------------------------------------------------------|

| <b>Device</b>                                                                             | <b>Package</b>       | <b>Number of <math>\times 8</math> Groups</b> | <b>Number of <math>\times 9</math> Groups (5), (6)</b> | <b>Number of <math>\times 16</math> Groups</b> | <b>Number of <math>\times 18</math> Groups (5), (6)</b> |

| EP2C35                                                                                    | 484-pin FineLine BGA | 16 (4)                                        | 8                                                      | 8                                              | 8                                                       |

|                                                                                           | 672-pin FineLine BGA | 20 (4)                                        | 8                                                      | 8                                              | 8                                                       |

| EP2C50                                                                                    | 484-pin FineLine BGA | 16 (4)                                        | 8                                                      | 8                                              | 8                                                       |

|                                                                                           | 672-pin FineLine BGA | 20 (4)                                        | 8                                                      | 8                                              | 8                                                       |

| EP2C70                                                                                    | 672-pin FineLine BGA | 20 (4)                                        | 8                                                      | 8                                              | 8                                                       |

|                                                                                           | 896-pin FineLine BGA | 20 (4)                                        | 8                                                      | 8                                              | 8                                                       |

**Notes to Table 2–15:**

- (1) Numbers are preliminary.

- (2) EP2C5 and EP2C8 devices in the 144-pin TQFP package do not have any DQ pin groups in I/O bank 1.

- (3) Because of available clock resources, only a total of 6 DQ/DQS groups can be implemented.

- (4) Because of available clock resources, only a total of 14 DQ/DQS groups can be implemented.

- (5) The  $\times 9$  DQS/DQ groups are also used as  $\times 8$  DQS/DQ groups. The  $\times 18$  DQS/DQ groups are also used as  $\times 16$  DQS/DQ groups.

- (6) For QDRI implementation, if you connect the D ports (write data) to the Cyclone II DQ pins, the total available  $\times 9$  DQS /DQ and  $\times 18$  DQS/DQ groups are half of that shown in [Table 2–15](#).

You can use any of the DQ pins for the parity pins in Cyclone II devices. The Cyclone II device family supports parity in the  $\times 8/\times 9$ , and  $\times 16/\times 18$  mode. There is one parity bit available per eight bits of data pins.

The data mask, DM, pins are required when writing to DDR SDRAM and DDR2 SDRAM devices. A low signal on the DM pin indicates that the write is valid. If the DM signal is high, the memory masks the DQ signals. In Cyclone II devices, the DM pins are assigned and are the preferred pins. Each group of DQS and DQ signals requires a DM pin.

When using the Cyclone II I/O banks to interface with the DDR memory, at least one PLL with two clock outputs is needed to generate the system and write clock. The system clock is used to clock the DQS write signals, commands, and addresses. The write clock is shifted by  $-90^\circ$  from the system clock and is used to clock the DQ signals during writes.

[Figure 2–27](#) illustrates DDR SDRAM interfacing from the I/O through the dedicated circuitry to the logic array.

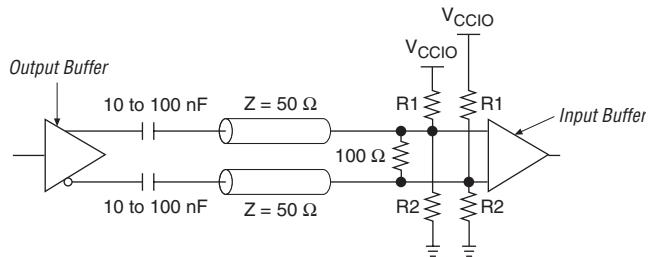

The reduced swing differential signaling (RSDS) and mini-LVDS standards are derivatives of the LVDS standard. The RSDS and mini-LVDS I/O standards are similar in electrical characteristics to LVDS, but have a smaller voltage swing and therefore provide increased power benefits and reduced electromagnetic interference (EMI). Cyclone II devices support the RSDS and mini-LVDS I/O standards at data rates up to 311 Mbps at the transmitter.

A subset of pins in each I/O bank (on both rows and columns) support the high-speed I/O interface. The dual-purpose LVDS pins require an external-resistor network at the transmitter channels in addition to  $100\text{-}\Omega$  termination resistors on receiver channels. These pins do not contain dedicated serialization or deserialization circuitry. Therefore, internal logic performs serialization and deserialization functions.

Cyclone II pin tables list the pins that support the high-speed I/O interface. The number of LVDS channels supported in each device family member is listed in [Table 2–18](#).

**Table 2–18. Cyclone II Device LVDS Channels (Part 1 of 2)**

| Device | Pin Count | Number of LVDS Channels (1) |

|--------|-----------|-----------------------------|

| EP2C5  | 144       | 31 (35)                     |

|        | 208       | 56 (60)                     |

|        | 256       | 61 (65)                     |

| EP2C8  | 144       | 29 (33)                     |

|        | 208       | 53 (57)                     |

|        | 256       | 75 (79)                     |

| EP2C15 | 256       | 52 (60)                     |

|        | 484       | 128 (136)                   |

| EP2C20 | 240       | 45 (53)                     |

|        | 256       | 52 (60)                     |

|        | 484       | 128 (136)                   |

| EP2C35 | 484       | 131 (139)                   |

|        | 672       | 201 (209)                   |

| EP2C50 | 484       | 119 (127)                   |

|        | 672       | 189 (197)                   |

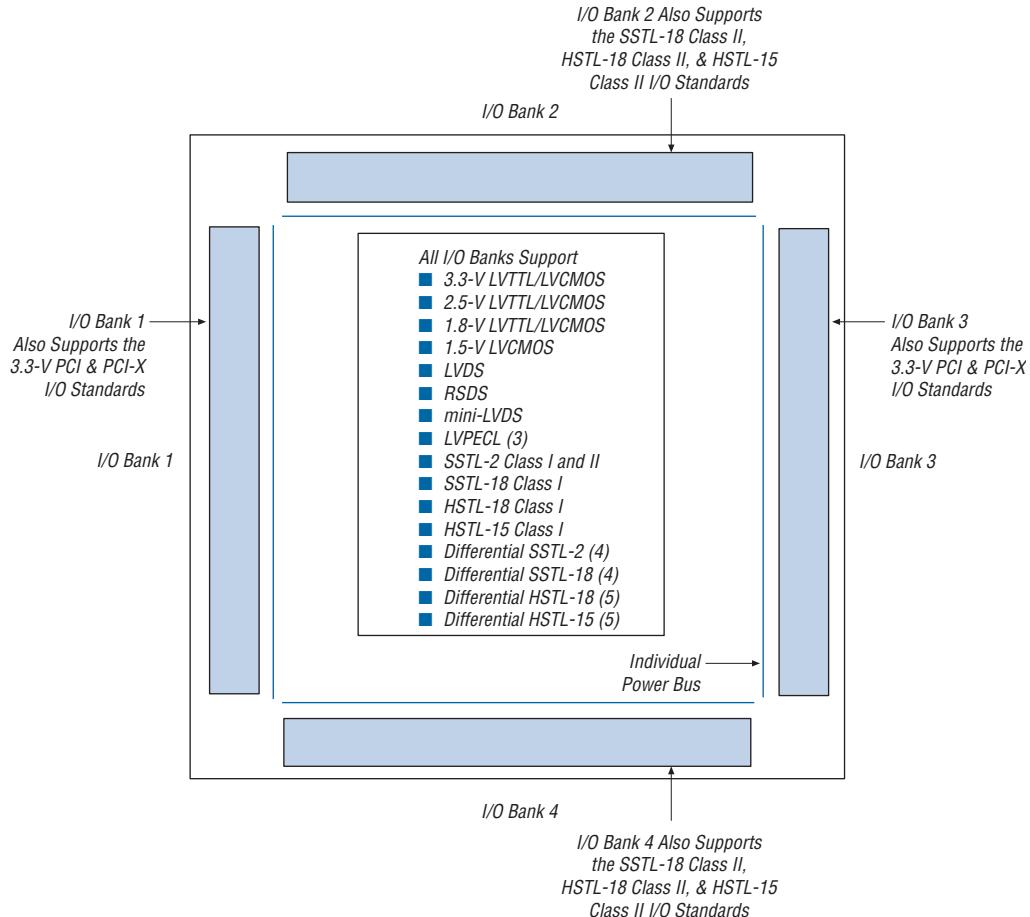

## I/O Banks

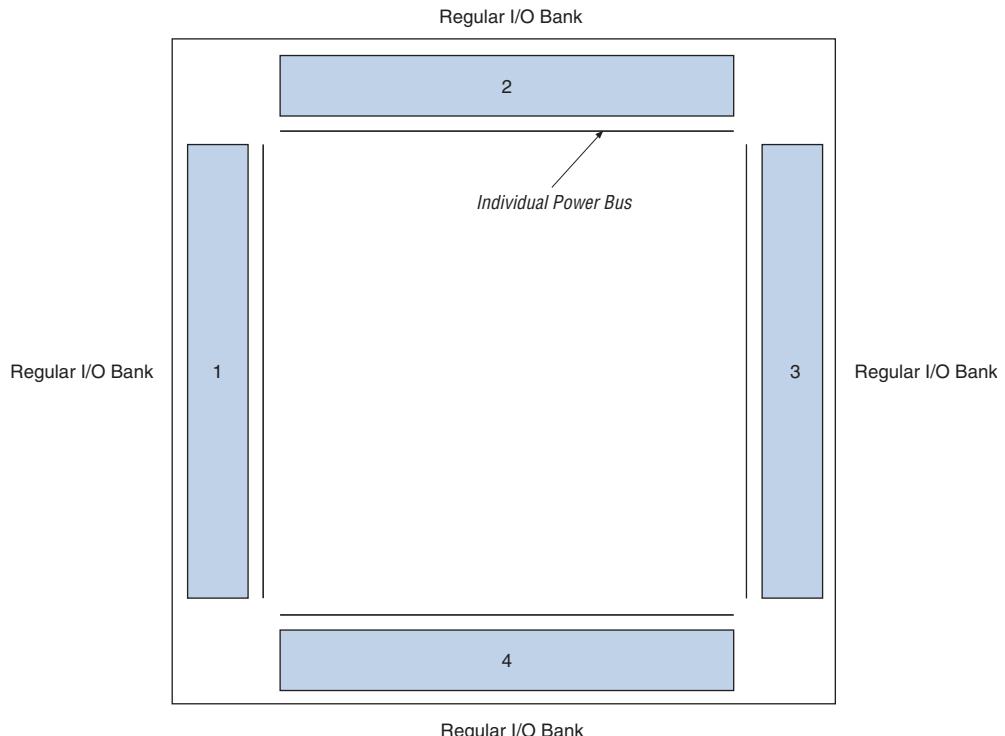

The I/O pins on Cyclone II devices are grouped together into I/O banks and each bank has a separate power bus. EP2C5 and EP2C8 devices have four I/O banks (see [Figure 2-28](#)), while EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices have eight I/O banks (see [Figure 2-29](#)).

Each device I/O pin is associated with one I/O bank. To accommodate voltage-referenced I/O standards, each Cyclone II I/O bank has a VREF bus. Each bank in EP2C5, EP2C8, EP2C15, EP2C20, EP2C35, and EP2C50 devices supports two VREF pins and each bank of EP2C70 supports four VREF pins. When using the VREF pins, each VREF pin must be properly connected to the appropriate voltage level. In the event these pins are not used as VREF pins, they may be used as regular I/O pins.

The top and bottom I/O banks (banks 2 and 4 in EP2C5 and EP2C8 devices and banks 3, 4, 7, and 8 in EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices) support all I/O standards listed in [Table 2-17](#), except the PCI/PCI-X I/O standards. The left and right side I/O banks (banks 1 and 3 in EP2C5 and EP2C8 devices and banks 1, 2, 5, and 6 in EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices) support I/O standards listed in [Table 2-17](#), except SSTL-18 class II, HSTL-18 class II, and HSTL-15 class II I/O standards. See [Table 2-17](#) for a complete list of supported I/O standards.

The top and bottom I/O banks (banks 2 and 4 in EP2C5 and EP2C8 devices and banks 3, 4, 7, and 8 in EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices) support DDR2 memory up to 167 MHz/333 Mbps and QDR memory up to 167 MHz/668 Mbps. The left and right side I/O banks (1 and 3 of EP2C5 and EP2C8 devices and 1, 2, 5, and 6 of EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices) only support SDR and DDR SDRAM interfaces. All the I/O banks of the Cyclone II devices support SDR memory up to 167 MHz/167 Mbps and DDR memory up to 167 MHz/333 Mbps.

DDR2 and QDRII interfaces may be implemented in Cyclone II side banks if the use of class II I/O standard is acceptable.

Figure 2-28. EP2C5 &amp; EP2C8 I/O Banks    Notes (1), (2)

**Notes to Figure 2-28:**

- (1) This is a top view of the silicon die.

- (2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (5) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

The Cyclone II device instruction register length is 10 bits and the USERCODE register length is 32 bits. Tables 3–2 and 3–3 show the boundary-scan register length and device IDCODE information for Cyclone II devices.

**Table 3–2. Cyclone II Boundary-Scan Register Length**

| Device | Boundary-Scan Register Length |

|--------|-------------------------------|

| EP2C5  | 498                           |

| EP2C8  | 597                           |

| EP2C15 | 969                           |

| EP2C20 | 969                           |

| EP2C35 | 1,449                         |

| EP2C50 | 1,374                         |

| EP2C70 | 1,890                         |

**Table 3–3. 32-Bit Cyclone II Device IDCODE**

| Device | IDCODE (32 Bits) (1) |                       |                                 |                 |

|--------|----------------------|-----------------------|---------------------------------|-----------------|

|        | Version (4 Bits)     | Part Number (16 Bits) | Manufacturer Identity (11 Bits) | LSB (1 Bit) (2) |

| EP2C5  | 0000                 | 0010 0000 1011 0001   | 000 0110 1110                   | 1               |

| EP2C8  | 0000                 | 0010 0000 1011 0010   | 000 0110 1110                   | 1               |

| EP2C15 | 0000                 | 0010 0000 1011 0011   | 000 0110 1110                   | 1               |

| EP2C20 | 0000                 | 0010 0000 1011 0011   | 000 0110 1110                   | 1               |

| EP2C35 | 0000                 | 0010 0000 1011 0100   | 000 0110 1110                   | 1               |

| EP2C50 | 0000                 | 0010 0000 1011 0101   | 000 0110 1110                   | 1               |

| EP2C70 | 0000                 | 0010 0000 1011 0110   | 000 0110 1110                   | 1               |

*Notes to Table 3–3:*

- (1) The most significant bit (MSB) is on the left.

- (2) The IDCODE's least significant bit (LSB) is always 1.

For more information on the Cyclone II JTAG specifications, refer to the *DC Characteristics & Timing Specifications* chapter in the *Cyclone II Device Handbook, Volume 1*.

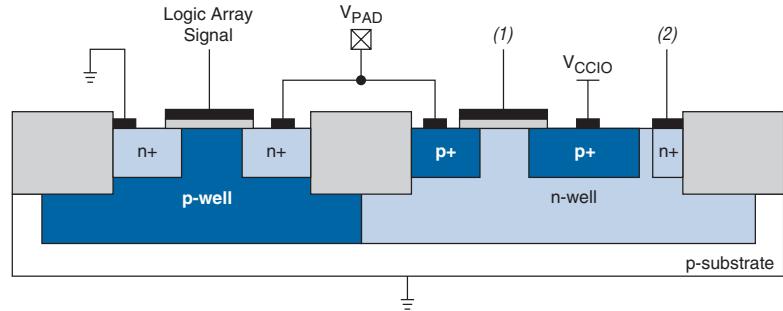

**Figure 4-2. Transistor Level Diagram of FPGA Device I/O Buffers****Notes to Figure 4-2:**

- (1) This is the logic array signal or the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

- (2) This is the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

## Power-On Reset Circuitry

Cyclone II devices contain POR circuitry to keep the device in a reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the V<sub>CCINT</sub> voltage levels and tri-states all user I/O pins until the V<sub>CC</sub> reaches the recommended operating levels. In addition, the POR circuitry also monitors the V<sub>CCIO</sub> level of the two I/O banks that contains configuration pins (I/O banks 1 and 3 for EP2C5 and EP2C8, I/O banks 2 and 6 for EP2C15A, EP2C20, EP2C35, EP2C50, and EP2C70) and tri-states all user I/O pins until the V<sub>CC</sub> reaches the recommended operating levels.

After the Cyclone II device enters user mode, the POR circuit continues to monitor the V<sub>CCINT</sub> voltage level so that a brown-out condition during user mode can be detected. If the V<sub>CCINT</sub> voltage sags below the POR trip point during user mode, the POR circuit resets the device. If the V<sub>CCIO</sub> voltage sags during user mode, the POR circuit does not reset the device.

### "Wake-up" Time for Cyclone II Devices

In some applications, it may be necessary for a device to wake up very quickly in order to begin operation. The Cyclone II device family offers the Fast-On feature to support fast wake-up time applications. Devices that support the Fast-On feature are designated with an "A" in the ordering code and have stricter power up requirements compared to non-A devices.

**Table 5–3. DC Characteristics for User I/O, Dual-Purpose, and Dedicated Pins (Part 1 of 2)**

| Symbol       | Parameter                            | Conditions                                                                                  | Minimum  | Typical | Maximum    | Unit    |

|--------------|--------------------------------------|---------------------------------------------------------------------------------------------|----------|---------|------------|---------|

| $V_{IN}$     | Input voltage                        | (1), (2)                                                                                    | -0.5     | —       | 4.0        | V       |

| $I_I$        | Input pin leakage current            | $V_{IN} = V_{CCIOmax}$ to 0 V (3)                                                           | -10      | —       | 10         | $\mu A$ |

| $V_{OUT}$    | Output voltage                       | —                                                                                           | 0        | —       | $V_{CCIO}$ | V       |

| $I_{OZ}$     | Tri-stated I/O pin leakage current   | $V_{OUT} = V_{CCIOmax}$ to 0 V (3)                                                          | -10      | —       | 10         | $\mu A$ |

| $I_{CCINT0}$ | $V_{CCINT}$ supply current (standby) | $V_{IN}$ = ground, no load, no toggling inputs<br>$T_J = 25^\circ C$<br>Nominal $V_{CCINT}$ | EP2C5/A  | —       | 0.010      | (4)     |

|              |                                      |                                                                                             | EP2C8/A  | —       | 0.017      | (4)     |

|              |                                      |                                                                                             | EP2C15A  | —       | 0.037      | (4)     |

|              |                                      |                                                                                             | EP2C20/A | —       | 0.037      | (4)     |

|              |                                      |                                                                                             | EP2C35   | —       | 0.066      | (4)     |

|              |                                      |                                                                                             | EP2C50   | —       | 0.101      | (4)     |

|              |                                      |                                                                                             | EP2C70   | —       | 0.141      | (4)     |

| $I_{CCIO0}$  | $V_{CCIO}$ supply current (standby)  | $V_{IN}$ = ground, no load, no toggling inputs<br>$T_J = 25^\circ C$<br>$V_{CCIO} = 2.5 V$  | EP2C5/A  | —       | 0.7        | (4)     |

|              |                                      |                                                                                             | EP2C8/A  | —       | 0.8        | (4)     |

|              |                                      |                                                                                             | EP2C15A  | —       | 0.9        | (4)     |

|              |                                      |                                                                                             | EP2C20/A | —       | 0.9        | (4)     |

|              |                                      |                                                                                             | EP2C35   | —       | 1.3        | (4)     |

|              |                                      |                                                                                             | EP2C50   | —       | 1.3        | (4)     |

|              |                                      |                                                                                             | EP2C70   | —       | 1.7        | (4)     |

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| <b>Table 5–14. Cyclone II Device Timing Model Status</b> |                       |                    |              |

|----------------------------------------------------------|-----------------------|--------------------|--------------|

| <b>Device</b>                                            | <b>Speed Grade</b>    | <b>Preliminary</b> | <b>Final</b> |

| EP2C5/A                                                  | Commercial/Industrial | —                  | ✓            |

|                                                          | Automotive            | ✓                  | —            |

| EP2C8/A                                                  | Commercial/Industrial | —                  | ✓            |

|                                                          | Automotive            | ✓                  | —            |

| EP2C15A                                                  | Commercial/Industrial | —                  | ✓            |

|                                                          | Automotive            | ✓                  | —            |

| EP2C20/A                                                 | Commercial/Industrial | —                  | ✓            |

|                                                          | Automotive            | ✓                  | —            |

| EP2C35                                                   | Commercial/Industrial | —                  | ✓            |

| EP2C50                                                   | Commercial/Industrial | —                  | ✓            |

| EP2C70                                                   | Commercial/Industrial | —                  | ✓            |

## Performance

Table 5–15 shows Cyclone II performance for some common designs. All performance values were obtained with Quartus II software compilation of LPM, or MegaCore functions for the FIR and FFT designs.

| <b>Table 5–15. Cyclone II Performance (Part 1 of 4)</b> |                         |                       |                          |                   |                           |                           |                           |                       |

|---------------------------------------------------------|-------------------------|-----------------------|--------------------------|-------------------|---------------------------|---------------------------|---------------------------|-----------------------|

| <b>Applications</b>                                     |                         | <b>Resources Used</b> |                          |                   | <b>Performance (MHz)</b>  |                           |                           |                       |

|                                                         |                         | <b>LEs</b>            | <b>M4K Memory Blocks</b> | <b>DSP Blocks</b> | <b>–6 Speed Grade (6)</b> | <b>–7 Speed Grade (7)</b> | <b>–7 Speed Grade (7)</b> | <b>–8 Speed Grade</b> |

| LE                                                      | 16-to-1 multiplexer (1) | 21                    | 0                        | 0                 | 385.35                    | 313.97                    | 270.85                    | 286.04                |

|                                                         | 32-to-1 multiplexer (1) | 38                    | 0                        | 0                 | 294.2                     | 260.75                    | 228.78                    | 191.02                |

|                                                         | 16-bit counter          | 16                    | 0                        | 0                 | 401.6                     | 349.4                     | 310.65                    | 310.65                |

|                                                         | 64-bit counter          | 64                    | 0                        | 0                 | 157.15                    | 137.98                    | 126.08                    | 126.27                |

## Introduction

Cyclone® II devices have up to four phase-locked loops (PLLs) that provide robust clock management and synthesis for device clock management, external system clock management, and I/O interfaces. Cyclone II PLLs are versatile and can be used as a zero delay buffer, a jitter attenuator, a low skew fan out buffer, or a frequency synthesizer.

Each Cyclone II device has up to four PLLs, supporting advanced capabilities such as clock switchover and programmable switchover. These PLLs offer clock multiplication and division, phase shifting, and programmable duty cycle and can be used to minimize clock delay and clock skew, and to reduce or adjust clock-to-out ( $t_{CO}$ ) and set-up ( $t_{SU}$ ) times.

Cyclone II devices also support a power-down mode where unused clock networks can be turned off. The Altera® Quartus® II software enables the PLLs and their features without requiring any external devices.

Cyclone II PLLs have been characterized to operate in the commercial junction temperature range (0° to 85° C), the industrial junction temperature range (-40° to 100° C) and the extended temperature range (-40° to 125° C).

Table 7-1 shows the PLLs available in each Cyclone II device.

**Table 7-1. Cyclone II Device PLL Availability**

| Device | PLL1 | PLL2 | PLL3 | PLL4 |

|--------|------|------|------|------|

| EP2C5  | ✓    | ✓    |      |      |

| EP2C8  | ✓    | ✓    |      |      |

| EP2C15 | ✓    | ✓    | ✓    | ✓    |

| EP2C20 | ✓    | ✓    | ✓    | ✓    |

| EP2C35 | ✓    | ✓    | ✓    | ✓    |

| EP2C50 | ✓    | ✓    | ✓    | ✓    |

| EP2C70 | ✓    | ✓    | ✓    | ✓    |

**Figure 7-1. Cyclone II Device PLL Locations** *Note (1)****Note to Figure 7-1:***

(1) This figure shows the PLL and clock inputs in the EP2C15 through EP2C70 devices. The EP2C5 and EP2C8 devices only have eight global clocks (CLK[0..3] and CLK[4..7]) and PLLs 1 and 2.

The main purpose of a PLL is to synchronize the phase and frequency of the VCO to an input reference clock. There are a number of components that comprise a PLL to achieve this phase alignment.

The PLL compares the rising edge of the reference input clock to a feedback clock using a phase-frequency detector (PFD). The PFD produces an up or down signal that determines whether the VCO needs to operate at a higher or lower frequency. The PFD output is applied to the charge pump and loop filter, which produces a control voltage for setting the frequency of the VCO. If the PFD transitions the up signal high, then the VCO frequency increases. If the PFD transitions the down signal high, then the VCO frequency decreases.

The VCO frequency is a critical parameter that must be between 300 and 1,000 MHz to ensure proper operation of the PLL. The Quartus II software automatically sets the VCO frequency within the recommended range based on the clock output and phase-shift requirements in your design.

## PLL Reference Clock Generation

In Cyclone II devices, up to four clock pins can drive the PLL, as shown in [Figure 7-11 on page 7-26](#). The multiplexer output feeds the PLL reference clock input. The PLL has internal delay elements that compensate for the clock delay from the input pin to the clock input port of the PLL.

[Table 7-3](#) shows the clock input pin connections to the PLLs in the Cyclone II device.

**Table 7-3. PLL Clock Input Pin Connections**

| Device | PLL 1        |              | PLL 2        |              | PLL 3        |                | PLL 4          |                |

|--------|--------------|--------------|--------------|--------------|--------------|----------------|----------------|----------------|

|        | CLK0<br>CLK1 | CLK2<br>CLK3 | CLK4<br>CLK5 | CLK6<br>CLK7 | CLK8<br>CLK9 | CLK10<br>CLK11 | CLK12<br>CLK13 | CLK14<br>CLK15 |

| EP2C5  | ✓            | ✓            | ✓            | ✓            |              |                |                |                |

| EP2C8  | ✓            | ✓            | ✓            | ✓            |              |                |                |                |

| EP2C15 | ✓            | ✓            | ✓            | ✓            | ✓            | ✓              | ✓              | ✓              |

| EP2C20 | ✓            | ✓            | ✓            | ✓            | ✓            | ✓              | ✓              | ✓              |

| EP2C35 | ✓            | ✓            | ✓            | ✓            | ✓            | ✓              | ✓              | ✓              |

| EP2C50 | ✓            | ✓            | ✓            | ✓            | ✓            | ✓              | ✓              | ✓              |

| EP2C70 | ✓            | ✓            | ✓            | ✓            | ✓            | ✓              | ✓              | ✓              |

Each PLL can be fed by one of four single-ended or two differential clock input pins. For example, PLL 1 can be fed by `CLK[3..0]` when using a single-ended I/O standard. When your design uses a differential I/O standard, these same clock pins have a secondary function as `LVDSDLK[2..1]p` and `LVDSDLK[2..1]n` pins. When using differential clocks, the `CLK0` pin's secondary function is `LVDSDLK1p`, the `CLK1` pin's secondary function is `LVDSDLK1n`, etc.

## PLL Specifications

See the *DC & Switching Characteristics* chapter in Volume 1 of the *Cyclone II Device Handbook* for information on PLL timing specifications.

### Clocking

Cyclone II devices provide up to 16 dedicated clock pins (CLK[15..0]) that can drive the global clock networks. The smaller Cyclone II devices (EP2C5 and EP2C8 devices) support four dedicated clock pins on each side (left and right) capable of driving a total of eight global clock networks, while the larger devices (EP2C15 devices and larger) support four clock pins on all four sides of the device. These clock pins can drive a total of 16 global clock networks.

Table 7-7 shows the number of global clocks available across the Cyclone II family members.

**Table 7-7. Number of Global Clocks Available in Cyclone II Devices**

| Device | Number of Global Clocks |

|--------|-------------------------|

| EP2C5  | 8                       |

| EP2C8  | 8                       |

| EP2C15 | 16                      |

| EP2C20 | 16                      |

| EP2C35 | 16                      |

| EP2C50 | 16                      |

| EP2C70 | 16                      |

### Global Clock Network

Global clocks drive throughout the entire device, feeding all device quadrants. All resources within the device (IOEs, logic array blocks (LABs), dedicated multiplier blocks, and M4K memory blocks) can use the global clock networks as clock sources. These clock network resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed by an external pin. Internal logic can also drive the global clock networks for internally generated global clocks and asynchronous clears, clock enables, or other control signals with high fan-out.

| Table 7-8. Global Clock Network Connections (Part 3 of 3) |                        |   |   |   |   |   |   |                                    |   |   |    |    |    |    |    |    |

|-----------------------------------------------------------|------------------------|---|---|---|---|---|---|------------------------------------|---|---|----|----|----|----|----|----|

| Global Clock Network Clock Sources                        | Global Clock Networks  |   |   |   |   |   |   |                                    |   |   |    |    |    |    |    |    |

|                                                           | All Cyclone II Devices |   |   |   |   |   |   | EP2C15 through EP2C70 Devices Only |   |   |    |    |    |    |    |    |

|                                                           | 0                      | 1 | 2 | 3 | 4 | 5 | 6 | 7                                  | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| DPCLK3 (1)                                                |                        |   |   |   |   |   |   |                                    |   |   |    |    |    |    |    | ✓  |

**Notes to Table 7-8:**

- (1) See the *Cyclone II Architecture* chapter in Volume 1 of the *Cyclone II Device Handbook* for more information on DPCLK pins.

- (2) This pin only applies to EP2C5 and EP2C8 devices.

- (3) These pins only apply to EP2C15 devices and larger. Only one of the two CDPCLK pins can feed the clock control block. The other pin can be used as a regular I/O pin.

If the dedicated clock pins are not used to feed the global clock networks, they can be used as general-purpose input pins to feed the logic array using the MultiTrack interconnect. However, if they are used as general-purpose input pins, they do not have support for an I/O register and must use LE-based registers in place of an I/O register.

## Clock Control Block

Every global clock network is driven by a clock control block residing either on the top, bottom, left, or right side of the Cyclone II device. The global clock network has been optimized for minimum clock skew and delay.

Table 7-9 lists the sources that can feed the clock control block, which in turn feeds the global clock networks.

| Table 7-9. Clock Control Block Inputs (Part 1 of 2) |                                                                                                                                                                                                                          |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input                                               | Description                                                                                                                                                                                                              |

| Dedicated clock inputs                              | Dedicated clock input pins can drive clocks or global signals, such as asynchronous clears, presets, or clock enables onto a given global clock network.                                                                 |

| Dual-purpose clock (DPCLK and CDPCLK) I/O inputs    | DPCLK and CDPCLK I/O pins are bidirectional dual function pins that can be used for high fan-out control signals, such as protocol signals, TRDY and IRDY signals for PCI, or DQS for DDR, via the global clock network. |

Figure 7-11. Clock Control Block

## Notes to Figure 7-11:

- (1) The CLKSWITCH signal can either be set through the configuration file or dynamically set when using the manual PLL switchover feature. The output of the multiplexer is the input reference clock ( $f_{IN}$ ) for the PLL.

- (2) The CLKSELECT[1..0] signals are fed by internal logic and can be used to dynamically select the clock source for the global clock network when the device is in user mode.

- (3) The static clock select signals are set in the configuration file and cannot be dynamically controlled when the device is in user mode.

- (4) Internal logic can be used to enable or disable the global clock network in user mode.

Each PLL generates three clock outputs through the  $c[1..0]$  and  $c2$  counters. Two of these clocks can drive the global clock network through the clock control block.

### Global Clock Network Clock Source Generation

There are a total of 8 clock control blocks on the smaller Cyclone II devices (EP2C5 and EP2C8 devices) and a total of 16 clock control blocks on the larger Cyclone II devices (EP2C15 devices and larger). [Figure 7-12](#) shows the Cyclone II clock inputs and the clock control blocks placement.

**Table 8–1. Summary of M4K Memory Features (Part 2 of 2)**

| Feature                              | M4K Blocks                                |

|--------------------------------------|-------------------------------------------|

| Packed mode                          | ✓                                         |

| Address clock enable                 | ✓                                         |

| Single-port mode                     | ✓                                         |

| Simple dual-port mode                | ✓                                         |

| True dual-port mode                  | ✓                                         |

| Embedded shift register mode (2)     | ✓                                         |

| ROM mode                             | ✓                                         |

| FIFO buffer (2)                      | ✓                                         |

| Simple dual-port mixed width support | ✓                                         |

| True dual-port mixed width support   | ✓                                         |

| Memory Initialization File (.mif)    | ✓                                         |

| Mixed-clock mode                     | ✓                                         |

| Power-up condition                   | Outputs cleared                           |

| Register clears                      | Output registers only                     |

| Same-port read-during-write          | New data available at positive clock edge |

| Mixed-port read-during-write         | Old data available at positive clock edge |

**Notes to Table 8–1:**

- (1) Maximum performance information is preliminary until device characterization.

- (2) FIFO buffers and embedded shift registers require external logic elements (LEs) for implementing control logic.

Table 8–2 shows the capacity and distribution of the M4K memory blocks in each Cyclone II device family member.

**Table 8–2. Number of M4K Blocks in Cyclone II Devices (Part 1 of 2)**

| Device | M4K Blocks | Total RAM Bits |

|--------|------------|----------------|

| EP2C5  | 26         | 119,808        |

| EP2C8  | 36         | 165,888        |

| EP2C15 | 52         | 239,616        |

| EP2C20 | 52         | 239,616        |

| EP2C35 | 105        | 483,840        |

In  $\times 8$  and  $\times 16$  modes, one DQS pin drives up to 8 or 16 DQ pins, respectively, within the group. In the  $\times 9$  and  $\times 18$  modes, a pair of DQS pins (CQ and CQ#) drives up to 9 or 18 DQ pins within the group to support one or two parity bits and the corresponding data bits. If the parity bits or any data bits are not used, the extra DQ pins can be used as regular user I/O pins. The  $\times 9$  and  $\times 18$  modes are used to support the QDRII memory interface. [Table 9–2](#) shows the number of DQS/DQ groups supported in each Cyclone II density/package combination.

**Table 9–2. Cyclone II DQS & DQ Bus Mode Support** [Note \(1\)](#)

| Device | Package               | Number of $\times 8$ Groups | Number of $\times 9$ Groups (5), (6) | Number of $\times 16$ Groups | Number of $\times 18$ Groups (5), (6) |

|--------|-----------------------|-----------------------------|--------------------------------------|------------------------------|---------------------------------------|

| EP2C5  | 144-pin TQFP (2)      | 3                           | 3                                    | 0                            | 0                                     |

|        | 208-pin PQFP          | 7 (3)                       | 4                                    | 3                            | 3                                     |

|        | 256-pin FineLine BGA  | 8 (3)                       | 4 (7)                                | 4                            | 4 (7)                                 |

| EP2C8  | 144-pin TQFP (2)      | 3                           | 3                                    | 0                            | 0                                     |

|        | 208-pin PQFP          | 7 (3)                       | 4 (7)                                | 3                            | 3                                     |

|        | 256-pin FineLine BGA® | 8 (3)                       | 4 (7)                                | 4                            | 4 (7)                                 |

| EP2C15 | 256-pin FineLine BGA  | 8                           | 4                                    | 4                            | 4                                     |

|        | 484-pin FineLine BGA  | 16 (4)                      | 8 (8)                                | 8                            | 8 (8)                                 |

| EP2C20 | 240-pin PQFP          | 8                           | 4                                    | 4                            | 4                                     |

|        | 256-pin FineLine BGA  | 8                           | 4                                    | 4                            | 4                                     |

|        | 484-pin FineLine BGA  | 16 (4)                      | 8 (8)                                | 8                            | 8 (8)                                 |

| EP2C35 | 484-pin FineLine BGA  | 16 (4)                      | 8 (8)                                | 8                            | 8 (8)                                 |

|        | 672-pin FineLine BGA  | 20 (4)                      | 8 (8)                                | 8                            | 8 (8)                                 |

| EP2C50 | 484-pin FineLine BGA  | 16 (4)                      | 8 (8)                                | 8                            | 8 (8)                                 |

|        | 672-pin FineLine BGA  | 20 (4)                      | 8 (8)                                | 8                            | 8 (8)                                 |

| EP2C70 | 672-pin FineLine BGA  | 20 (4)                      | 8 (8)                                | 8                            | 8 (8)                                 |

|        | 896-pin FineLine BGA  | 20 (4)                      | 8 (8)                                | 8                            | 8 (8)                                 |

**Notes to Table 9–2:**

- (1) Numbers are preliminary.

- (2) EP2C5 and EP2C8 devices in the 144-pin TQFP package do not have any DQ pin groups in I/O bank 1.

- (3) Because of available clock resources, only a total of 6 DQ/DQS groups can be implemented.

- (4) Because of available clock resources, only a total of 14 DQ/DQS groups can be implemented.

- (5) The  $\times 9$  DQS/DQ groups are also used as  $\times 8$  DQS/DQ groups. The  $\times 18$  DQS/DQ groups are also used as  $\times 16$  DQS/DQ groups.

- (6) For QDRII implementation, if you connect the D ports (write data) to the Cyclone II DQ pins, the total available  $\times 9$  DQS /DQ and  $\times 18$  DQS/DQ groups are half of that shown in [Table 9–2](#).

- (7) Because of available clock resources, only a total of 3 DQ/DQS groups can be implemented.

- (8) Because of available clock resources, only a total of 7 DQ/DQS groups can be implemented.

The DQS pins are listed in the Cyclone II pin tables as  $DQS[1..0]T$ ,  $DQS[1..0]B$ ,  $DQS[1..0]L$ , and  $DQS[1..0]R$  for the EP2C5 and EP2C8 devices and  $DQS[5..0]T$ ,  $DQS[5..0]B$ ,  $DQS[3..0]L$ , and  $DQS[3..0]R$  for the larger devices. The  $T$  denotes pins on the top of the device, the  $B$  denotes pins on the bottom of the device, the  $L$  denotes pins on the left of the device, and the  $R$  denotes pins on the right of the device. The corresponding DQ pins are marked as  $DQ[5..0]T[8..0]$ , where  $[5..0]$  indicates which DQS group the pins belong to.

In the Cyclone II pinouts, the DQ groups with 9 DQ pins are also used in the  $\times 8$  mode with the corresponding DQS pins, leaving the unused DQ pin available as a regular I/O pin. The DQ groups that have 18 DQ pins are also used in the  $\times 16$  mode with the corresponding DQS pins, leaving the two unused DQ pins available as regular I/O pins. For example,  $DQ1T[8..0]$  can be used in the  $\times 8$  mode, provided it is used with  $DQS1T$ . The remaining unused DQ pin,  $DQ1T8$ , is available as a regular I/O pin.

When not used as DQ or DQS pins, these pins are available as regular I/O pins. [Table 9-3](#) shows the number of DQS pins supported in each I/O bank in each Cyclone II device density.

| <b>Table 9-3. Available DQS Pins in Each I/O Bank &amp; Each Device</b> <i>Note (1)</i> |                     |                        |                      |                       |

|-----------------------------------------------------------------------------------------|---------------------|------------------------|----------------------|-----------------------|

| <b>Device</b>                                                                           | <b>Top I/O Bank</b> | <b>Bottom I/O Bank</b> | <b>Left I/O Bank</b> | <b>Right I/O Bank</b> |

| EP2C5, EP2C8                                                                            | $DQS[1..0]T$        | $DQS[1..0]B$           | $DQS[1..0]L$         | $DQS[1..0]R$          |

| EP2C15, EP2C20, EP2C35, EP2C50, EP2C70                                                  | $DQS[5..0]B$        | $DQS[5..0]T$           | $DQS[3..0]L$         | $DQS[3..0]R$          |

**Note to Table 9-3:**

(1) Numbers are preliminary.

The DQ pin numbering is based on  $\times 8/\times 9$  mode. There are up to 8 DQS/DQ groups in  $\times 8$  mode or 4 DQS/DQ groups in  $\times 9$  mode in I/O banks for EP2C5 and EP2C8. For the larger devices, there are up to 20 DQS/DQ groups in  $\times 8$  mode or 8 DQS/DQ groups in  $\times 9$  mode. Although there are up to 20 DQS/DQ groups in the  $\times 8$  mode available in the larger Cyclone II devices, but because of the available clock resources in the Cyclone II devices, only 16 DQS/DQ groups can be utilized for the external memory interface. There is a total of 16 global clock buses available for routing DQS signals but 2 of them are needed for routing the  $-90^\circ$  write clock and the system clock to the external memory devices. This reduces the global clock resources to 14 global clock buses for routing DQS signals. Incoming DQS signals are all routed to the clock control block, and are then routed to the global clock bus to clock the DDR LE registers. For EP2C5 and EP2C8 devices, the DQS signals are routed

**Table 10–2. Cyclone II 66-MHz PCI Support (Part 2 of 2)**

| Device | Package              | –6 and –7 Speed Grades |         |

|--------|----------------------|------------------------|---------|

|        |                      | 64 Bits                | 32 Bits |

| EP2C8  | 144-pin TQFP         |                        |         |

|        | 208-pin PQFP         |                        | ✓       |

|        | 256-pin FineLine BGA |                        | ✓       |

| EP2C15 | 256-pin FineLine BGA |                        | ✓       |

|        | 484-pin FineLine BGA | ✓                      | ✓       |

| EP2C20 | 240-pin PQFP         |                        | ✓       |

|        | 256-pin FineLine BGA |                        | ✓       |

|        | 484-pin FineLine BGA | ✓                      | ✓       |

| EP2C35 | 484-pin FineLine BGA | ✓                      | ✓       |

|        | 672-pin FineLine BGA | ✓                      | ✓       |

| EP2C50 | 484-pin FineLine BGA | ✓                      | ✓       |

|        | 672-pin FineLine BGA | ✓                      | ✓       |

| EP2C70 | 672-pin FineLine BGA | ✓                      | ✓       |

|        | 896-pin FineLine BGA | ✓                      | ✓       |

Table 10–3 lists the specific Cyclone II devices that support 64-bit and 32-bit PCI at 33 MHz.

**Table 10–3. Cyclone II 33-MHz PCI Support (Part 1 of 2)**

| Device | Package              | –6, –7 and –8 Speed Grades |         |

|--------|----------------------|----------------------------|---------|

|        |                      | 64 Bits                    | 32 Bits |

| EP2C5  | 144-pin TQFP         | —                          | —       |

|        | 208-pin PQFP         | —                          | ✓       |

|        | 256-pin FineLine BGA | —                          | ✓       |

| EP2C8  | 144-pin TQFP         | —                          | —       |

|        | 208-pin PQFP         | —                          | ✓       |

|        | 256-pin FineLine BGA | —                          | ✓       |

| EP2C15 | 256-pin FineLine BGA | —                          | ✓       |

|        | 484-pin FineLine BGA | ✓                          | ✓       |

Figure 10-18. LVPECL AC Coupled Termination

## Cyclone II I/O Banks

The I/O pins on Cyclone II devices are grouped together into I/O banks, and each bank has a separate power bus. This allows you to select the preferred I/O standard for a given bank, enabling tremendous flexibility in the Cyclone II device's I/O support.

EP2C5 and EP2C8 devices support four I/O banks. EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices support eight I/O banks. Each device I/O pin is associated with one of these specific, numbered I/O banks (refer to Figures 10-19 and 10-20). To accommodate voltage-referenced I/O standards, each Cyclone II I/O bank has separate  $V_{REF}$  bus. Each bank in EP2C5, EP2C8, EP2C15, EP2C20, EP2C35, and EP2C50 devices supports two  $V_{REF}$  pins and each bank in EP2C70 devices supports four  $V_{REF}$  pins. In the event these pins are not used as  $V_{REF}$  pins, they may be used as regular I/O pins. However, they are expected to have slightly higher pin capacitance than other user I/O pins when used with regular user I/O pins.

**Figure 10–19. EP2C5 and EP2C8 Device I/O Banks** *Notes (1), (2)***Notes to Figure 10–19:**

- (1) This is a top view of the silicon die.

- (2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

**Table 10–5. Cyclone II Regular I/O Standards Support**

| I/O Standard                   | I/O Banks for EP2C15, EP2C20, EP2C35, EP2C50 and EP2C70 Devices |     |     |     |     |     |     |     | I/O Banks for EP2C5 and EP2C8 Devices |     |     |     |

|--------------------------------|-----------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|---------------------------------------|-----|-----|-----|

|                                | 1                                                               | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 1                                     | 2   | 3   | 4   |

| LVTTL                          | ✓                                                               | ✓   | ✓   | ✓   | ✓   | ✓   | ✓   | ✓   | ✓                                     | ✓   | ✓   | ✓   |

| LVCMS                          | ✓                                                               | ✓   | ✓   | ✓   | ✓   | ✓   | ✓   | ✓   | ✓                                     | ✓   | ✓   | ✓   |

| 2.5 V                          | ✓                                                               | ✓   | ✓   | ✓   | ✓   | ✓   | ✓   | ✓   | ✓                                     | ✓   | ✓   | ✓   |

| 1.8 V                          | ✓                                                               | ✓   | ✓   | ✓   | ✓   | ✓   | ✓   | ✓   | ✓                                     | ✓   | ✓   | ✓   |

| 1.5 V                          | ✓                                                               | ✓   | ✓   | ✓   | ✓   | ✓   | ✓   | ✓   | ✓                                     | ✓   | ✓   | ✓   |

| 3.3-V PCI                      | ✓                                                               | ✓   | —   | —   | ✓   | ✓   | —   | —   | ✓                                     | —   | ✓   | —   |

| 3.3-V PCI-X                    | ✓                                                               | ✓   | —   | —   | ✓   | ✓   | —   | —   | ✓                                     | —   | ✓   | —   |